Сумматор

.docxМИНОБРНАУКИ РОССИИ

Федеральное государственное образовательное учреждение высшего образования

“Юго–Западный государственный университет”

Кафедра Информационной безопасности

ПРАКТИЧЕСКИЕ РАБОТЫ №1-4

по дискретной математике

Выполнил: студент группы ИБ-11б

Гребенникова А.И.

Проверил Шевелев С.С.

Курск 2022 г.

Задача: спроектировать схему 5-разрядного сумматора.

Теоретическая часть.

Сумматор — логический операционный узел, выполняющий арифметическое сложение двоичных, троичных или n-ичных кодов. Может складывать два (бинарный), три (тернарный) или n чисел (n-арный). Помимо сложения выполняются и другие операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное.

Сумматоры выполняют арифметическое сложение чисел. Они являются ядром арифметико-логических устройств, входящих в состав процессоров. В противовес сумматорам могут быть реализованы вычитатели, однако это никогда не делается, так как вычитание удобно реализовать через сложение с применением дополнительных и обратных кодов.

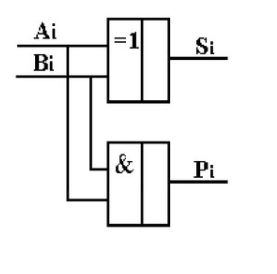

Сумматором называется устройство, предназначенное для выполнения операции сложения над многоразрядными числами. Многоразрядный сумматор состоит из одноразрядных сумматоров. Одноразрядный сумматор, на входы которого поступают два одноразрядных числа А и В, а на выходах формируются одноразрядные числа суммы S и переноса P называется полусумматором.

Сумматоры можно разделить на следующие группы:

- одноразрядный полный сумматор, как основа всех сумматоров;

- сумматор для последовательных операндов;

- многоразрядный сумматор для параллельных операндов:

- с последовательным переносом;

- с параллельным переносом;

- с групповой структурой;

- накапливающий или аккумулятор.

Рисунок 1. Полусумматор.

Рисунок 2. Быстродействующий полный сумматор.

По числу входов и выходов одноразрядных двоичных сумматоров различают:

- четвертьсумматоры (элементы "сумма по модулю 2", то есть "исключающее ИЛИ"), имеют два входа для двух одноразрядных чисел и одним выходом, на котором реализуется их арифметическая сумма;

- полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом - перенос в следующий (более старший разряд);

- полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего )разряда и двумя выходами:

на одном реализуется арифметическая сумма в данном разряде,

а на другом - перенос в следующий (более старший разряд).

Таблица

1. Таблица истинности полного сумматора.

Входы |

Выходы |

||||

Ai |

Bi |

Pi-1 |

Si |

Pi |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

|

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

- последовательные, в которых обработка чисел ведётся поочерёдно, разряд за разрядом на одном и том же оборудовании;

- параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

Параллельный сумматор в простейшем случае представляет собой n одноразрядных сумматоров, последовательно соединённых цепями переноса.

По способу выполнения операции сложения выделяются два типа сумматоров:

- комбинационный сумматор, выполняющий микрооперацию "S=A+B", в котором результат выдаётся по мере его образования;

- накапливающий сумматор, на вход которого операнды подаются

последовательно с некоторой задержкой.

Если дискретные устройства выполнены не из контактов, а из некоторых базовых дискретных устройств, то про такие устройства говорят, что они - схемы из функциональных элементов, а сами базовые дискретные устройства называют функциональными элементами.

В качестве функциональных элементов обычно берут такие устройства, для которых их булевы функции образуют базис в классе всех булевых функции. В этом случае из таких функциональных элементов можно получить схемы любых дискретных устройств, моделируемых булевыми функциями.

Одноразрядный двоичный сумматор - это дискретное устройство является центральным в компьютерной технике. Успех создания такого сумматора в середине XX в. позволил главным теоретикам создания первых электронных вычислительных машин в США Джону Фон Нейману, а чуть позже в СССР академику Сергею Алексеевичу Лебедеву успешно завершить это грандиозное дело.

Отметим, что числа в компьютере записываются в двоичном счислении и все арифметические действия над числами сводятся только к суммированию. Суммирование п -разрядных двоичных чисел производится поразрядно от младшего разряда к следующему старшему. При этом каждый раз вычисляется признак переноса единицы в старший разряд. Так же как при сложении столбиком в десятичной записи чисел. Такой одноразрядный сумматор производит сложение двух бинарных чисел Ai,Bi и учитывает еще перенос из предыдущего разряда. На выходе одноразрядного сумматора выдается сумма Ai+Bj+Pj=Si и еще вычисляется перенос Pм в следующий разряд.

Если надо перейти к функциональным элементам стандартного базиса, то надо заменить каждый одноразрядный сумматор его схемой. При этом р = 0. Если значение ри+| = 1, то это сигнал о переполнении сумматора. Важно, что каждый очередной одноразрядный сумматор вступает в работу только после окончания работы предыдущего одноразрядного сумматора, который вырабатывает перенос. Этот элемент запирает каждый одноразрядный сумматор до тех пор, пока не закончилось суммирование в предыдущем разряде. Синхронизация этого процесса характеризуется тактовой частотой процессора. Быстродействие компьютера зависит от тактовой частоты процессора и от величины разрядности сумматора.

В двоичной арифметике вычитание можно заменить сложением, используя следующие приемы:

при записи отрицательных чисел в обратном коде можно инвертировать вычитаемое и прибавить его к уменьшаемому. Если при сложении отрицательных чисел в старшем разряде возникает перенос, то бит переноса необходимо прибавить к младшему биту суммы.

при записи отрицательных чисел в дополнительном коде необходимо постоянно прибавлять 1 к младшему разряду суммы.

Вычитатель в дополнительных кодах строится на обычном сумматоре с аппаратным получением кода второго дополнения. Процесс двоичного вычитания с использованием обычного сумматора и с аппаратным получением кода второго дополнения описан ниже. При вычитании на обычном сумматоре для второго операнда используется стандартная запись второго дополнения (дополнительный код). Чтобы получить первое дополнение, второй операнд инвертируется. Чтобы получить второе дополнение, к инверсии второго операнда добавляется единица, используя вход переноса.

Проверка работы сумматора.

Подадим на входы сумматора два числа.

Пусть А = -14, B = 10.

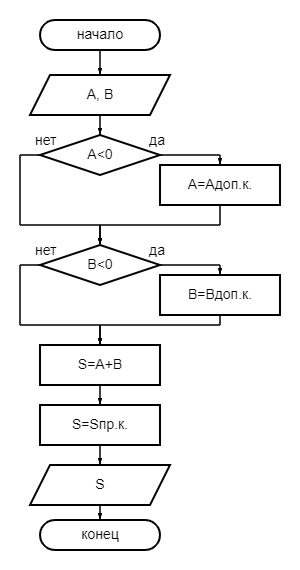

Алгоритм сложения двух чисел:

1. Переведём оба числа в двоичную систему счисления.

-1410 = 1.11102

1010 = 0.10102

2. Если какое-то число отрицательное, то переведём его в дополнительный двоичный код. В моём случае отрицательным числом является А.

-1410 = 1.1110пр.к. = 1.0010доп.к.

3. Складываем числа в двоичной системе счисления. Если числа были переведены в дополнительный код, то используем его, а не прямой. В таком случае сумма так же получится в дополнительном коде.

0.10102 + 1.0010доп.к. = 1.1100 доп.к.

4. Если сумма записана в дополнительном коде, то переводим обратно в прямой двоичный код и только после этого в десятичную систему счисления.

1.1100 доп.к. = 1.0100пр.к. = -410

Рисунок 3. Алгоритм сложения двух чисел с помощью дополнительного кода.

На входы сумматора подаём прямой двоичный код, если число положительное, и обратный, если число отрицательное. Старший знаковый разряд остаётся неизменным. (0 = «+»; 1 = «-»)

Рисунок 4. Сложение чисел A и B на сумматоре.

Как видно на скриншоте, сумма совпадает с полученной. Проведём аналогичную проверку для других чисел и результаты занесём в таблицу.

A10 |

B10 |

Aпр.к. |

Впр.к. |

Адоп.к. |

Вдоп.к. |

Sдоп.к. |

Sпр.к. |

S10 |

-14 |

10 |

1.1110 |

0.1010 |

1.0010 |

0.1010 |

1.1100 |

1.0100 |

-4 |

12 |

-10 |

0.1100 |

1.1010 |

0.1100 |

1.0110 |

0.1110 |

0.0010 |

2 |

9 |

5 |

0.1001 |

0.0101 |

0.1001 |

0.0101 |

0.1110 |

0.1110 |

14 |

-5 |

-4 |

1.0101 |

1.0100 |

1.1011 |

1.1100 |

1.0111 |

1.1001 |

-9 |

В результате проверки можно сделать вывод, что сумматор работает исправно. Задача выполнена.

Вывод: В ходе работы мы изучили принципы работы сумматоров и полусумматоров, спроектировали схему 5-разрядного сумматора и выполнили его проверку.

Литература:

1. В.И. Карлащук. Электронная лаборатория на IBM PC.

М., "СОЛОН-Р", 2001.

2. Электротехника и электроника в экспериментах и упражнениях:

Практикум на Electronics Workbench: В 2-х томах /Под общей

редакцией Д.И.Панфилова. М.: ДОДЭКА,2000.

3. Потёмкин И.С. Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат, 1988. - 320 с.

4. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учебное пособие

для втузов. - СПб.: Политехника, 1996. - 885 с.

5. Савельев А.Я. Арифметические и логические основы цифровых автоматов: Учебник. - М.: Высшая школа, 1980.-255 с.

6. Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ - Санкт-Петербург, 2000 - 528 с.: ил.