- •Реферат

- •Содержание

- •Введение

- •1 Выбор и обоснование требований и

- •Технические требования к передатчику

- •1.2 Разработка структурной и функциональной схем передатчика

- •2 Выбор обоснование и энергетический

- •2.1 Оконечный каскад

- •2.2 Усилитель мощности

- •2.3 Синтезатор частоты

- •2.4 Автогенератор

- •3 Разработка схемы контроля и защиты

- •4 Расчет кпд передатчика

- •Заключение

- •Список литературных источников

- •Приложение

2.3 Синтезатор частоты

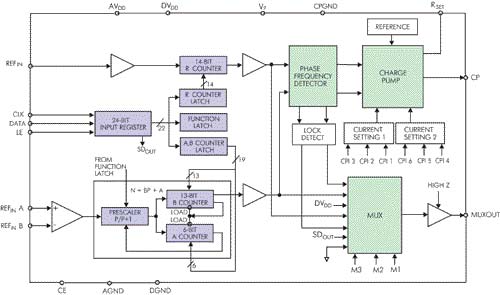

Синтезатор частоты выполнен на микросхеме ADF4110 компании ANALOG DEVICES, которая представляется собой схему простого (однопетлевого) синтезатора частоты. Функциональная схема синтезатора частоты приведена на рисунке 2.4.

Рисунок 2.4 – Функциональная схема ФАПЧ-синтезатора ADF4110

Микросхема рассчитана на максимальную входную частоту 550 МГц, работает от источника питания в диапазоне от 2,7 до 5,5 В и при необходимости может быть переведена в режим пониженного энергопотребления (программно или аппаратно). Имеет в своем составе программируемый опорный делитель, двухмодульный прескалер с коэффициентом 8/9, 16/17, 32/33, 64/65, а также содержит функции программирования источника тока и антилюфтового широкого импульса (antibacklash pulse width). Программирование производится по трехпроводному последовательному интерфейсу.

На вход REFIN подается сигнал частоты от внешнего генератора, который через входной буфер поступает на вход 14-разрядного опорного делителя (14-BIT R COUNTER) с коэффициентом деления от 1 до 16383. Биты в счетчике-защелке (R COUNTER LATCH) устанавливают коэффициент деления опорного делителя.

REFIN – это КМОП-вход с номинальным порогом VDD/2 и эквивалентным входным сопротивлением 100 кОм. Этот вход блокируется, когда инициирован режим пониженного энергопотребления Power-Down.

Входы REFINA и REFINВ являются входами (прямым и дополнительным, соответственно) входного радиочастотного каскада. Он представляет собой двухкаскадный усилитель-ограничитель формирующий CML (Current Mode Logic) синхронизирующие уровни, необходимые для нормального функционирования прескалера.

На вход REFINA обычно подается сигнал от генератора управляемого напряжением (в нашем случае VCO 190-902T). Дополнительный вход REFINВ, как правило, блокируется на землю через конденсатор емкостью 100 пФ.

CLK является входом синхронизации последовательности данных, поступающих со входа DATA. Загрузка последовательности данных DATA производится, начиная со старшего бита (MSB) и заканчивается двумя младшими контрольными битами. Каждый бит записывается в 24-разрядный входной регистр сдвига (24-BIT INPUT REGISTER) по положительному фронту импульса CLK. CLK – это КМОП-вход с высоким полный входным сопротивлением.

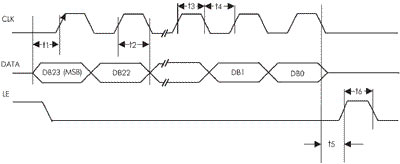

LE – это КМОП-вход разрешения загрузки. В течении всего времени загрузки данных в 24-разрядный входной регистр, уровень на это входе должен быть низким. По окончании загрузки данных, после фиксации последнего (младшего) бита, когда уровень на этом входе принимает высокое состояние, данные из входного регистра загружаются в одну из четырех защелок (LATCH). На рисунке 2.5 показан упрощенный формат загрузки данных в 24-разрядный входной регистр сдвига. В таблицах 2.1 и 2.2 приведен формат регистров-защелок, используемых для программирования различных режимов ADF4110. Биты C2, C1 (DB1, DB0) используются для выбора защелки.

Таблица 2.1 – Формат защелки опорного делителя

Reserved |

DLY |

SYNC |

Lock detect precision |

Test mode bits |

Anti-backlash |

14-bit reference counter, R |

Control bits |

|||||||||||||||||||

DB23 |

DB22 |

DB21 |

DB20 |

DB19 |

DB18 |

DB17 |

DB16 |

DB15 |

DB14 |

DB13 |

DB12 |

DB11 |

DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

|||

X* |

DLY |

SYNC |

LDP |

T2 |

T1 |

ABP2 |

ABP1 |

R14 |

R13 |

R12 |

R11 |

R10 |

R9 |

R8 |

R7 |

R6 |

R5 |

R4 |

R3 |

R2 |

R1 |

C2 |

C1 |

|||

Таблица 2.2 – Формат защелки N-делителя

Reserved |

CP Gain |

13-bit B counter |

6-bit A counter |

Control bits |

|||||||||||||||||||||||

DB23 |

DB22 |

DB21 |

DB20 |

DB19 |

DB18 |

DB17 |

DB16 |

DB15 |

DB14 |

DB13 |

DB12 |

DB11 |

DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

||||

X* |

X |

G1 |

B13 |

B12 |

B11 |

B10 |

B9 |

B8 |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

C2 |

C1 |

||||

Рисунок 2.5 – Упрощенный формат загрузки последовательности данных

На рисунке 2.5 обозначены:

t1 – минимальное время с момента появления бита данных до начала трактирования этого бита фронтом импульса CLK (не менее 10 нс);

t2 – минимальное время, в течение которого бит данных должен присутствовать после появления импульса CLK (его фронта) для его надежной фиксации (не менее 10 нс);

t3 – минимальная длительность высокого уровня CLK-импульса (не менее 25 нс);

t4 – минимальная длительность низкого уровня CLK-импульса (не менее 25 нс);

t5 – минимальное время, которое должно пройти после фиксации последнего бита до начала загрузки данных из регистра сдвига в одну из защелок (не менее 10 нс);

t6 – минимальное время, в течение которого на входе LE должен быть установлен высокий уровень, необходимый для выбора защелки и записи данных в эту защелку (не менее 20 нс). Обычно это минимальное время между последующими загрузками данных.

CE – это вход выбора микросхемы. При высоком уровне на этом входе разрешается работа микросхемы. Логический низкий уровень на этом входе переводит устройство в режим Power-Down, а выход источника тока – в режим третьего состояния.

RSET - вход установки максимального выходного тока источника. Резистор, включенный между этим входом и выводом CPGND (земля источника тока), устанавливает максимальный выходной ток источника тока. Номинальный потенциал напряжения на этом входе должен быть порядка 0,56 В. Взаимосвязь между выходным током и номиналом используемого резистора выражается отношением:

Так, при использовании резистора номиналом 2,7 кОм максимальный выходной ток источника тока будет равен 8,7 мА.

CP – выход источника тока. Когда выход разрешен, сигнал управления через внешний фильтр нижних частот поступает на вход VCO. Как уже говорилось ранее, этот выход может принимать третье состояние в различных режимах функционирования ИМС.

MUXOUT – выход мультиплексора, позволяет коммутировать на выход различные внутренние сигналы микросхемы. Состояние выхода контролируется битами М3, М2 и М1 в функциональной защелке (FUNCTION LATCH). Этот выход также может принимать третье состояние.

Входы AVDD и AGND являются входами аналогового источника питания (аналоговой части микросхемы) и аналоговой земли, соответственно. Значение источника питания AVDD должны быть в диапазоне от 2,7 до 5,5 В.

Входы DVDD и DGND являются входами цифрового источника питания (цифровой части микросхемы) и цифровой земли, соответственно. Значение источника питания DVDD должны быть в диапазоне от 2,7 до 5,5 В.

По сути, значения источников питания AVDD и DVDD должны быть равны, и на практике, как правило, они соединены между собой, и питание на эти части микросхемы подается от общего для них источника питания VDD. Здесь необходимо сделать важное замечание относительно конденсаторов развязки, которые ставятся в цепях этих источников питания.

Они (как впрочем и другие компоненты высокочастотных схем) должны быть расположены (припаяны) своими выводами к поверхности платы настолько близко, насколько это возможно, т.е. должны иметь минимально возможную длину выводов. Важно также отметить, что площадь заземляющей поверхности должна быть как можно больше и как можно лучшего качества. Аналоговая земля AGND и цифровая земля DGND на практике также соединяются между собой и представляют общую для этих источников питания землю GND.

VР и CPGND – вход питания и земля источника тока. Значение этого источника питания должно быть больше ли равно VDD. В системах, где значение VDD равно 3 В, значение VР может быть равно 6 В и использоваться для управления VCO с диапазоном настройки до 6 В. На этот вход подается напряжение от отдельного источника питания, хотя земли CPGND может быть соединена с общей землей GND.

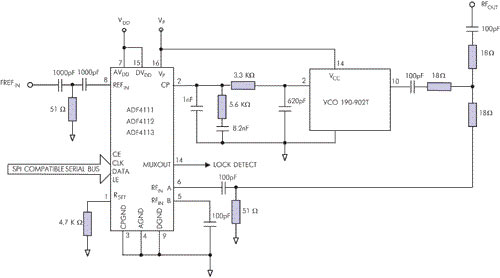

Рисунок 2.6 – Схема ФАПЧ-синтезатора частоты