- •Логические элементы и микросхемы

- •Логические элементы и микросхемы

- •Логические элементы и микросхемы

- •Логические элементы и микросхемы

- •Логические элементы и микросхемы

- •Логические элементы и микросхемы

- •Логические элементы и микросхемы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

- •Интегральные логические элементы

Интегральные логические элементы

•По схемотехническому построению современные ИЛЭ подразделяются на следующие основные типы:

элементы транзисторно-транзисторной логики (ТТЛ);элементы транзисторно-транзисторной логики с диодами Шоттки (ТТЛШ);элементы на МОП-транзисторах с каналом n-типа (n-МОП);

элементы на комплементарных МОП-транзисторах (КМОП) и другие.

•Основные параметры интегральных логических элементов

•Все логические элементы характеризуются определенным набором параметров, приводимых в справочной литературе. Наиболее важными параметрами являются следующие.

•Напряжение источника питания зависит от типа ИМС. Например, для микросхем ТТЛ и ТТЛШ напряжение питания равно 5 В. У элементов КМОП-логики напряжение питания может меняться в широких пределах: от 1,8 В до 15 В.

•Напряжения логических нуля и единицы также зависят от типа микросхем. Для ТТЛ элементов напряжение логического нуля Uвх0 = 0.8 B, Uвых0 = 0.4 B, а напряжение логической единицы Uвх1 = 2 B, Uвых1 = 2.4 B.

•Выход КМОП-элемента представляет открытый полевой транзистор, подключенный к земле либо к шине питания. Поэтому высокий уровень выходного напряжения таких элементов меньше напряжения питания на 10–20 мВ, а низкий – близок к нулю.

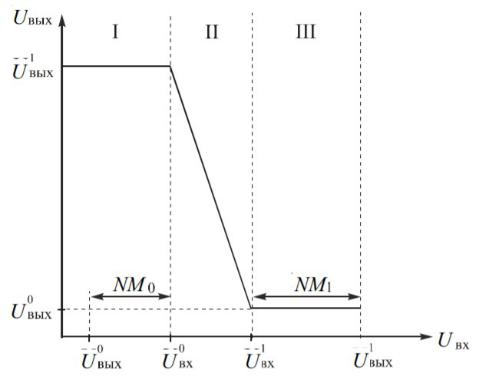

•Помехоустойчивость. В реальных условиях логический элемент находится под воздействием помех, поэтому важно, чтобы ИЛЭ не изменял своего состояния под их воздействием.

•Помехоустойчивость в состоянии логической единицы определяется формулой: NM1 =Uвых1 - Uвх1.

•Помехоустойчивость в состоянии логического нуля: NM0 =Uвх0 - Uвых0.

•Последние равенства иллюстрирует рисунок.

Интегральные логические элементы

•Потребляемая мощность является важным параметром логических элементов, входящих в состав БИС и СБИС. Она равна сумме статической Рст и динамической Рдин составляющих. Статическая составляющая определяется как среднее арифметическое мощностей, потребляемых логическим элементом в состояниях логических 0 и 1. Динамическая составляющая Рдин пропорциональна частоте f:

Pдин = fCнΔU2, где

•Cн – емкость нагрузки;

•ΔU – величина логического перепада: ΔU = Uвых1 -Uвых0.

•Мощность, потребляемая элементом ТТЛШ, реализующим функцию 2И-НЕ, составляет в зависимости от серии от 1 до 20 мВт. Например, КМОП-инвертор с длиной канала 0.25 мкм, работающий на частоте 500 мГц, потребляет мощность около 20 мкВт.

Интегральные логические элементы

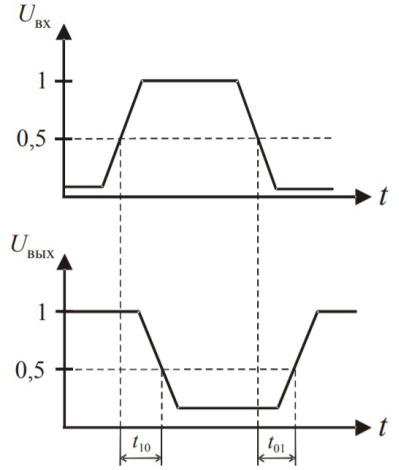

•Быстродействие логического элемента принято оценивать средним временем задержки распространения сигнала tзад. Его определяют по формуле tзад = (t01 + t10)/2.

•Здесь t01 – время задержки распространения при переключении из состояния логического нуля в состояние логической единицы; t10 – время задержки распространения при переключении из состояния логической единицы в состояние логического нуля. Время задержки распространения измеряют обычно на уровне 0.5 от полной амплитуды входного и выходного импульсов.

•Для стандартных элементов ТТЛ среднее время задержки распространения составляет около 10 нс. У элементов ТТЛШ tзад = 3 нс. Время задержки распространения КМОП-инвертора, реализованного по технологии 0.25 мкм, не превышает 30 пс.

•Нагрузочная способность цифровых ИС характеризуется коэффициентом разветвления Кразв. Он равен наибольшему числу входов ИМС той же серии, которые можно подключить к выходу рассматриваемой схемы, не нарушая ее правильного функционирования. В зависимости от типа микросхем коэффициент разветвления может изменяться от 2–3 (ТТЛ) до 30–100 и более (КМОП).

Интегральные логические элементы

•Для элементов ТТЛ-логики Кразв = 10. Входное сопротивление МОП-транзисторов практически бесконечно. Поэтому коэффициент разветвления КМОП-логических элементов может достигать 100 и более.

•Элементы транзисторно-транзисторной логики (ТТЛ).

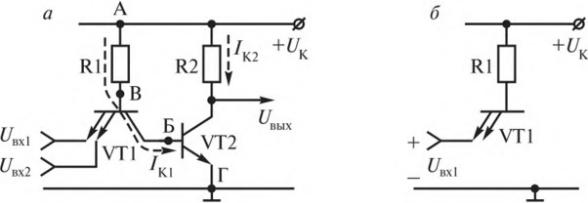

•Схема простейшего ТТЛ-элемента, реализующего операцию И-НЕ, показана на рисунке. Основная особенность схем ТТЛ заключается в том, что во входной цепи используется многоэмиттерный транзистор. Он реализует операцию И. Эмиттеры расположены таким образом, что прямое взаимодействие между ними исключается. Благодаря этому эмиттерные переходы можно рассматривать как параллельно включенные диоды. Число эмиттеров определяет число входов элемента. Инвертор реализован на транзисторе VT2.

•Таким образом, схема реализует операцию И-НЕ. Транзисторы VT1 и VT2 представляют собой однотипные n–p–n- транзисторы, поэтому их можно изготовить в едином технологическом цикле.

Предположим, что входные напряжения Uвх1 и

Uвх2 имеют высокий уровень, соответствующий

логической единице: Uвх1 = Uвх2 = +Uк . При этом

эмиттерные переходы транзистора VT1 закрыты, а

коллекторный переход открыт и VТ1 находится в инверсном режиме. Ток коллектора многоэмиттерного транзистора Iк1 втекает в базу

транзистора VT2, при этом VT2 входит в состояние насыщения. Выходное напряжение имеет низкий уровень: Uвых ≈ 0.2 В.

Если на одном из входов транзистора VT1 низкий уровень напряжения, соответствующий эмиттерный переход открыт, ток базы замыкается через него и вводит VT1 в насыщение, а VT2 - отсечки. Таблица истинности И-НЕ.

Интегральные логические элементы

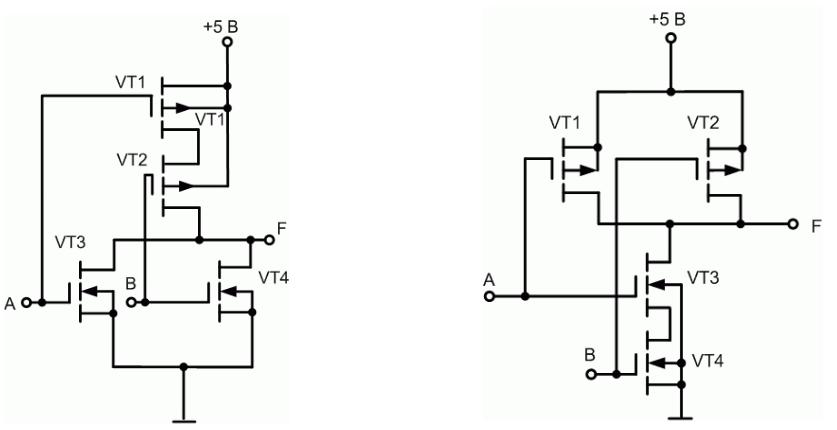

•Недостатком простейшей схемы ТТЛ-элемента является его неэкономичность. Когда транзистор VT2 находится в режиме насыщения, его коллекторный ток велик, что приводит к увеличению потребляемой мощности. Для повышения экономичности и быстродействия при сохранении нагрузочной способности в элементах ТТЛ используют сложные инверторы. Одна из стандартных схем ТТЛ-элемента, реализующая функцию 2И-НЕ, показана на рисунке.

Выходной усилитель мощности двухтактный, транзисторы VT3 и VT4 работают в противофазе, сквозной ток Iскв не протекает. Диод VD3 – для улучшения условий запирания транзистора VT3. Во всех элементах ТТЛ при отрицательном входном напряжении резко увеличивается входной ток. Для ограничения отрицательных входных напряжений

эмиттеры VT1 соединяют с корпусом через диоды VD1 и VD2, запертые для входных сигналов положительной полярности. Диоды отпираются только при действии отрицательных импульсов, возникающих при наличии помех.

Существенными недостатками ИМС ТТЛ являются:

• большие входные токи,

• высокое энергопотребление,

• невысокое быстродействие.

Интегральные логические элементы

•Элементы транзисторно-транзисторной логики на транзисторах Шоттки (ТТЛШ).

•Скорость переключения транзистора ограничивается временем рассасывания зарядов, накопленных в его базе, когда транзистор находится в насыщении. Заметно увеличить быстродействие в ТТЛ-схемах удается с помощью введения отрицательной обратной связи между коллектором и базой транзистора через диод, который предотвращает ввод транзистора в состояние насыщения. Получается ненасыщенный транзисторный ключ. Используется для этой цели диод Шоттки – полупроводниковый диод на основе барьерного перехода типа металл-полупроводник, а не p-n-перехода. Падение напряжения на диоде Шоттки при его прямом включении составляет всего 0,2—0,4 вольта. Биполярный транзистор с диодом Шоттки, включенным параллельно коллекторному переходу, носит название транзистора Шоттки. Технологически для получения такого транзистора просто наносится металлизация на коллектоный переход. Логические элементы ТТЛ, в которых все транзисторы – это транзисторы Шоттки (и диоды тоже), носят название ТТЛШ.

Быстродействие эле- ментов ТТЛШ в 3–5 раз выше, чем у аналогичных элементов ТТЛ.

Схемы ТТЛШ работают при таких же уровнях сигналов и питающих напряжений, как и обычные ТТЛ-схемы.

Интегральные логические элементы

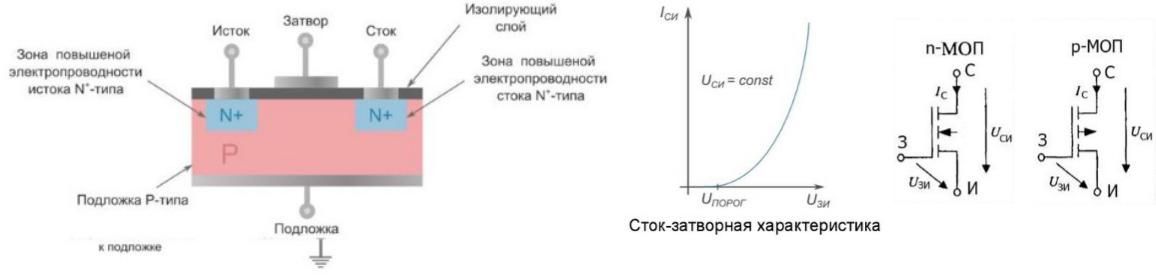

•Логические элементы n-МОП.

•МОП (металл-оксид-полупроводник) — один из видов полевого транзистора, в котором управляющий электрод (затвор) отделён от канала слоем диэлектрика, в простейшем случае, диоксида кремния. Другие названия: МДП (металл-диэлектрик- полупроводник), транзистор с изолированным затвором, англ. MOSFET. Транзисторы МОП-структуры лучше других активных полупроводниковых приборов подходили для создания логических БИС и СБИС. В отличие от биполярного транзистора, который управляется входным током, МОП-транзистор, как и другие полевые транзисторы, управляется напряжением. По причине изолированного управляющего электрода (затвора) такие транзисторы обладают очень высоким входным сопротивлением.

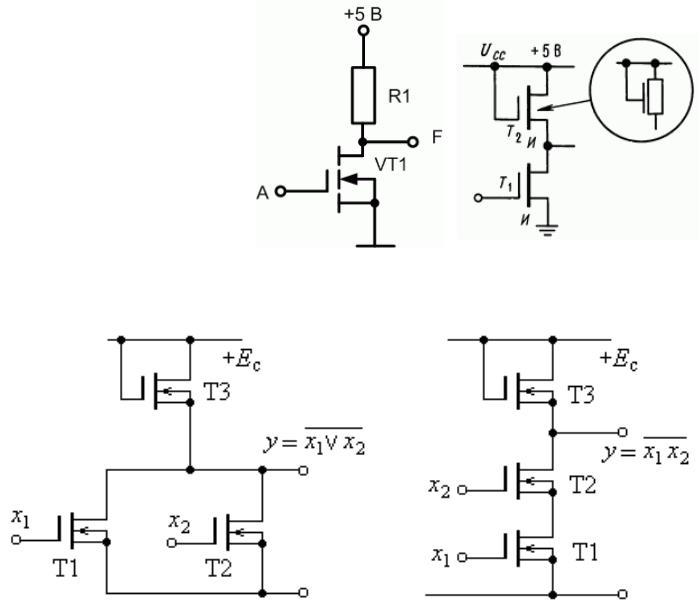

•На рисунках – транзистор n-МОП с индуцированным каналом n-типа.

Для n-канальных полевых транзисторов отпирающим является положительное (относительно истока) напряжение, приложенное к управляющему электроду (затвору) и превышающее пороговое напряжение этого транзистора. Соответственно, для p-канальных полевых транзисторов отпирающим будет являться отрицательное (относительно истока) напряжение, приложенное к управляющему электроду и превышающее его пороговое.

Интегральные логические элементы

•Базовый логический элемент n-МОП – инвертор (НЕ). Схема инвертора строится на одном транзисторе. Если напряжение на затворе транзистора

UЗИ = UA меньше порогового (низкий уровень, лог. 0), транзистор закрыт, ток стока отсутствует, выходное напряжение UF = +5 В (высокий уровень, лог. 1). Если же UA больше порогового, транзистор открыт, падение напряжение на индуцированном канале мало (высокий уровень, лог. 1), UF близко к нулю (низкий уровень, лог. 0).

•Недостаток такого инвертора – наличие в схеме резистора R1. Технология изготовления резистора в интегральном исполнении существенно отличается от технологии изготовления МОП-транзистора: резистор изготовить сложнее, и он занимает больше места на подложке. Поэтому вместо R1 применяют его эквивалент в виде МОП-транзистора: это инвертор с так называемой динамической нагрузкой.

На основе инвертора строятся элементы И-НЕ и ИЛИ-НЕ. Принцип: операция И реализуется последовательным включением транзисторов, операция ИЛИ – параллельным. Общий недостаток всех схем n-МОП, p-МОП – высокое энергопотребление в статическом режиме: когда нижние транзисторы открыты, в схеме протекает сквозной ток от источника питания на землю.

Интегральные логические элементы

•Логические элементы КМОП.

•КМОП (комплементарная структура металл-оксид-полупроводник) — набор полупроводниковых технологий построения интегральных микросхем и соответствующая ей схемотехника микросхем. Другие названия – КМДП (со структурой металл-диэлектрик-полупроводник); англ. CMOS. Подавляющее большинство современных цифровых микросхем — КМОП.

•Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (n-МОП, p-МОП) является наличие как n-, так и p-канальных полевых транзисторов в одной локации кристалла; вследствие меньшего расстояния между элементами КМОП-схемы обладают более высокой скоростью действия, однако при этом характеризуются более сложным технологическим процессом изготовления.

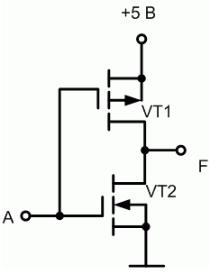

•Базовым логическим элементом является инвертор НЕ, как и в ЛЭ n-МОП.

Транзисторы с каналом p-типа подключены подложкой к источнику питания, поэтому образование канала в них будет происходить при достаточной большой разности потенциалов между подложкой и затвором, причем потенциал на затворе должен быть отрицательным относительно подложки. Такое состояние обеспечивается подачей на затвор потенциала земли (т.е. логического 0 ). Транзисторы с каналом n-типа подключены подложкой к земле, поэтому образование канала в них будет происходить при подаче на затвор потенциала источника питания (т.е. логической 1 ). Одновременная подача на такие пары транзисторов с разным типом каналов логического нуля или логической единицы приводит к тому, что один транзистор пары обязательно будет открыт, а другой закрыт. Таким образом, сквозной ток в статическом режиме не протекает.

Интегральные логические элементы

•Логическая операция ИЛИ-НЕ реализуется параллельным соединением нижних транзисторов. Каждому транзистору в нижней части схемы соответствует комплементарный транзистор в верхней части, и они соединяются последовательно.

•Логическая операция И-НЕ реализуется последовательным соединением нижних транзисторов. Верхние транзисторы соединяются параллельно.