- •Роль микропроцессорной техники в мехатронных устройствах.

- •Способы представления двоичного кода в электронных устройствах.

- •История развития микропроцессоров.

- •Основные понятия. Микропроцессор, физическая и логическая организация, архитектура.

- •Основные типы архитектур. Неймановская и гарвардская архитектура.

- •Основные понятия. Программа, команда, объектный код, мнемокод.

- •Командный цикл. Фазы командного цикла.

- •Структурная схема микро-эвм на базе микропроцессора.

- •Регистры данных микропроцессора.

- •Регистры адреса микропроцессора.

- •Специальные регистры микропроцессора. Флаги, генерируемые микропроцессором

- •Регистры общего назначения микропроцессора.

- •Счетчик команд микропроцессора. Работа счетчика команд.

- •Понятие стека, назначение и организация.

- •Указатель стека микропроцессора. Работа указателя стека.

- •Классификация микропроцессоров по числу бис в комплекте и по разрядности.

- •Классификация микропроцессоров по назначению и виду обрабатываемых сигналов.

- •Классификация микропроцессоров по характеру временной организации работы и по количеству выполняемых программ

- •Особенности программного обеспечения микропроцессорных систем. Понятие транслятора. Виды трансляторов.

- •Языки Ассемблера. Номенклатура, характеристики

- •Элементы языка ассемблера для 8-ми разрядного микропроцессора.

- •Директивы языка ассемблера. Пример программы на языке ассемблера.

- •Преимущества применения однокристальных микропроцессоров при проектировании электронных измерительных устройств.

- •Состав регистров однокристального микропроцессора к1816ве48.

- •Банки рабочих регистров микропроцессора к1816ве48. Назначение и особенности.

- •Счетчик команд, указатель стека и регистр psw микропроцессора к1816ве48.

- •Флаги признаков микропроцессора к1816ве48

- •Организация памяти микропроцессора к1816ве48. Пространство внутренней памяти данных dseg.

- •Организация памяти микропроцессора к1816ве48. Пространство внутренней памяти программ cseg.

- •Организация памяти микропроцессора к1816ве48. Пространство внешней памяти данных xseg.

- •Система ввода-вывода микропроцессора к1816ве48. Порты ввода-вывода.

- •Службы реального времени микропроцессора к1816ве48. Таймер-счетчик: организация, возможности, программирование.

- •Службы реального времени микропроцессора к1816ве48. Система прерываний от внешнего источника запросов.

- •Службы реального времени микропроцессора к1816ве48. Система прерываний от таймера.

- •Генератор тактовых импульсов микропроцессора к1816ве48.

Организация памяти микропроцессора к1816ве48. Пространство внутренней памяти программ cseg.

CSEG - пространство программного кода (до 64К байт). Программный счетчик адресует пространство памяти программ CSEG объемом до 64K байт, причем переход из области внутренней памяти программ к внешней осуществляется автоматически.

Указатель данных DPTR используется для обращения к XSEG и при Курс лекций Микропроцессорные устройства автоматики 188 пересылке констант из CSEG в A. Кроме того, содержимое DPTR используется а качестве смещения в команде перехода

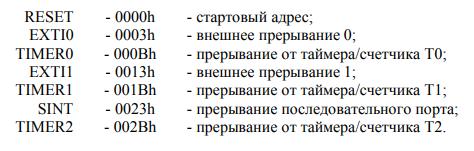

Память программ адресуется PC[15:0] и может составлять до 64К байт, причем младшие 4..8К могут располагаться непосредственно на кристалле микро-ЭВМ (РПЗУ или ПЗУ), а остальная память - внешнее ЗУ. С точки зрения программиста внешняя и внутренняя память программ представляют единое адресное пространство. Имеются “особые точки” CSEG :

Организация памяти микропроцессора к1816ве48. Пространство внешней памяти данных xseg.

XSEG - пространство внешней памяти данных (до 64К байт); Указатель данных DPTR используется для обращения к XSEG и при Курс лекций Микропроцессорные устройства автоматики 188 пересылке констант из CSEG в A. Кроме того, содержимое DPTR используется а качестве смещения в команде перехода.

Указатель стека SP образует системный стек глубиной до 256 байт. SP хранит адрес последнего занесенного байта и растет при записи в сторону больших адресов. Регистры R0, R1 каждого банка используются в качестве указателей данных. При сбросе машины в A, B, PC и DPTR загружаются 0h, а в SP<07h.

Система команд включает 111 команд - однобайтовых (49), двухбайтовых (45) и трехбайтовых (17). Все команды выполняются за 1 или 2 МЦ (12 тактов CLK), за исключением команд умножения и деления MUL и DIV, для выполнения которых требуется 4 МЦ. Большинство двухбайтовых команд - одноцикловые, а все трехбайтовые двухцикловые. За один МЦ в ВЕ52 можно вводить до двух байтов программного кода.

В микро-ЭВМ предусмотрена прямая (direct), косвенная (через R0, R1 или DPTR) и непосредственная (# data) адресация элементов DSEG и RSEG, прямая адресация элемента BSEG, косвенная (через R0, R1 или DPTR) адресация XSEG.

Система ввода-вывода микропроцессора к1816ве48. Порты ввода-вывода.

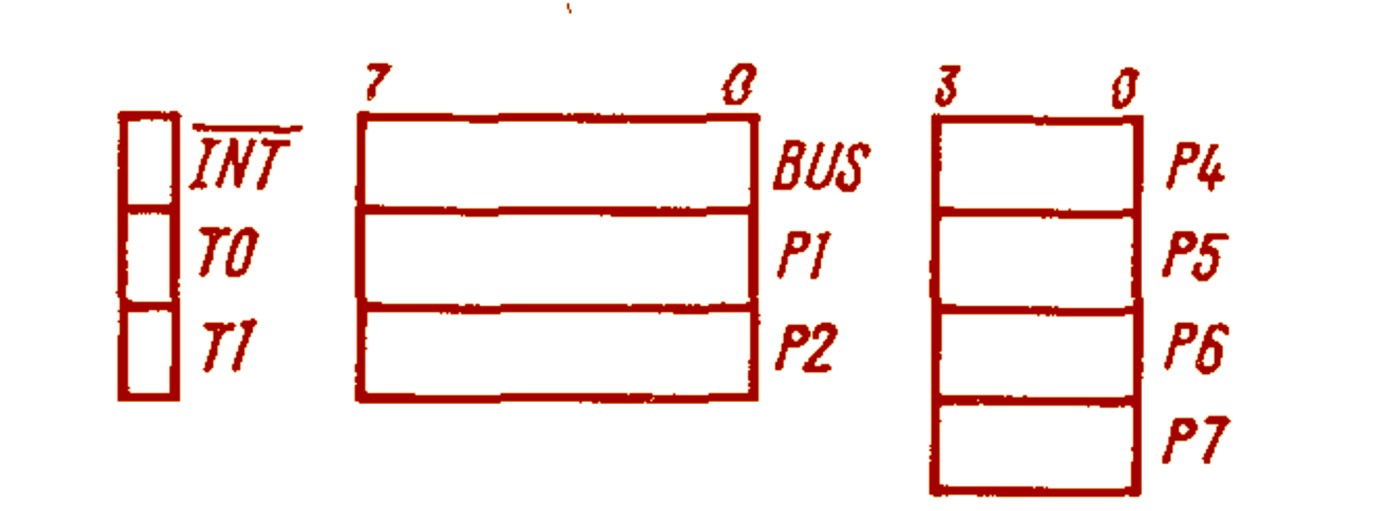

Архитектура

INTEL 8048 содержит 27 резидентных линий ВВ

(рис.), организованных в три 8- разрядных

порта BUS, PI, P2 и три тестируемые командами

условного перехода независимые линии

Т0, T1, INT.

Архитектура

INTEL 8048 содержит 27 резидентных линий ВВ

(рис.), организованных в три 8- разрядных

порта BUS, PI, P2 и три тестируемые командами

условного перехода независимые линии

Т0, T1, INT.

Порты Р1 и Р2 имеют одинаковую структурную схему (рис.) и могут быть запрограммированы либо на ввод, либо на вывод данных. Выходные буфера портов имеют встроенные регистры, которые запоминают выводимые данные. При вводе данных информация поступает непосредственно в аккумулятор, минуя выходной буферный регистр, который должен находиться в состоянии 0FFH. В противном случае выполняется операция маскирования вводимых данных по схеме «монтажное ИЛИ» с содержимым выходного регистра.

Это позволяет одни линии портов использовать для ввода, а другие – для вывода. Порт BUS отличается от Р1 и Р2 тем, что в нем применяется выходной буфер с тремя состояниями. Поэтому он не допускает одновременного смешивания ввода и вывода между своими разрядами. Расширенное пространство ВВ содержит еще четыре 4- разрядных порта Р4—Р7, реализуемые внешними средствами. В системе команд предусмотрен ряд операций с прямым доступом к этим портам. Для осуществления этой возможности разработан специальный расширитель ВВ — микросхема 8243.