- •Воронеж 2011

- •Введение

- •1. Методика ускоренного курса английского языка для проектировщиков сверхбольших интегральных схем (сбис)

- •2. Empowering design for quality of silicon

- •Vocabulary work and situations.

- •3. What is electromigration?

- •Vocabulary work and situations.

- •4. Down to the wire

- •Vocabulary work and situations.

- •Interconnect verification

- •Ir drop (power grid design)

- •5. Signal integrity closure

- •Vocabulary work and situations.

- •Appendix a: glossary for submicron and ultra-deep submicron designs

- •Appendix b:

- •Vocabulary

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

3. What is electromigration?

Class Activity

ACTIVITY 1

Introduction TEXT 1A:

Task 38. Read the passage and guess what the text is about.

Electromigration (EM), the mass transport of a metal due to the momentum transfer between conducting electrons and diffusing metal atoms, exists wherever current flows through metal wires. Discovered more than 100 years ago, EM first showed up in ICs as early as 1966 and has been a persistent problem since the early days of IC manufacturing.

When electrons flow through wires on a chip, they collide with metal atoms, producing a force on the atoms that causes the wires to break over the chip’s lifetime. When early ICs were returned from the field and examined under a microscope, very fine “cracks” in the wires were found. The immediate fix was simple: make the metal wires thicker. Making wires thicker was easy when they were 10 microns wide, but, due to the difference in aspect ratio, it’s not easy with today’s 130 nanometer and 90 nanometer technologies.

The conditions necessary for EM to be a significant problem continue to bear down on us with increasing speed and ferocity: high current densities, long narrow wires, logic hazards, and high operating frequencies. These conditions now occur on both power grids and signal lines. The transition from aluminum wires to copper wires was promoted as solving the EM problem. This is far from the case. Copper has in fact made EM analysis of chips more complex. Reduced wire size in both width and thickness and higher frequencies continue to push the envelope

of current densities wires can handle. Wire slotting and via characteristics in copper also lead to more complex design rules for EM.

More than ever, IC designers need tools that can find and help fix EM problems during the design stage before they become problems in silicon. And designers need a thorough understanding of what EM is, how it occurs, and how it affects the full-chip power and signal routing of designs.

Task 39. Organizing your thoughts:

What is Electromigration?

What happens when electrons flow through wires on a chip?

Which conditions are necessary for EM?

Why do IC designers needs tools for EM?

Task 40. Study the sentences where the following words and word combinations are used:

Average vs RMS – среднее число

joule heating – джоулевое тепло

RMS current density – среднеквадратичная текущая плотность

via – сквозное межсоединение

to dissipate – рассеивать

power grid – сетевая решетка

voltage storm – штормовое напряжение

reliability budgeting – энергетический потенциал надежности

Grammar: THE INFINITIVE |

THE FUNCTION OF INFINITIVE |

EXAMPLE |

Purpose Clause

|

To manage EM, designers first need to understand the effects of average vs. RMS current density and the effects of line widths and vias on EM |

Task 41. Read the following text carefully paying attention to the italicized words and word combinations, and try to understand the contents of the text:

BASIC TEXT 1B:

HOW TO MANAGE EM

To manage EM, designers first need to understand the effects of average vs. RMS current density and the effects of line widths and vias on EM. It is also helpful to understand the current flow in each design, how to limit current density in metal lines and contacts, and how to minimize EM without overdesigning. Any understanding of these effects and behaviors will be enhanced with the use of design tools that extract and analyze the power grid and signal lines of an entire chip.

EM is a thermally activated phenomenon based on average current density. In contrast, Joule heating is based on RMS current density. For a narrow pulse, the RMS current can be much higher than the average current. The problem with Joule heating is not only the modest temperature increase, but also the resulting temperature gradients, which can vary tremendously throughout a real structure. Therefore designers need to take a conservative approach and forbid excessive temperature gradients by limiting the RMS current density. A common location of RMS current density violations is the output of large drivers, such as clock tree or bus drivers. These nets with large distributed loads tend to have high current density in the wire segments just beyond the output of the driver.

The relationship between wire width and susceptibility to EM was often misunderstood with aluminum. A simple approach for managing EM is to reduce average current density by increasing the width of the metal lines. But blindly increasing the width of narrow wires may actually increase susceptibility to EM due to material properties of aluminum wires.

Vias conduct current from layer to layer through metal lines that are thinner than the interconnect wires, causing a local increase in current density. The number of vias used, their location, and their structure can impact current density enough to cause EM. Unless designers use verification tools that analyze these effects, EM caused by vias may not be found until after manufacturing.

Understanding, analyzing, and predicting current flow can be difficult because of the high connectivity of power grids. The most difficult aspect of power grid design is that no one block can be isolated from another. One logic block analyzed in isolation may not show any EM risk, but when viewed in a full-chip context it may show how current flowing to adjacent blocks is overloading the power connections in the analyzed block and causing EM.

Designers frequently lack information on where power is dissipating, and they typically don’t pay much attention to “local” decisions made during power grid design that may impact the overall power flow. But EM risk lurks everywhere. Logic gates with high loading can be anywhere. Power grid wires are often removed in order to complete signal routing. Large power buses designed to protect a block can result in attracting more power grid current because they offer a lower resistive path to the pins.

A complete picture of EM risk can be obtained only during full-chip physical verification. Analysis tools such as VoltageStorm show the power grid of the full chip and enable designers to see how the current flows, where it is concentrated, where it is draining, and how it can be improved.

Eliminating the last trace of EM may seem like a desirable goal, but may not be worth the extra time or design area it takes. How much time should designers spend fixing problems, and how do they prioritize the problems? When should they stop improving the design? Some design tools, such as VoltageStorm, can now help designers estimate a chip’s lifetime given its existing EM violations, and based on the estimate, determine the right time to stop working on additional EM issues. This process is known as reliability budgeting.

Task 42. Fill in the gaps with the correct variants:

1. To ….. designers ….. RMS.

a) to control b) to solve c) to manage

2. EM is a thermally activated …... based on average current density.

a) result b) solution c) phenomenon

3. A common location of RMS current ….. is the output of large drivers.

a) violations b) density c) isolation

4. ….. conduct current from layer to layer from metal lines.

a) conductor b) vias c) wires

5. Understanding, analyzing and predicting current flow can be difficult because of the high connectivity of …… grids.

a) system b) network c) power

Task 43. Match up the words with the definition.

d |

to handle, to control |

heating |

the quality of being dense |

grid |

contrary of cold |

to manage |

a plate or frame of parallel bars of wires |

Task 44. Look through the text again and find the following words in the sentences:

RMS current density

joule lucking

RMS current density

power grid

full-clip physical verification

a mean time to failure (MTTF)

Task 45. Organizing your thoughts:

What must designers know to manage EM?

Which effects of EM do you know?

What is the RMS current density?

What causes a local increase in current density?

How much time should designers spend fixing problem in EM?

When should they stop improving the design?

Task 46. Sum up the text using the following plan:

Management of EM.

Joule heating.

Current density.

Use of necessary tools to complete picture of EM.

Task 47. Skim the following text and try to understand the subject-matter

of the text.

TEXT 1C:

RELIABILITY BUDGETING

Repairing all areas of a chip that have potential EM problems is labor-intensive, time-consuming and probably unnecessary. A mean time to failure (MTTF) factor can be used to compute the probability of chip failure due to EM during the chip’s lifetime, and the power grid can be modified to decrease the probability of failure to an acceptable level.

Design rules are typically based on “worst case” scenarios that assume all wires use the highest current density limit.

This approach is too confining and results in overly conservative designs. EM failure is statistical, and typically only a few circuit elements run at the “EM limit.” Most circuit elements have little to no current flowing though them.

To perform reliability budgeting, you need to know how much current is going through each element. Tools can compute a probability of failure in time by calculating the MTTF from each circuit element and applying extreme value “links in a chain” statistics. If the probability of failure is unacceptable, designers can eliminate identified trouble spots and design a more reliable circuit.

Task 48. Find sentences with the following words.

repairing – исправление.

a mean time to failure (MTTF) – среднее время до отказа (СВДО).

chips lifetime – срок службы микросхемы.

current density – плотность тока.

links in a chain – связи в цепи

reliability budgeting – энергетический потенциал надежности

Task 49. Comprehension check.

Why is repairing labor – intensive, time-consuming and unnecessary?

What is a mean time to failure (MTTF)?

How is reliability budgeting performed?

Task 50. Match up the words with the definition.

e |

the ratio of DC voltage to DC current for a conductor |

grain boundaries |

a tiny, hard particle |

resistance |

the internal interfaces that separate neighboring misoriented single crystals in a polycrystalline solid |

density |

the mass transport of a metal due to the momentum transfer between conducting electrons and diffusing metal atoms wherever current flows through metal wires |

ACTIVITY 2

Task 51. Skim the following passage and try to understand the subject-matter of it.

TEXT 2A:

THE ROLE OF PLACE-AND-ROUTE TOOLS

Ideally, a place-and-route tool would be able to route a design to make it resistant to both signal and power grid EM. Unfortunately, most current place-and-route tools are not designed to do this.

Power grid EM issues can be solved with place-and-route tools that provide critical information such as:

1. Average switching information for each of the cells within the block being routed. This switching information would be used to estimate the average current dissipated by each cell in the design.

2. Loading information for each cell that drives an output of the block.

3. Flow of power current through the block due to how the block is oriented with respect to power pins and other blocks on the global grid.

Today’s place-and-route tools could be modified to route a block to make it resistant to signal EM if they could perform net simulation to compute the appropriate current data for each wire segment, and if they were able to access clocking information, cell driver characteristics, and information on the switching activity of every signal.

Without this information, most place-and-route tools could probably route a signal EM-resistant block, but the design would be overly conservative to accommodate the lack of critical information.

EM will not go away; it will only get worse as line widths continue to shrink and operating frequencies increase.

Until we develop new metallization schemes to erase EM or develop a room temperature superconductor, designers need to understand EM, understand the design decisions that cause EM, and manage EM using modern verification tools such as VoltageStorm and ElectronStorm analyses. Only then can designers ensure reliability while squeezing as much performance as possible out of the fabrication process.

Task 52. Comprehension check:

When would a place and route tools be able to route?

What provides critical information for power grid EM issues?

Which functions do place-and-route tools do?

How does EM help to control your design?

Task 53. Fill in the gaps with the correct variant.

A place-and-route tool would be able ….. a design to make it resistant.

a) lay b) to dissipate c) to route

Most current place-and-route ….. are not designed.

a) devices b) tools c) tasks

Loading information for each ….. that drives an output of the block.

a) case b) cell c) number

….. of power current the route the block due to how the block is oriented.

a) result b) flow c) tool

Task 54. Sum up the text using the following plan.

Role of EM in your design.

Importance of loading information for each cell of the block.

Controlling EM in your designs.

Task 55. Skim the following passage trying to understand it and give a title to it.

TEXT 2B:

From Equation 1 we see that the electromigration driving force is proportional to the current density. It could be assumed that electromigration failure would scale in the same way – linearly with the current – but that is not always the case. Traditionally, it has been observed that electromigration failure followed a 1/j2 law rather than 1/j.

This has become known as Black’s Law. In the late sixties, Jim Black of Motorola was heavily involved in understanding the “cracked stripe” problem that was later identified as electromigration. Jim's pioneering work included the first careful systematic investigations of electromigration failure kinetics. His experiments uncovered the curious behavior that electromigration failures followed kinetics that depended not on the inverse of the current density, but on the inverse square.

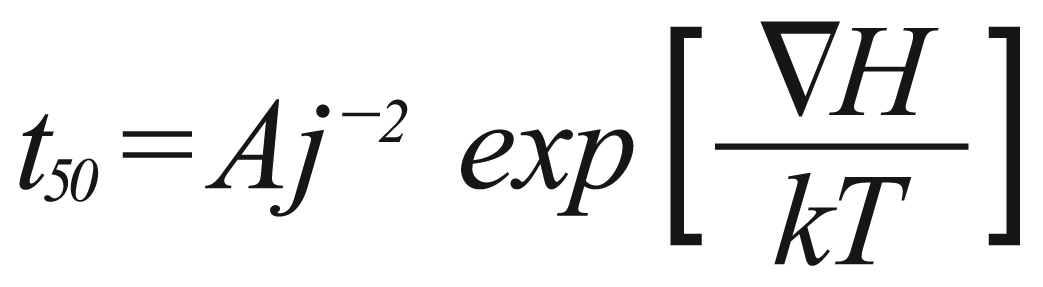

Where t50 is the median time to failure in an ensemble of samples, A is a constant that needs to be empirically determined and DH is the activation energy for failure. The experimental values found for the activation energy suggested grain boundary diffusion as the mass transport mechanism. For nucleation dominated failure, this equation has proven to be adequate even to the present day. Only small corrections, often too small to be detected experimentally have been needed to keep Black’s Law consistent with the latest theoretical developments.

Whether this empirical law holds or not depends entirely on whether the failures are nucleation or growth dominated. This, in turn, depends heavily on the process used to construct the metal lines. If there is no refractory “shunt layer” such as TiN or TiW under the Al line, failure is nucleation dominated and Black's Law holds. If, however, the failures are growth dominated, such as is usually the case for W via failure in narrow lines with shunt layers, Black's Law is not followed and failure times are dependent on 1/j kinetics. Often, as might be expected, the failure process involves both nucleation and growth of damage, and the behavior is more complicated and cannot be described by a simple power law in j.

Wherever growth dominates or is a significant part of the failure time, we assume that 1/j kinetics hold. Most recent experimental data where contacts or vias have been examined in the presence of refractory conductive shunt layers has supported the use of 1/j kinetics, whereas most data on conductor lines attached to bond pads has supported 1/j2 kinetics.

To ensure that electromigration failure does not occur in the field, we need to limit the current density such that electromigration failure will not become significant until long after the projected useful lifetime of the circuit.

This is a function of not only the current density in the metal lines and contacts, which may behave differently, but also of temperature and often process variations.

Task 56. Comprehension check.

Explain with the help of the equation the Black`s law.

When does electromigration failure take place?

Task 57. Skim the following text trying to understand the subject-matter of it.

TEXT 2C:

EFFECT OF TEMPERATURE ON CURRENT DENSITY LIMITS

The major effect of temperature on electromigration is in the diffusion coefficient. Diffusion is a thermally activated process characterized by the Arrhenius relation and it possesses an activation energy. The activation energy for self diffusion depends strongly on the diffusion mechanism. Diffusion can proceed through the lattice, or grain boundaries, and along interfaces or the surface. The lattice is the most difficult path with the highest activation energy (for Al DHlattice is about 1.4 eV), followed by the grain boundary (for Al, DHgrain boundary is about 0.6 eV ) and then the surface. In Al, the surface is generally not available due to the presence of a coherent oxide film. Interfacial diffusion activation energies differ for every interface and can be either greater or less than that for grain boundary diffusion. Adding alloying elements generally has the paradoxical effect of decreasing the lattice and increasing the grain boundary activation energies. The effect on interfaces is unclear.

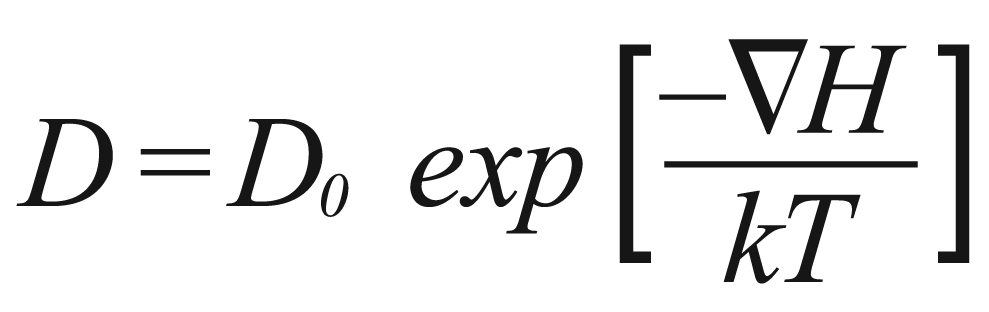

Where D0 is a pre-exponential factor that depends on the diffusion mechanism and DH is the activation energy, also dependent on the diffusion mechanism.

Equation 3 shows that electromigration is very sensitive to temperature. For Al, generally a change in temperature of 20 degrees can double the rate of electromigration. Therefore, the current permitted in a thin film conductor is a function of temperature. The higher the temperature, the less current can be permitted and still remain safe from electromigration failure.

Just how much current can be permitted and still maintain reliability as the temperature is changed will depend on whether you have nucleation or growth dominated failure and what the dominant diffusion mechanism is. If we have growth-dominated diffusion and we increase the temperature such that we double the diffusion coefficient (approximately 20 degrees for Al alloys and grain boundary diffusion), we must reduce the current density by half.

Conversely, if we want to increase the current density by a factor of two, we must ensure that the temperature is at least 20 degrees cooler. If failure is nucleation dominated, an approximate 30 % reduction in current is needed for a similar temperature increase to maintain equal reliability.

Whether failure is nucleation or growth dominated is a matter of the process used to deposit the metal and the overlying dielectric. Almost everything that happens consists of an initiation followed by a continuation.

Electromigration is no exception. First the damage must be initiated, a void nucleated or an extrusion formed, then the damage proceeds, such as void growth or continuing the extrusion, until failure occurs. Sometimes nucleation is slow and takes a long time and growth is fast. When this happens we have nucleation dominated failure. Sometimes we have the converse, and the nucleation is either very short or non-existent, and we then have growth-dominated failure. Electromigration exhibits both types of behavior.

Task 58. Comprehension check:

What is the diffusion coefficient?

What does activation energy depend upon?

What does equation 3 illustrate?

Task 59. Skim the passage and find out how the thermal heating is formed.

TEXT 2D:

RMS CURRENT AND TEMPERATURE GRADIENTS

When current is passed through a conductor, the interaction of the electrons with the lattice produces a thermal energy equal to the product of the square of the current and the resistance. This is called Joule heating. Metal lines will heat up whenever current is passed through them. If the current is low, the heat is effectively conducted away, but there must be some temperature increase even if it is not detectable. If the current density approaches 106 A/cm2, Joule heating can produce enough energy to make the conductor lines heat up appreciably. At first this does not appear to be a problem, since current densities are almost always lower than this due to limitations induced by electromigration. However, one must realize that Joule heating is caused by root mean square (RMS) current and not by the average current, as is electromigration. For a narrow pulse, the RMS current can be much higher than the average current. The average current can be well within any guidelines that may be set for electromigration considerations, yet significant Joule heating can result. This can be more prevalent on upper level metallization, where heat must be conducted through several layers of interlevel dielectric, which is a poor thermal conductor.

The problem with Joule heating is not the modest temperature increase, but the temperature gradients that result.

Typically, at the current densities found in modern circuitry, temperature increases would range between a few and a few tens of degrees Celsius. This produces temperature profiles that decay within a few microns, so that temperature gradients of 104 to 105 degrees Celsius/cm will be found. Since electromigration is thermally activated, the temperature gradients produce flux divergences that approach that found at absolute divergences such as at contacts or at microstructural features.

RMS current density must then be limited to about 2 x106 A/cm2 for lower level lines and about half that for upper level lines. Unfortunately, the reliability of metal lines in the presence of temperature gradients cannot be accurately estimated.

Temperature gradients can vary tremendously throughout a real structure, depending on subtleties of the geometry and on the use of the underlying silicon devices. The only way to deal with these issues is to take a conservative approach and forbid temperature gradients by limiting the RMS current density to the levels suggested above.

Task 60. Find the sentences with the following words:

thermal energy – тепловая энергия

joile heating – тепловая энергия

RMS Root mean equal – среднеквадратичное значение

average current – средний ток

divergence – различие

Task 61. Which of the following do you think is true or false?

1. Thermal heating passes through the conductor.

2. Joule heating does not pass electric current.

3. Temperature gradients produce flux divergences found at microstructure.

Task 62. Study the following words and word combinations in the following sentences:

Joule heating – джоулевое тепло

Temperature gradients – температурные градиенты

RMS current – среднеквадратичный ток

Task 63. Skim the text and try to get its main idea.

TEXT 2 E:

MICROSTRUCTURE AND ELECTROMIGRATION LINE WIDTH EFFECTS

Electromigration is a form of mass diffusion, where the driving force is provided by the electron flow. Therefore, things that affect diffusion will affect electromigration. Metals are composed of atomic crystals where atoms are lined up very nearly perfectly in only a few allowable configurations. The size of these crystals (“grains”) is finite.

Where the grains meet, they form a region of disorder (“grain boundary”), and provide a pathway for easy diffusion as compared to the nearly perfect metal lattices.

In the early days of ICs, the thin film conductors used in manufacturing were relatively wide, fine grained, and composed of many grains. These were referred to as polycrystalline. The grain size was about the thickness of the film, generally about one micron. Across the width of a typical conductor several microns wide, many grain boundary pathways were available to accommodate the electromigrating atoms. It came as no surprise that electromigration failure was inversely proportional to the grain size of the films: the more grain boundaries present, the more atoms that can be transported along them, and the earlier the failure time.

As line widths became smaller, the grain size of the metal films became larger. Conductor lines became comparable in width to the grain size and took on a “bamboo” like appearance where most of the grains spanned the line width, providing no continuous grain boundary pathway in the direction of the current flow. When this occurred, a peculiar effect was found: failure times were strongly dependent on line width. Narrow lines at the same current density became substantially more reliable than wider lines, as long as the grain size was uniform.

The reason for this behavior was not hard to figure out. The lack of easy grain boundary pathways meant that the atoms had to take more arduous paths such as the lattice or various interfaces in their journeys. The activation energy for failure was found to be a function of line width, since the diffusion process changed. What became even more interesting and important to reliability engineers was that the precise arrangement and orientation of the grains had a large effect on the lifetime of the conductor. In fact, as the ratio of grain size to line width increased, the reliability became poorer before it got better, and then got worse again as lines entered submicron widths.

Today, we understand this behavior and can predict the reliability from test data, grain structure, and particulars of the metal deposition process. New effects, due to the presence of refractory shunt layers and W plugs, have surfaced and have also been explained well enough that they can be tamed. However, a fundamental understanding of the process of solid state diffusion and what affects it are essential in interpreting test results. For this reason, conservative default values for parameters used in relating electromigration test data to real circuits should be employed until careful testing and data interpretation justify a change.

The choice of test structures and test conditions are of critical importance in extracting meaningful parameters to be used in interpreting the test data as it relates to actual chip performance. The wrong test or the wrong test structure can produce fatal results. The test structure must be designed to reflect the process and usually a single structure cannot.

Task 64. Give explantation of electromigration in the electron flow.

Task 65. Read the following text and try to understand the subject-matter of it.

TEXT 2F:

PHYSICS OF ELECTROMIGRATION

Electromigration is due to the momentum exchange between conducting electrons and diffusing metal atoms. Simply stated, perhaps, but how does it happen?

In a perfect lattice, there is no resistance. Electrons move about in a periodic potential with no other interaction with the metal atoms. This may sound like superconductivity, but it isn’t. The problem here is that a perfect lattice cannot exist above absolute zero due to missing atoms (“vacancies”), impurities, boundaries between crystals of different orientation (“grain boundaries”), and regions of imperfection (“dislocations”). Perhaps even more important, at any temperature above 0o K, atomic vibrations occur. These vibrations (“phonons”) put a metal atom out its of perfect position about 1013 times each second and disturb the periodic potential, causing electron scattering.

The scattering event makes the electron change direction; any change in direction is accompanied by an acceleration; and for every acceleration there is a force. After many collisions (another word for the scattering event), the force averages out in the direction of electron flow.

The force due to collisions of electrons to metal atoms is called the momentum exchange. In electromigration, momentum is exchanged between the electrons and the metal atoms and a change in momentum with time is called a force. To provide sufficient momentum exchange to cause measurable effects, many electrons must be available to collide with the atoms. This can only happen in a metal. In metals, many electrons are easily accelerated in an electric field.

Semiconductors have far fewer electrons and in a true semiconductor, electromigration does not exist because there just aren’t enough charge carriers. However, electromigration can occur in semiconductor-like materials, such as silicon, when they are so heavily doped that they act as if they were metals. At dopant levels of around 1%, electromigration has been observed in polycrystalline silicon, but then the temperature coefficient of resistance (TCR) is positive. A positive TCR is probably the best definition of a metal.

The size of the momentum exchange will be proportional to the distortion in the lattice at any given point. This distortion is greatest when there is a vacancy nearby, or in the region of a grain boundary. This is also where diffusion occurs. Vacancies or grain boundaries must be present for metal atoms to move from their fixed positions in the crystal lattice (“diffuse”). You can’t have two things in the same place at the same time, so for an atom to move from site A to site B, site B must be vacant. In grain boundaries the problem is less well defined, but the concept still applies. However, a boundary is a region of distortion and open space, and the diffusion of atoms can be accommodated in these regions rather easily as compared to the lattice. This creates a fortuitous situation where the greatest momentum exchange occurs only at the sites where it is possible for atoms to move.

For the design engineer, electromigration physics can be simply stated. Electrons flow through a metal film and collide with metal atoms. The collisions produce a force on the metal atoms in the direction of electron flow (for n-type materials, opposite for p-type materials). Electromigration is only significant at high current densities and only in metals. The magnitude of the electromigration force is proportional to the current density.

Task 66. Give a short summary of the text paying attention to the formation of line width effect in electromigration.

ACTIVITY 3

ensity

ensity lectromigration

lectromigration