- •Микропроцессорные системы. Список экзаменационных вопросов. Оглавление

- •1. Комбинационная логика, основные элементы (и, или, не), их схемы на кмоп транзисторах.

- •5. Регистры на основе d-триггеров. Параллельные регистры, последовательные (сдвиговые) регистры. Временная диаграмма работы сдвигового регистра.

- •6. Общая структура микроконтроллерного устройства, алу, программный счётчик.

- •7. Виды памяти микроконтроллеров (на примере семейства avr). Стек и его инициализация.

- •8. Прерывания, вектор прерываний.

- •9. Основы языка Assembler для микроконтроллеров семейства avr. Синтаксис, классификация команд.

- •Внешний кварцевый резонатор

- •Внешний генератор

- •12. Широтно-импульсная модуляция. Понятие широтно-импульсной модуляции. Различные режимы широтно-импульсной модуляции. Режим быстрый шим (Fast pwm). Шим без фазового сдвига (Phase Correct pwm).

- •13. Цифро-аналоговые преобразователи. Структурная схема цап. Параллельная схема суммирования токов. Последовательная схема суммирования токов.

- •15. Структурная схема встроенного аналого-цифрового преобразователя, его основные параметры. Настройка ацп, управляющие регистры. Прерывания по завершению цикла преобразования.

- •4 Режима работы spi:

- •18. Интерфейс i2c. Протокол передачи данных, режимы работы. Основные преимущества и недостатки интерфейса.

15. Структурная схема встроенного аналого-цифрового преобразователя, его основные параметры. Настройка ацп, управляющие регистры. Прерывания по завершению цикла преобразования.

Все микроконтроллеры семейства AtMega и некоторые из семейства Tiny имеют встроенный блок АЦП. Встроенный АЦП представляет собой преобразователь последовательного приближения с устройством выборки-хранения и фиксированным числом тактов преобразования, равным 13 (14 для дифференциального измерения). Данный класс АЦП занимает промежуточное положение по быстродействию, стоимости и разрешающей способности между последовательно-параллельными и сигма-дельта АЦП.

Этот АЦП десятиразрядный и многоканальный (количество каналов может варьироваться от 4 до 16 в зависимости от модели микроконтроллера).

Для выполнения первого преобразования (при первоначальной настройке АЦП) требуется 25 тактов. Тактовая частота преобразования формируется с помощью делителя от опорной частоты микроконтроллера при помощи соответствующего управляющего регистра, рекомендованная частота преобразования – от 50 до 200кГц, в этом диапазоне наиболее вероятно получение наиболее достоверного результата измерения.

На входе АЦП стоит аналоговый мультиплексор, подключающий этот вход к различным выводам МК. Выбранный канал поступает на вход компаратора. Есть 10-битный ЦАП, устройство выборки и хранения, совмещенное с компаратором. Выход компаратора идет на управляющую логику, включающую регистр последовательных преобразований. Результат поступает на двухбайтный регистр, двухбайтный, потому что состоит из двух частей ADCH и ADCL.

Есть предделитель, который задает частоту преобразования, и управляющий регистр. Мультиплексор управляет источником опорного напряжения, который идет на ЦАП, а также позволяет проводить разделенные во времени измерения сразу нескольких независимых аналоговых величин. Входы мультиплексора могут работать как по отдельности (в несимметричном режиме, измеряя напряжение относительно земли), так и объединяться в пары, измеряя дифференциальное напряжение. Также опционально возможно усиление входного сигнала с фиксированным коэффициентом 10 или 100.

2 режима преобразования:

непрерывный (free-runningmode), когда по завершении одного цикла преобразования сразу же следует другой

одиночный (single), когда последовательность циклов регулируется вручную.

Первый способ не отличается высокой точностью измерений и целесообразен только при необходимости максимальной скорости преобразований.

Параметры АЦП:

Аналоговое напряжение могут считывать только те выводы, которые имеют метку «ADC»

Встроенный источник опорного напряжения. В роли источника опорного напряжения может еще выступать напряжение питания МК.

Максимальное разрешение

Максимальная частота дискретизации (количество тактов, которое ставится на одно АЦП преобразование) – до 1 МГц. Рекомендуемые цифры меньше сотни кГц на один канал.

Управляющие регистры (картинки из даташита ATtiny 13)

1) ADMUX – управляет мультиплексором: выбором источника опорного напряжения; выбором текущего канала (откуда берем аналоговый сигнал); режим хранения данных (по какому краю выравнивание).

REFS (Reference Selection Bits) – определяют источник опорного напряжения, относительно которого будет происходить преобразование (ИОН может быть как напряжением питания, так и внутренним). Опорное напряжение должно быть как можно более стабильным, без помех и колебаний по напряжению – от этого во многом зависит точность работы АЦП. Внутренний источник опорного напряжения не очень точный и подходит только для нетребовательных приложений.

MUX (Analog Channel and Gain Selection Bits) – данные биты определяют текущий вход (канал), с которого мы будем считывать аналоговый сигнал. Также с помощью этих битов выставляется коэффициент усиления при измерении в дифференциальном режиме.

ADLAR – отвечает за выравнивание.

«0» – по правой границе: два бита в ADCH, а младшие в ADCL

«1» – по левой границе: два бита в ADCL, а младшие в ADCH

Лучше использовать выравнивание по правому краю, так как в двух младших битах чаще всего хранится всякий мусор и помехи.

Данные с АЦП записываются в регистровую пару ADCH:ADCL, откуда их можно считать для дальнейшей обработки. Регистровая пара 16 разрядная, а АЦП имеет разрядность 10 бит. В итоге лишь один регистр занят полностью, а второй занимают лишь оставшиеся два бита.

2) ADCSRA (ADC Control and Status Register A) – управляющий регистр, отвечающий за работу АЦП:

! ADEN (ADC Enable) – записывая единицу в этот бит, разрешаем использование АЦП.

! ADSC – отвечает за начало АЦП преобразования и устанавливает режим. Устанавливания 1 выбираем одиночный режим преобразования.

ADATE (ADC Auto Trigger Enable) – возможность запуска преобразований от внешних источников, таймера и тп.

ADIF (ADC Interrupt Flag) – флаг прерывания по завершению преобразования, когда регистры данных обновились. Автоматически. (вроде как устанавливается в 1 по завершению цикла преобразования)

! ADIE (ADC Interrupt Enable) – разрешение прерывания по завершению цикла преобразования.

! ADPS (ADC Prescaler Select Bits) – позволяет выбрать коэффициент делителя тактовых импульсов для установки частоты преобразований (в непрерывном режиме).

ADFR (ADC Free Running Select) – записывая единицу в этот бит, выбираем непрерывный режим преобразования.

3) Пара ADCH:ADCL – сюда записываются данные с АЦП преобразования (про них написано где и про ADLAR)

4) ADCSRB – источник запуска АЦП преобразования: переполнение таймера, совпадение таймера и т.д.

16. Передача данных с использованием асинхронного последовательного интерфейса UART. Общая структура асинхронного приёмопередатчика. Протокол передачи данных RS-232. Настройка и программирование интерфейса UART. Скорость передачи данных.

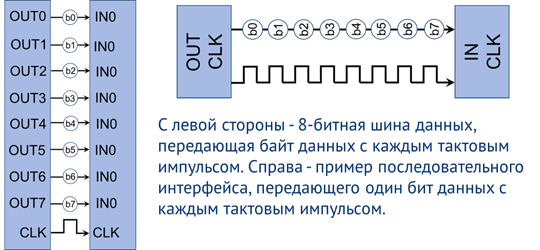

В чем главное отличие между последовательным и параллельным интерфейсом? Параллельные интерфейсы позволяют передавать по несколько бит информации за один раз. Обычно для этого используются шины данных, состоящие из восьми или шестнадцати проводов, поэтому данные передаются большими блоками.

Последовательные интерфейсы передают свои данные по одному биту за такт, что в идеале требует всего одного провода.

Рисунок 1 – Последовательные и параллельные интерфейсы

Параллельные интерфейсы:

+) крайне просты в реализации с точки зрения аппаратного и программного обеспечения.

– ) требуют слишком много проводов и из-за этого работают слишком медленно.

– ) близко расположенные линии представляют собой распределенную емкость и в зависимости от длины еще и распределенную индуктивность, из-за этого возникают искажения (рисунок 2)

Рисунок 2 – Искажения сигнала

Все сигналы от передатчика к приёмнику должны поступать одновременно. Но гарантировать время прохождения сигнала для всех линий параллельного интерфейса на больших частотах очень тяжело, при этом неизбежно искажается форма передаваемого сигнала.

Сейчас последовательные интерфейсы полностью вытеснили параллельные. Для персональных компьютеров общим стандартом для обмена данными с периферией стал USB интерфейс, практически полностью заменив собой RS-232. Однако удобство пользования и обилие программного обеспечения, имеющего доступ к внешним устройствам через COM-порт, вынудило разработчиков создать драйвера виртуальных COM-портов.

Интерфейса RS-232

Ранее популярный метод передачи данных. На задней панели некоторых компьютеров, особенно старых, среди разъёмов можно заметить D-образный штекер с 9 контактами, также известный как COM-порт (от слова communication).

СОМ-ПОРТ |

Виртуальный COM-порт |

|

|

Общая структура UART

По структуре это обычный асинхронный последовательный протокол как и RS-232, т.е. передающая сторона по очереди выдает в линию нули и единицы, а принимающая отслеживает и запоминает их (асинхронный, потому что нет линии тактовых импульсов, отвечающей за скорость передачи данных).

Синхронизация идет по времени – мы заранее задаем скорость передачи данных как на стороне передатчика информации, так и на стороне приемника.

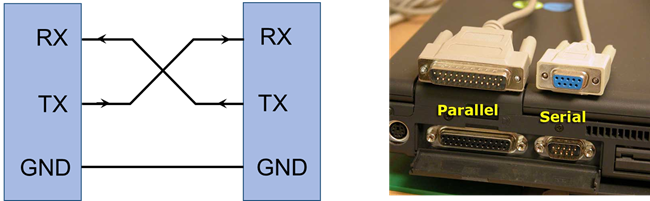

Аппаратная реализация: достаточно 2 проводов, не считая общего провода, подключаемого обычно к напряжению земли (рис. 3).

Линия RXD используется для приема сообщений (Receiver), а линия TXD – для передачи сообщений (Transmitter).

UART является полнодуплексным интерфейсом. Это значит, что приемник и передатчик работают независимо друг от друга, позволяя одновременно как передавать, так и принимать данные (так называемая полнодуплексная передача данных).

Рисунок 3 – Аппаратное обеспечение UART

Протокол передачи данных

Передача (соответственно, и прием) сообщений осуществляется фиксированными пакетами битов, такой пакет называют кадром (рис. 4).

Рисунок 4 – Пакет данных для передачи по интерфейсу UART

Кадр состоит из стартового бита (с него начинается каждый кадр), битов данных (их количество можно изменять от 5 до 9), бита проверки четности (проверка правильности передачи данных) и одного или двух стоп-битов (обязательный сигнал окончания кадра).

Вначале передатчик переводит линию в уровень логического нуля – это стартовый бит. Между пакетами данных линия передатчика находится в состоянии логической единицы, поэтому зафиксировав появление нуля (тот самый стартовый бит), приемник отсчитывает интервал Т1 и считывает первый бит данных, потом через интервалы Т2 считывает все оставшиеся биты.

В конце байта, перед стоповым битом, может находиться бит проверки четности. Так называют контрольный бит, служащий для проверки общей чётности двоичного числа (чётности количества единичных битов в числе).

Все параметры задаются строго перед началом передачи данных и не могут быть изменены в процессе. Самый распространенный формат передачи данных для микроконтроллеров – 8 бит данных, 1 стартовый бит, 1 стоповый бит, без проверки на четность.

Для организации последовательной передачи необходимо много настроек (Условное обозначение – данные/четность/стоп биты):

Скорость передачи (baudrate)

Количество бит в пакете (обычно 8 бит)

Проверка на четность

Стоп-биты отправляются в конце каждого пакета данных

Настройка и программирование интерфейса UART

Регистры, имеющие отношение к приемопередатчику.

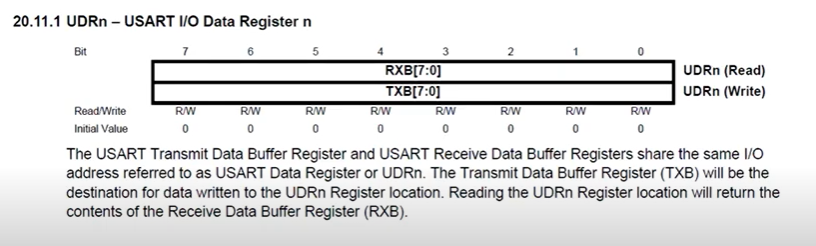

1) UDRx (UART Data Registor) – на физическом уровне представляет собой два разных регистра, имеющих одинаковый адрес.

При записи информация поступает в первый регистр (регистр передатчика TXB), а при чтении берется из другого (регистр приемника RXB). И при чтении, и при записи данных используется один регистр, что облегчает процесс программирования.

О том, что байт полностью пришел в регистр UDR, нам указывает прерывание по завершении приема, которое вызывается сразу же после того, как приемник обрабатывает все поступившие в него биты.

2) UCSRA, UCSRB, UCSRC – регистры конфигурации, хранящие все настройки приемопередатчика

UCSRA (USART (S – потому что еще и синхронным может быть) Control and Status Register):

RXCn (Receive Complete) – флаг прерывания по приему данных. Устанавливается в «1», когда принимаемый байт записался в UDR.

TXCn (Transmit Complete) – флаг прерывания по передачи данных. Устанавливается в «1» после прохождения последнего стоп-бита и отсутствия новых данных в регистре UDR, т.е. после окончания передачи всех битов.

Одновременно с этими влагами вызывается прерывание

UDREn (USART Data Register Empty) – сообщает, что регистр UDR пуст. Сбрасывается он аппаратно после записи новой порции данных в UDR, при этом генерируется соответствующее прерывание.

U2Xn (Double the USART Transmission Empty) – бит удвоения скорости передачи данных при работе в асинхронном режиме.

Регистр UCSRxB

RXEN (Receiver Enable) и TXEN (Transmitter Enable) – при записи в них логической единицы осуществляется разрешение приема и передачи, соответственно.

RXCIEn (RX Complete Interrupt Enable) и TXCIE – осуществляет разрешение прерывания по завершению приема и передачи данных соответственно.

UDRIEn (UART DATA Register Empty Interrupt Enable) – осуществляется разрешение прерывания по опустошению регистра передачи данных UDR.

UCSZn – определяют количество бит данных, которые мы передаем в нашем пакете.

Регистр UCSRxC – выбор необходимого протокола передачи данных.

UMSEL (UART Mode Select) – задаем формат передачи: синхронный («0») или асинхронный («1»)

UPM (UART Parity Mode) – установка проверки на четность, по умолчанию в оба бита записаны логические нули, передача данных ведется без проверки на четность.

USBS (UART Stop Bit Select) – определяет количество стоповых битов (0 – 1 стоповый бит, 1 – 2 стоповых бита).

UCSZ (UART Character Size) – уже упоминался выше. Определяет количество передаваемых битов данных.

UCPOLn – полярность нашего тактового сигнала (для синхронной передачи). Определяет момент выдачи и считывания данных на выводах модуля USART.

3) UBRRH:UBRRL – регистровая пара, задающая скорость передачи данных

Скорость передачи данных

Старший (H) использует всего 4 бита. Число разбиваем на две части и записываем в регистры.

Скорость вычисляется по следующей формуле (без удвоения скорости):

Нижняя для удвоенной скорости.

где, XTAL – тактовая частота, на которой работает наш МК

baudrate – требуемая скорость.

Также значение UBBR можно найти по таблице в даташите. Надо знать скорость и частоту работы МК.

17. Передача данных с использованием асинхронного последовательного интерфейса SPI. Схема организации SPI интерфейса, сдвиговые регистры. Пакетная передача данных. Диаграмма передачи данных по SPI, режимы передачи данных. Управляющие регистры, скорость передачи данных. Работа в режиме передачи (Master) и приёма данных (Slave).

SPI (Serial Peripheral Interface – последовательный периферийный интерфейс) – последовательный синхронный стандарт передачи данных в режиме дуплекса, предназначенный для обеспечения простого и недорогого высокоскоростного сопряжения микроконтроллеров и периферии.

Также называют четырехпроводным (four-wire) – для подключения нужно 4 провода.

SPI является синхронным интерфейсом, в котором любая передача синхронизирована с общим тактовым сигналом, генерируемым ведущим устройством (чаще всего в роли ведущего выступает микроконтроллер). Принимающая (ведомая) периферия синхронизирует получение битовой последовательности с тактовым сигналом.

На стороне ведомого делать никаких настроек не нужно, т.к. генератор находится на стороне ведущего, где все и настраивается.

К одному последовательному периферийному интерфейсу ведущего устройства-микросхемы может присоединяться несколько устройств. Ведущее устройство выбирает ведомое для передачи, активируя сигнал «выбор кристалла» (chip select) на ведомой микросхеме (чтобы знать с кем мы сейчас общаемся). НЕДОСТАТОК: чем больше датчиков, тем больше линий потребуется. Периферия, не выбранная ведущим устройством, не принимает участие в передаче по SPI.

Основное предназначение этого интерфейса – подключение к микроконтроллеру различных периферийных устройств.

Очень быстро SPI стал популярен по следующим причинам:

1) Минимальные требования к аппаратной части подключаемого к МК устройства (сдвиговый регистр);

2) SPI-ведущего в минимальной конфигурации легко эмулировать программным образом, если в микроконтроллере отсутствует его аппаратная реализация.

Периферийные узлы, подключаемые к микроконтроллеру через SPI:

датчики физических величин (температуры, давления, ускорения); устройства аналого-цифрового преобразования (АЦП, ЦАП, цифровые потенциометры);

устройства преобразования интерфейсов (CAN-контроллеры, Ethernet-контроллеры);

модули энергонезависимой памяти (Flash-карты MMC и SD, микросхемы EEPROM) и многие другие.

Аппаратное обеспечение SPI

У нас есть ведущий – Master (МК) и ведомый – Slave (датчики, устройства).

С точки зрения аппаратного обеспечения: 2 регистра сдвига 1 – со стороны мастера, другой со стороны slave, объединенные в кольцо (выход одного идет на вход другого). Передачей данных управляет тактовый генератор.

В SPI используются четыре линии передачи (рисунок 1).

Рисунок 1 – Схема организации SPI интерфейса

1) MOSI – выход ведущего, вход ведомого (Master Out Slave In). Служит для передачи данных от ведущего устройства ведомому.

2) MISO – вход ведущего, выход ведомого (Master In Slave Out). Служит для передачи данных от ведомого устройства ведущему.

3) SCK – последовательный тактовый сигнал (Serial Clock). Служит для передачи тактового сигнала для ведомых устройств.

4) CS (SS) – выбор микросхемы, выбор ведомого (Chip Select, Slave Select).

Главным составным блоком интерфейса SPI является обычный сдвиговый регистр (который одновременно выполняет и функцию приемника, и функцию передатчика), сигналы синхронизации и ввода/вывода битового потока которого и образуют интерфейсные сигналы. Таким образом, протокол SPI правильнее назвать не протоколом передачи данных, а протоколом обмена данными между двумя сдвиговыми регистрами.

Частота следования битовых интервалов определяется синхросигналом SCK, который генерирует ведущий (Master). Ведомые используют синхросигнал для определения моментов изменения битов на линии данных.

Передача битов осуществляется пакетами. Длина пакета чаще всего составляет 1 байт (8 битов).

В ведущем устройстве, так и в ведомом имеется (обычно недоступный из исполняемой программы) счетчик импульсов синхронизации (битов). Счетчик в ведомом устройстве позволяет определить момент окончания передачи пакета. В ведомом устройстве счетчик битов обычно сбрасывается деактивацией интерфейсного сигнала SS. Передача пакета, т. е. запуск генератора синхроимпульсов в ведущем, обычно осуществляется автоматически при записи передаваемого байта в регистр сдвига ведущего.

Задание частоты следования битов FSCK осуществляется стандартным для последовательных интерфейсов способом:

FSCK=FG/DIV,

где FG – постоянная частота задающего генератора SPI,

DIV – делитель, который может быть задан программным образом.

Поскольку действия на ведущем и ведомом устройствах тактируются одним и тем же сигналом SCK, к стабильности частоты этого сигнала не предъявляется никаких требований (за исключением ограничения сверху на длительности полупериодов, определяемого максимальной рабочей частотой более медленного абонента).

Передача данных

Существует три типа подключения к шине SPI, в каждом из которых участвуют четыре сигнала. (Простейшее, независимое (параллельное), каскадное (последовательное) – картинки будут ниже)

Чтобы подчиненная микросхема принимала и передавала данные, помимо наличия сигнала синхронизации необходимо также, чтобы линия СS была переведена в низкое состояние.

До начала передачи пакета, левее момента времени А, сигнал SS на выходе ведущего в высоком состоянии, ведомый неактивен, его выход MISO в отключенном состоянии, а входы ведомого MOSI и SCK не воспринимают сигналов, формируемых ведущим. Тактовый сигнал (SCK) на выходе ведущего в этот период имеет низкий уровень.

Для активации ведомого ведущий переводит в активное (низкое) состояние сигнал SS выбора ведомого (момент времени A). Ведомый включается, его вход тактирования способен воспринимать тактовый сигнал, а вывод MISO переходит в режим выхода. Тактовые импульсы пока еще не начались, выходные сигналы на линях данных MOSI и MISO теперь отражают значения бита, который будет первым передан другому абоненту.

Через некоторое время ведущий начинает формирование пакета сдвиговых импульсов – сигнал SCK (настройки: передача по переднему фронту данных). Перепады тактового сигнала вызывают сдвиг содержимого сдвиговых регистров ведущего и ведомого, а также захват новых значений битов после сдвига. Моменты сдвига и захвата должны быть разнесены во времени, поэтому эти действия выполняются в интерфейсе SPI по разным перепадам тактовых импульсов. Диаграмма изображена в предположении, что захват производится по нарастанию тактового сигнала (по нечетным перепадам на рисунке), а сдвиг в регистрах – по спаду (четные перепады). Таким образом, порядок событий при действии каждого тактового импульса можно описать как «захват, затем сдвиг» (Latch, then Shift).

После окончания обмена пакетами (правее перепада 16-тактовой последовательности) выходной сигнал на каждой из линий данных MOSI и MISO отражает значение бита, который был передан первым. Передача пакета завершается снятием сигнала SS на выходе ведущего (момент B), что деактивирует ведомого абонента. Через некоторое время возможно начало передачи следующего пакета (момент С).

Достоинства |

Недостатки |

Простота аппаратной реализации |

Ведомое устройство не может управлять потоком данных (даже если оно не принимает эти данные) |

Можно использовать в системах с низкостабильной тактовой частотой (поскольку мастер задает скорость передачи для всех) |

Необходимо больше выводов, чем для интерфейса I2С (отдельная линия CS на каждое внешнее устройство) |

Максимальная тактовая частота ограничена только быстродействием мастера (ведущего) и максимально допустимой частотой ведомого |

Отсутствие официального стандарта, что делает невозможным сертификацию устройств (наличие множества вариантов реализации интерфейса) |

Полнодуплексная передача данных по умолчанию (за счет того, что 2 сдвиговых регистра закольцованы) |

|

Возможность произвольного выбора длины пакета (держим линию CS на низком уровне сколько надо) |

|

Регистры, отвечающие за работу SPI

За функционирование SPI у нас отвечают два основных регистра:

1) SPCR (SPI Control Register) – регистр управления.

SPIE (SPI Interrupt Enable) – разрешение прерывания по окончанию передачи\приема данных.

SPE (SPI Enable) – разрешение на работу самого SPI. Если этот бит установлен в единицу, то выводы #SS, MISO, MOSI и SCK работают как выводы SPI, иначе – как простые выводы порта.

DORD (Data Order) – определяет направление передачи данных. Если он установлен, то передача идёт с младшего бита, если сброшен – со старшего.

MSTR (Master/Slave Select) – выбора направления передачи данных. Если этот бит установлен, контроллер работает как Master (т. е. на передачу данных), если сброшен – как Slave (на прием данных). Управляется также выводом SS, если он настроен на ввод – при подаче "0" на SS бит MSTR сбрасывается.

CPOL (Clock Polarity) – отвечает за режим работы. Определяет уровень на выходе SCK в режиме ожидания.

CPHA (Clock Phase) – если этот бит установлен, передача и приём данных производится по заднему фронту тактового импульса, если сброшен – по переднему.

SPR1, SPR0 (SPI Clock Rate Select) – предделитель тактовой частоты микроконтроллера, определяющие частоту работы SPI в режиме Master. В режиме Slave эти два бита не несут на себе никакой нагрузки.

2) SPSR (SPI Status Register) – регистр состояния.

SPIF (SPI Interrupt Flag) – флаг прерывания по окончании передачи данных. Устанавливается и сбрасывается аппаратно.

WCOL (Write COLlision flag) – флаг наложения. Устанавливается, когда передача данных еще не завершена, а в регистр данных SPDR уже записывается следующий байт. Сбрасывается чтением регистра состояния.

SPI2X (Double SPI Speed Bit) – установленный в единицу, этот бит удваивает частоту тактовых импульсов по линии SCK, и, соответственно, удваивает скорость передачи данных.

3) SPDR (SPI Data Register) – регистр данных. Используется для приема и передачи данных по SPI интерфейсу. Запись байта в этот регистр начинает передачу данных. Чтение из него освобождает приемный буфер сдвигового регистра.

Сюда записываем данные и считываем их. Записываем прямо в регистр и так инициализируем передачу. Считываем с буфера.