- •Бийский технологический институт (филиал)

- •Техника двоичной переработки информации Курс лекций

- •Содержание

- •1 Сопряжение аналоговых и цифровых устройств

- •1.1 Процесс аналого-цифрового преобразования

- •1.2 Процесс цифро-аналогового преобразования

- •1.3 Основные характеристики цап и ацп

- •1.4.1 Цап со взвешивающей резистивной матрицей

- •1.4.2 Цап с матрицей r-2r

- •1.5.1 Ацп последовательного счёта

- •1.5.2 Ацп поразрядного кодирования

- •1.5.3 Ацп параллельного действия

- •1.6 Основное уравнение для цап и ацп

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •2 Запоминающие устройства

- •2.1 Основные параметры зу

- •2.1.1 Емкость зу

- •2.1.2 Организация зу

- •2.1.3 Время выборки зу

- •2.1.4 Время цикла адреса зу

- •2.2 Зу с одномерной адресацией

- •2.3 Зу с двумерной адресацией

- •2.4 Увеличение объёма памяти зу

- •2.4.1 Построение блока зу требуемой разрядности

- •2.4.2 Увеличение числа хранимых слов зу

- •2.4.3 Увеличение разрядности и числа хранимых слов зу

- •2.5 Аппаратные особенности построения статических озу

- •2.6 Аппаратные особенности построения динамических озу

- •2.7 Аппаратные особенности построения пзу

- •2.7.1 Масочные пзу

- •2.7.2 Программируемые пзу

- •2.7.3 Репрограммируемые пзу

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •3 Программируемые логические интегральные схемы

- •3.1 Обобщённая структурная схема плис

- •3.2 Применение ппзу в качестве плис

- •3.3 Программируемая матричная логика

- •3.4 Программируемые логические матрицы

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •4 Основные понятия микропроцессорной техники

- •4.1 Микропроцессор. Основные термины и определения

- •4.2 Классификация мп

- •4.3 Структура типового мп

- •4.3.1 Арифметико-логические устройства

- •4.4 Режимы работы мп

- •4.4.1 Нормальный режим работы мп

- •4.4.2 Режим прерывания

- •4.4.3 Режим ожидания

- •4.4.4 Режим прямого доступа к памяти

- •4.5 Система команд однокристального микропроцессора

- •4.6 Периферийные устройства микропроцессорных систем

- •4.6.1 Универсальный синхронно-асинхронный приёмо-передатчик

- •4.6.2 Таймер-счётчик

- •4.6.3 Устройство ввода/вывода параллельной информации

- •4.6.4 Контроллер прямого доступа к памяти

- •4.6.5 Контроллер прерываний

- •4.6.6 Динамическая индикация

- •4.6.7 Динамическая клавиатура

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •Техника двоичной переработки информации

1.5.2 Ацп поразрядного кодирования

В основе построения АЦП поразрядного кодирования лежит регистр последовательного приближения (РПП).

Если вместо счётчика в структурной схеме на рисунке 7 использовать РПП, выход компаратора подать на вход сравнения РПП, ГТИ подключить ко входу синхронизации РПП, то получится АЦП поразрядного кодирования, или, как его ещё называют, АЦП последовательного приближения.

Вспомнив алгоритм работы РПП, легко увидеть, что число импульсов, необходимое для выполнения преобразования, равно разрядности выходного кода АЦП, то есть время преобразования

![]() .

.

Очевидно, что это время не зависит от входного напряжения и существенно меньше времени, необходимого для преобразования в АЦП последовательного счета.

Ввиду своей достаточной простоты и хорошего быстродействия данный тип АЦП находит широкое применение при разработке ИС.

1.5.3 Ацп параллельного действия

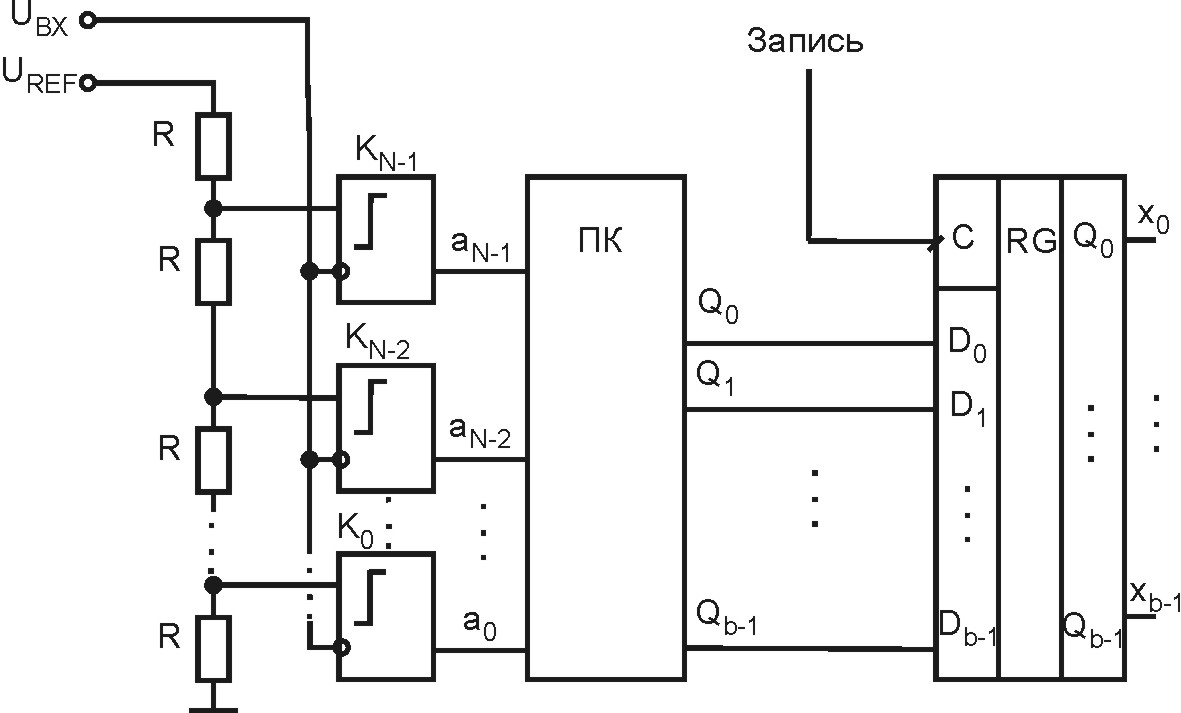

Данный тип АЦП реализует метод непосредственного считывания и является на сегодняшний день самым быстродействующим. Классический принцип его работы поясняется рисунком 11.

Устройство

содержит 2b

– 1 компараторов К, на

объединенные инвертирующие входы

которых подается входной преобразуемый

сигнал. На неинвертирующие входы

компараторов подаются напряжения,

численно равные уровням квантования

![]() .

В результате с выходов компаратора

снимается параллельный N-разрядный

единичный код. Число единиц в нем

равно числу уровней квантования по

величине меньших значений UВХ.

.

В результате с выходов компаратора

снимается параллельный N-разрядный

единичный код. Число единиц в нем

равно числу уровней квантования по

величине меньших значений UВХ.

Полученный единичный код подается на вход преобразователя кода (ПК), в котором он преобразуется в двоичный с числом разрядов b = lоg2N. С выхода ПК двоичный код подается на вход регистра, с выхода которого он и считывается. Перезапись кода ПК в регистр происходит по сигналу «Запись». Этот сигнал подается в схему после того, как все переходные процессы, связанные со срабатыванием компараторов и получением двоичного кода, завершены.

Рисунок 11 – Структурная схема ЦАП параллельного действия

Для получения напряжений, равных уровням квантования в схеме, использован делитель напряжения на N одинаковых резисторах, подключенный к выходу источника эталонного напряжения UREF. Формирование в данном АЦП выходного кода одновременно по всем разрядам предполагает получение максимально возможного быстродействия. Его время преобразования определяется только структурой ПК и собственным быстродействием используемой элементной базы.

Следует заметить,

что повышение точности работы АЦП

данного типа всегда связано со

значительными аппаратными затратами.

Так, для построения 8-разрядного АЦП

необходимо 255 компараторов. Реально

общее число элементов в ИС такого АЦП

достигает порядка

![]() ,

а потребляемая мощность 2,5 Вт.

,

а потребляемая мощность 2,5 Вт.

На практике компромисс между быстродействием и сложностью схемы разрешается в так называемых параллельно-последовательных схемах АЦП.

Принцип их работы основан на выделении в АЦП нескольких самостоятельных структур (групп). Например, при двух структурах первая осуществляет грубое преобразование, формируя старшие разряды выходного кода, вторая формирует младшие разряды выходного кода. На ее вход подается разность входного напряжения и напряжения с выхода дополнительного ЦАП, преобразующего в аналоговую величину код старших выходных разрядов. Для повышения точности преобразования эта разность усиливается в 2l раз, l – разрядность кода на выходе первой «грубой» структуры.

Такое решение позволяет при приемлемой сложности реализации увеличить число выходных разрядов АЦП до 10…12. Реальное время преобразования в АЦП параллельного типа достигает 10…20 нc.