Национальный исследовательский ядерный университет «МИФИ»

|

Факультет Кибернетики и информационной безопасности

Кафедра «Компьютерные системы и технологии»

|

Реферат по предмету

«Архитектура вычислительных систем»

на тему:

Многоядерный процессор Cortex-A9 MPCore

Студент гр. К1-12М Панин Ю. Ю.

Руководитель Чепин Е. В.

Москва 2012

Оглавление

ARM Cortex 3

ARMv7-A 4

Cortex-A9 6

Cortex-A9 MPCore 11

Структурная нотация 16

Список литературы 17

ARM Cortex

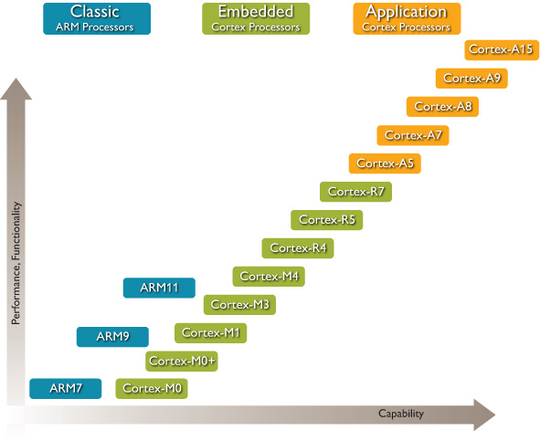

Процессорные ядра Cortex — результат развития классической архитектуры ARM, семейство со стандартизированной архитектурой, предназначенное для решения широкого круга технологических задач. В семействе Cortex реализуются три подсемейства:

Cortex-M – для микроконтроллерных и недорогих встроенных приложений;

Cortex-A – для высокопроизводительных приложений;

Cortex-R – для приложений реального времени.

На рисунке 1 показано соотношение возможностей процессорных ядер Cortex различных подсемейств между собой и в сравнении с классическими ARM микроконтроллерами.

Рис. 1.Процессоры ARM

Процессорные ядра подсемейства Cortex-A предназначены для работы со сложными пользовательскими интерфейсами. Кроме открытых ОС Linux и Android, заявлена поддержка платформы ARM ОС Microsoft Windows 8.

ArMv7-a

Процессор Cortex-A9 реализует 32 разрядную усовершенствованную RISC архитектуру ARMv7-A. Возможности архитектуры в сравнении с предыдущими ARM поколениями представлены на рисунке 2.

Рис. 2. Архитектуры ARM

ARM – набор 32-разрядных инструкций.

Thumb – из всего набора 32-разрядных инструкций отобраны наиболее часто используемые и перекодированы в 16-разрядные коды, при выборке такой инструкции аппаратным образом восстанавливается истинный 32-разрядный код, который и выполняется процессором.

Thumb2 – внесено 130 дополнительных команд, расширяет ограниченный набор 16-разрядных кодов Thumb 32-разрядными командами, улучшенное использование памяти.

VFP – Vector Floating Point, обеспечивает выполнение операций над числами с плавающей запятой в соответствии со стандартом ANSI/IEEE Std 754(Standard for Binary Floating-Point Arithmetic). В VFPv3 используется расширение половинной точностью, что предоставляет функцию взаимообратного преобразования между числами половинной и одинарной точности. Так же реализованы инструкции преобразования чисел с плавающей и фиксированной запятой для вычислений с двойной точностью.

Jazelle – технология дает возможность ARM-процессору выполнять Java-код на аппаратном уровне.

TrustZone – технология аппаратной защиты данных, которая предусматривает создание областей для защищенных приложений, в которых они могут работать отдельно от незащищенных.

SIMD – векторные операции над целыми числами и числами с плавающей запятой.

NEON – усовершенствованный SIMD, 32 64-разрядных регистра, которые могут использоваться как 16 128-разрядных. Ускоряет обработку аудио-, видео- и графических данных. Он содержит собственный регистровый файл и исполнительный конвейер, отделенные от основного целочисленного конвейера ядра. Конвейер NEON-блока работает с плавающей запятой и целыми числами. Он поддерживает операции с невыровненными данными и обеспечивает простую загрузку перемежающихся данных, хранимых в структурированном виде.

Virtualization – предоставляет аппаратную поддержку для виртуализации. Расширение поддерживает системное использование монитора виртуальной машины (гипервизора) для переключения гостевых операционных систем. Независимо от применения на однопроцессорной или многопроцессорной системе расширение виртуализации позволяет запускать несколько виртуальных машин на одном ядре.