Лабораторная работа №51

.docМинистерство образования Республики Беларусь

УО МОГИЛЕВСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ПРОДОВОЛЬСТВИЯ

Кафедра «автоматизации технологических процессов и производств»

«Исследование двоичных логических элементов»

Лабораторная работа №5

по дисциплине «Электроника»

Специальность 1 53 01 01 « Автоматизация технологических процессов и производств»

Проверил Выполнил

старший преподаватель студент группы АТПП -

__________ Е.А.КОЛЮКОВИЧ

«____» _______________ 2007 г. «____» ___________ 2007 г.

Могилев 2007

Цель работы: исследование логических схем, реализация логических функций при помощи логических элементов, синтез логических схем, выполняющих заданные логические функции.

Ход работы

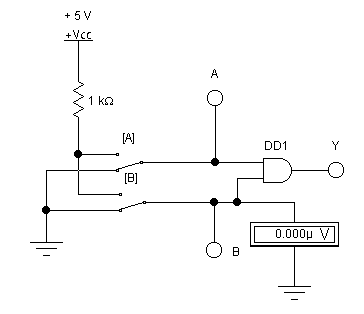

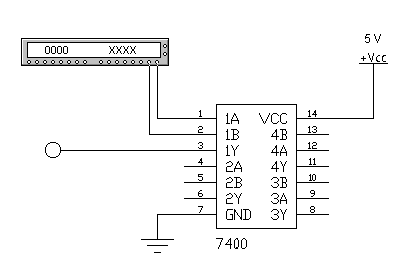

Собрали схему в соответствии с рисунком 1. В схему включены: логические пробники, источник постоянного напряжения + 5 В, двухпозиционные переключатели, резистор 1 кОм, индикаторный вольтметр и логический элемент 2И.

Рисунок 1 — Схема 2И

Исследование логической функции И

а). Задание уровней логических сигналов.

В схеме, приведённой на рисунке 1, два двухпозиционных переключателя [А] и [В] подают на входы логической схемы И уровни 0 (контакт переключателя в нижнем положении) или 1 (контакт переключателя в верхнем положении). Включили схему. Установили переключатель [В] в нижнее положение. Измерили вольтметром напряжение на входе B логического элемента 2И и определили с помощью логического пробника уровень логического сигнала. Установили переключатель [В] в верхнее положение. Определили уровень логического сигнала на входе B логического элемента 2И и записали показания вольтметра; укажите, какой логический сигнал формируется на выходе Y схемы 2И. Результаты занесли в таблицу 1.

б). Экспериментальное получение таблицы истинности логического элемента И.

Подайте на входы схемы все возможные комбинации уровней сигналов А и В и для каждой комбинации зафиксируйте уровень выходного сигнала Y. Заполните таблицу истинности логической схемы И (таблица 2).

Таблица 1 — Задание уровней логических сигналов

|

Напряжение на входе B (контакт [B] в нижнем положении), В |

0 |

|

Логический уровень на входе B (контакт [B] в нижнем положении) |

0 |

|

Напряжение на входе B (контакт [B] в верхнем положении), В |

4,985 |

|

Логический уровень на входе B (контакт [B] в верхнем положении) |

1 |

|

Логический уровень на выходе Y |

0 |

Таблица 2.8 — Таблица истинности логического элемента 2И

-

A

B

Y

0

0

0

1

0

0

0

1

0

1

1

1

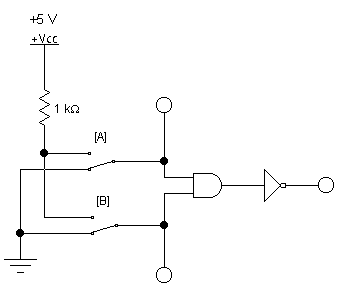

Экспериментальное получение таблицы истинности логического элемента 2И-НЕ, составленного из элементов 2И и НЕ.

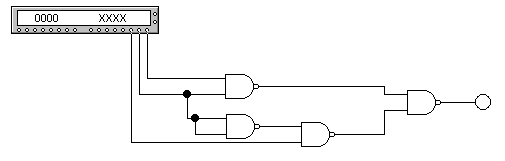

Собрали схему, изображенную на рисунке 2. Включили схему и подали на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с помощью логических пробников, заполнили таблицу истинности логической схемы 2И-НЕ (таблица 3)

Рисунок 2 — Схема 2И-НЕ

Таблица 3 — Таблица истинности логического элемента 2И-НЕ

|

A |

B |

Y |

|

0 |

0 |

1 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

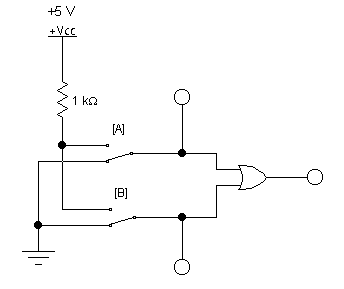

Экспериментальное получение таблицы истинности логического элемента 2ИЛИ.

Собрали схему, приведённую на рисунке 4. Включили схему и подали на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с помощью логических пробников, заполнили таблицу истинности логической схемы ИЛИ (таблица 4).

Рисунок 3 — Схема ИЛИ

Таблица 4 — Таблица истинности логического элемента 2ИЛИ

|

A |

B |

Y |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

1 |

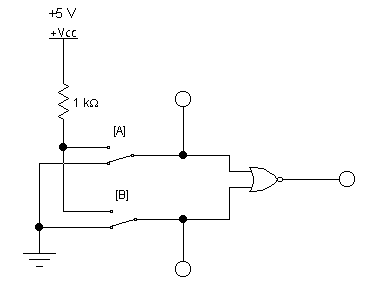

Экспериментальное получение таблицы истинности логического элемента 2ИЛИ-НЕ.

Собрали схему, изображенную на рисунке 4. Включили схему и подали на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с помощью логических пробников, заполните таблицу истинности логической схемы 2ИЛИ-НЕ (таблица 5).

Таблица 5 — Таблица истинности логического элемента 2ИЛИ-НЕ

|

A |

B |

Y |

|

0 |

0 |

1 |

|

1 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

1 |

0 |

Рисунок 4 — Схема 2ИЛИ-НЕ

Исследование логических схем с помощью генератора слов.

а). Сведения об исследуемой микросхеме.

Собрали схему, приведённую на рисунке 5. Включили схему. Укажите, к каким выводам микросхемы 7400 подключается источник питания, сколько элементов 2И-НЕ содержит микросхема, сколько элементов используется в данном эксперименте и как обозначены на схеме используемые входы и выходы. Заполните таблицу сведений о микросхеме (таблица 6).

Рисунок 5 — Микросхема 7400 (четыре 2И-НЕ)

Таблица 6 — Сведения об исследуемой микросхеме

|

Число элементов И-НЕ в микросхеме |

4 |

|

Число исследуемых элементов 2И-НЕ |

1 |

|

Обозначение выводов для подключения источника питания |

VCC |

|

Обозначения используемых входов |

1A и 1B |

|

Обозначение используемого выхода |

1Y |

б). Экспериментальное получение таблицы истинности логического элемента 2И-НЕ.

Запрограммировали генератор слов так, чтобы на выходе генератора можно было последовательно получать следующие комбинации:00, 01, 10, 11(значения разрядов текущего слова на выходе генератора отображаются в круглых окнах в нижней части на панели генератора). Последовательно подавая на микросхему слова из заданной последовательности, заполнили таблицу истинности элемента 2И-НЕ (таблица 7).

Таблица 7 — Таблица истинности логического элемента 2И-НЕ микросхемы 7400

|

A |

B |

Y |

|

0 |

0 |

1 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

Реализация логической функции 3-х переменных.

Синтез схемы, реализующей функцию, заданную логическим выражением

Реализуем функцию F = ab + b`c на элементах 2И-НЕ.

Рисунок 6 − Схемная реализация функции на элементах 2И-НЕ

Собрали в Electronics Workbench схему на элементах 2И-НЕ (рисунок 6), соответствующую логическому выражению F = ab + b`c . Подключили к входам схемы генератор слов, к выходу - логический пробник. Генератор слов запрограммировали на формирование последовательности из восьми слов, соответствующих числам от 0 до 7.

В пошаговом режиме, последовательно подавая на вход полученной схемы все слова последовательности, определите при помощи логического пробника уровень сигнала на выходе схемы. По полученным результатам заполните таблицу 8.

Таблица 8 — Таблица истинности функции F = ab + b`c

-

с

b

a

F

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

1

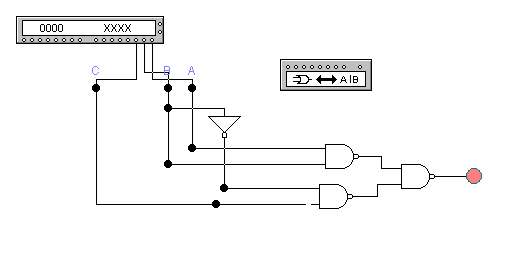

Синтез схемы, реализующей заданную функцию при помощи логического преобразователя.

Для получения схемы, реализующей функцию, описываемую логическим выражением F = ab + b’c, можно воспользоваться логическим преобразователем.

Перевели генератор слов в пошаговый режим. Включили схему. Последовательно подавая на входы схемы слова из заданной последовательности, заполнили таблицу истинности (таблица 9).

Рисунок 7− Схемная реализация функции полученная логическим преобразователем

Таблица 9— Таблица истинности схемы, реализующей функцию

F = ab + b’c

|

c |

b |

a |

F |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |