- •1. Освоить практически возможности алгоритмов перевода чисел с использованием различных систем счисления. 5

- •2. Научиться применять способы выполнения арифметических операций с применением машинных кодов чисел. 5

- •3. Приобрести навыки практической работы с информацией во внутримашинном представлении. 5

- •1. Закрепление теоретических знаний по теме занятия. 106

- •Пз№1. Выполнение арифметических операций над числами в эвм Цель занятия:

- •Освоить практически возможности алгоритмов перевода чисел с использованием различных систем счисления.

- •Научиться применять способы выполнения арифметических операций с применением машинных кодов чисел.

- •Приобрести навыки практической работы с информацией во внутримашинном представлении. Теоретические сведения

- •Числа в системах счисления

- •Частные правила перевода

- •Арифметические действия над числами

- •Машинные коды чисел

- •Операции над машинными кодами чисел

- •Задания для работы на занятии:

- •Контрольные вопросы

- •Задание на самоподготовку:

- •Список литературы:

- •1.Освоить практически различные способы минимизации логических функций.

- •2.Научиться применять различные способы решения задач по минимизации логических функций.

- •3.Приобрести навыки практической работы по использованию различных способов минимизации логических функций.

- •Расчетный метод

- •Табличный метод

- •Задание для работы на занятии

- •Законы алгебры логики, следствия из них

- •Свойства элементарных функций.

- •Логические элементы

- •Синтез и анализ логических схем без памяти Синтез логических схем без памяти

- •Выводы:

- •1. Закрепление теоретических знаний по теме занятия;

- •2. Приобрести навыки анализа различных способов представления информации в эвм;

- •3. Совершенствование практических навыков оценки характеристик эвм.

- •Отображение чисел в разрядной сетке эвм.

- •Представление других видов информации

- •Методические рекомендации по подготовке к занятию

- •Задания для работы на занятии:

- •Разрядная функциональная группа

- •Озу типа 2d

- •Алгоритм функционирования озу типа 2d Выполнение операции "Запись";

- •Выполнение операции "Считывание";

- •Озу типа 3d

- •Постоянные зу

- •Определение основных параметров зу

- •Задание для работы на занятии:

- •Задание на самоподготовку

- •Контрольные вопросы

- •Литература

- •Пз №6. Составление алгоритмов и микропрограмм работы алу Цель занятия:

- •Краткие теоретические сведения

- •Запросы прерывания

- •Структура арифметико – логического устройства

- •Алгоритм работы алу при сложении n двоичных чисел с фиксированной запятой в дополнительном коде

- •Алгоритм работы алу при умножении чисел с фиксированной запятой

- •Задание для работы на занятии:

- •Вопросы для самоконтроля:

- •Задание на самоподготовку:

- •Литература:

- •Пз №7. Составление алгоритмов и микропрограмм работы устройства управления Цель занятия:

- •Краткие теоретические сведения об уу цвм

- •Алгоритм работы микропрограммного уу при выполнении операций сложения и умножения.

- •Методические рекомендации:

- •Задание для работы на занятии:

- •Задание для работы на самоподготовке:

- •Вопросы для самоконтроля:

- •Литература:

- •Пз №8. Разработка модулей памяти на бис

- •Закрепление теоретических знаний по теме занятия.

- •Краткие теоретические сведения о структуре памяти эвм

- •Разработка модулей памяти на бис зу

- •Задание для работы на занятии:

- •Задание на самоподготовку:

- •Контрольные вопросы:

- •Приобретение навыков решения задач, связанных с составлением отдельных микрокоманд (микроинструкций) для мпк к589.

- •. Приобретение навыков решения задач, связанных с разработкой алгоритмов и микропрограмм для мпк к589.

- •Проверка степени усвоения материала практического занятия (выполнение курсантами заданий по вариантам).

- •Методические рекомендации по проведению занятия:

- •Вопросы для контроля и самоконтроля: Проверка степени усвоения лекционного материала (устно) и уровня подготовленности курсантов к занятию (летучка).

- •Вопросы для проведения письменного контроля:

- •Задание на самоподготовку:

- •Литература:

- •Система микроопераций микропроцессора к589

- •Пз №10 решение задач разработки аппаратных средств специализированных вычислительных комплексов. Цель занятия:

- •Задание для работы на занятии.

- •Задача №1

- •Краткий теоретический материал по задаче №1

- •Предварительный выбор типов смпк.

- •Расчет цикла работы об

- •Временные характеристики смпк

- •Расчет надежностных характеристик об и аппаратных затрат для его реализации.

- •Сравнительная оценка характеристик об и окончательный выбор типа смпк и структуры об смп

- •Разработка временной диаграммы функционирования об.

- •Пример решения подзадач 1…5

- •Заданные характеристики об

- •Задача №2

- •Краткий теоретический материал по задаче №2

- •1.Обоснование и выбор структурной схемы.

- •2. Построение функциональной схемы.

- •3.Построение принципиальной схемы

- •Разработка структурной, функциональной и принципиальной схем об смп

- •Методические рекомендации:

- •Контрольные вопросы:

- •Задание на самоподготовку:

- •Список литературы:

- •Режимы работы вс

- •Алгоритмы планирования работы вс в различных режимах

- •Алгоритм планирования вычислительного процесса вс, работающей в режиме однопрограммной пакетной обработки

- •Алгоритм планирования вычислительного процесса вс, работающей в режиме классического мультипрограммирования

- •Задание для работы на занятии:

- •Методические рекомендации:

- •Вопросы для самоконтроля:

- •Расчет основных параметров алу.

- •Определение требуемого быстродействия алу.

- •Определение разрядности алу с фиксированной запятой.

- •Определение разрядности алу с плавающей запятой.

- •Определение характеристик озу

- •Пример определения основных параметров вк

- •Определим структуру и формат команд уу.

- •Регистр команд

- •Регистр базы

- •Определим характеристики озу.

- •Задание для работы на занятии.

- •7. Доложить о результатах расчетов преподавателю, ответить на контрольные вопросы. Методические указания:

- •Контрольные вопросы

- •Список литературы:

Структура арифметико – логического устройства

Структура АЛУ зависит от характера использования элементов и узлов, входящих в состав АЛУ, формы представления операндов, способов организации выполнения операций, организации связи между узлами.

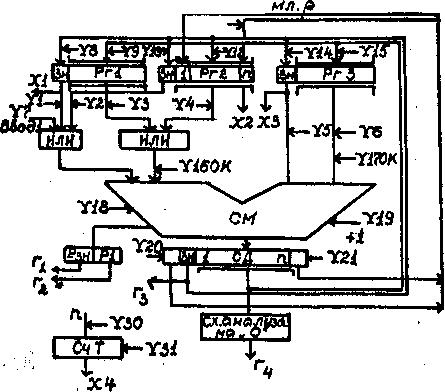

На рис.6.2 представлена упрощенная структурная схема АЛУ для операций над двоичными числами с фиксированной запятой.

Рис. 6.2. Структурная схема АЛУ параллельного типа

В состав АЛУ входят: n – разрядный параллельный комбинационный сумматор СМ; регистры для временного хранения операндов и промежуточных результатов Рг1, Рг2, Рг3; сдвигатель СД; счетчик тактов СчТ; вспомогательные логические схемы ИЛИ; схема анализа на ноль и схема формирования 2-х разрядного кода признака [r1:r2] результата (Рзн и Р1 – переносы из знакового и старшего разряда СМ).

Работа АЛУ осуществляется под действием управляющих сигналов Y1….Y21, которые вырабатываются УУ (БМУ). Каждый УС инициирует определенную микрооперацию, выполняемую в АЛУ. Перечень микроопераций приведен в табл.6.1 Формируемые сигналы X1….X4 и r1...r4 в виде сигналов состояния устройства (ССУ) поступают в УУ и там анализируются. Результаты анализа ССУ позволяют сформировать логическую последовательность микроопераций.

Перечень микроопераций Таблица 6.1.

-

Сигнал

Микрооперации

Выполняемые

действия

Y1

СМ [зн]:=Рг1[зн]

Пересылка знака Рг1 в СМ

Y2

СМ [зн]:=Рг2[зн]

Пересылка знака Рг2 в СМ

Y3

См [1:n]:=Рг1[1:n]

Пересылка в СМ значащей части Рг1

Y4

См [1:n]:=Рг2[1:n]

Пересылка в СМ значащей части РГ2

Y5

СМ [зн]:=Рг3[зн]

Пересылка знака Рг3 в СМ

Y6

См [1:n]:=Рг3[1:n]

Пересылка в СМ значащей части Рг3

Y7

СМ [зн]:=1

Присваивание знаку СМ значения 1

Y8

Рг1[зн]:=СД[зн]

Пересылка знака в Рг1 (Y10, Y14 – аналогичны)

Y9

Рг1[1:n]:=СД[1:n]

Пересылка значащей части в Рг1 (Y12, Y15 – аналогичны)

Y11

Рг2[1]:=СД[n]

Пересылка младшего разряда СД на место старшего разряда Рг2

Y13

Рг2[n]:=СД[1]

Пересылка старшего разряда СД на место младшего разряда Рг2

Y14

Рг3[зн]=СД

Пересылка старшего разряда СД на место младшего разряда Рг2

Y15

Рг3[зн]=СД

Пересылка старшего разряда СД на место младшего разряда Рг2

Y16

См [1:n]:=Рг1[1:n]

Пересылка значащих разрядов из Рг1 с инверсией

Y17

См [1:n]:=Рг3[1:n]

Пересылка значащих разрядов из Рг3 с инверсией

Y18

Рг1+ Рг2

Поразрядное сложение по модулю 2

Y19

СМ:=СМ+1

Прибавление к младшему разряду 1

Y20

СД:=СД

Сдвиг вправо на 1 разряд

Y21

СД:=СД

Сдвиг влево на 1 разряд

Y30

СчТ:= n

Занесение кода числа тактов в счетчик

Y31

СчТ:= СчТ-1

Уменьшение содержимого счётчика на1

Y32

Рг1:=ШД

Пересылки на Рг1 с ШД

Y33

ШД:=Рг1

Пересылки из Рг1 на ЩД

П р и м е ч а н и е: При работе на микроЭВМ, при выполнении алгоритма умножения сначала осуществляется сдвиг множителя (Рг2) по Y20А, потом сдвиг суммы частичных произведений (Рг3) по Y20.