- •Введение

- •1 Расшифровка и анализ задания

- •2.2 Генератор тактовых импульсов к1810гф84

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.7 Программируемый параллельный интерфейс кр580вв55

- •4.2 Программируемый таймер кр580ви53

- •4.3 Программируемый контроллер прерываний кр580вн59

- •4.4 Программируемый контроллер клавиатуры и индикации кр580вв79

- •5 Разработка алгоритма работы мпс

- •6 Реализация одноплатной микроэвм пмв02 на базе мп к1810вм86

- •№ Докум.

- •Подпись

- •Уитс.161ххх.210 пз

Введение

1 Расшифровка и анализ задания

Задание на курсовой проект включает в себя набор исходных данных и ограничений для проектирования управляющей микроЭВМ.

Задание определяет:

- базовый микропроцессор К1810ВМ86, на основе которого требуется построить управляющую микроЭВМ.

- алгоритм управления определяется в задании видом функций f1 и f2 , длительностями управляющих сигналов t1, t2, t3, необходимо при срабатывании аварийного датчика (INT1) сформировать на пульте аварийную сигнализацию светодиодом (2Гц).

![]()

![]() мкс

мкс

![]()

![]() мкс

мкс

![]() мкс

мкс

- типы БИС, на которых должны быть реализованы блоки ПЗУ и ОЗУ: К537РУ8, К541РТ2.

Управляющая микроЭВМ проектируется на базе однокристального МП и включает в себя следующие основные устройства:

- процессорный модуль;

- память, состоящую из ОЗУ и ПЗУ;

- устройства параллельного ввода/вывода для связи с ОУ;

- блок последовательного канала для связи с ЭВМ верхнего уровня;

- программируемый системный таймер;

- контроллер прерываний;

- контроллер прямого доступа к памяти;

- пульт управления.

Алгоритм управления состоит из следующих этапов:

- обработка

информации от цифровых датчиков и выдача

управляюшего воздействия

![]() производится путем ввода значений х1,

х2,

х3,

х4

и вычисления значения булевой функции

f1(х1,

х2,

х3,

х4).(при

единичном значении f1

вырабатывается управляющий сигнал

производится путем ввода значений х1,

х2,

х3,

х4

и вычисления значения булевой функции

f1(х1,

х2,

х3,

х4).(при

единичном значении f1

вырабатывается управляющий сигнал

![]() =1

длительностью t1)

=1

длительностью t1)

- при обработке информации с аналоговых датчиков процессорный модуль принимает 8-разрядные двоичные коды NU1, NU2 с выводов АЦП и код константы К с регистра пульта управления; далее вычисляется значение функции NU=f2(NU1,NU2,K) и сравнивается с константой Q; в зависимости от результотов сравнения вырабатывается один из двух двоичных управляющих сигналов y2 или y3 длительностью t2 или t3 соответственно (если NU<Q, то выдается y2, иначе выдается y3);

- формируется управляющее воздействие Y4, для чего с АЦП вводится значение NU3 производится вычисление по формуле:

![]()

- значение Y4 в виде 8-разрядного кода выдается на вход ЦАП.

В системе необходимо предусмотреть следующие линии запроса на внешние прерывания:

INT0 – отказ источника питания;

INT1 – сигнал ха аварийного датчика ОУ;

INT2 – запрос от пульта управления;

INT3 – запрос от микроЭВМ верхнего уровня.

Программное обеспечение системы разрабатывается на языке Ассемблер соответствующего микропроцессора и включает следующие основные модули:

- модуль начальной инициализации системы;

- модуль управления;

- программы обслуживания прерываний, в том числе драйвер последова-тельного канала.

2 РАЗРАБОТКА ПРОЦЕССОРНОГО МОДУЛЯ, ИНТЕРФЕЙСА И УТОЧНЕННОЙ СТРУКТУРНОЙ СХЕМЫ

В данном курсовом проекте проектируется микроЭВМ на основе микропроцессор К1810ВМ86. Микропроцессорный комплект БИС серии К1810 предназначен для построения как простейших одноплатных микроЭВМ общего назначения, так и мощных мультипроцессорных систем. Комплект используется в системах управления технологическими процессами, производственным оборудованием и промышленными роботами, в контрольно-измерительных комплексах и в информационно-измерительных системах.

2.1 Архитектура и режимы работы МП К1810ВМ86

БИС К1810ВМ86 представляет собой высокопроизводительный 16-разрядный микропроцессор, по усовершенствованной n-канальной МОП-технологии, позволившей получить среднее время задержки распространения сигналов на вентиль 2 нс и обеспечить высокую плотность (29 тыс. транзисторов на кристалл).

Основными архитектурными особенностью микросхемы К1810ВМ86, отличающими ее от микросхемы КР580ИА80А и позволяющими больше чем на порядок повысить производительность систем, являются:

- более мощная система команд с расширенными возможностями адресации памяти, включающая команды умножения, деления и обработки последовательностей байтов или слов;

- аппаратная реализация процесса совмещения операций выполнения и выборки команд;

- более гибкая и мощная организация системы прерываний;

- аппаратная реализация некоторых механизмов взаимодействия нескольких процессоров, упрощающая построение сложных мультипроцес-сорных систем.

Основные системные характеристики микропроцессора К1810ВМ86:

Тактовая частота, МГц 5

Объем адресуемой памяти, Мбайт 1

Разрядность адресной шины 20

Разрядность шины данных 16

Число адресуемых устройств:

ввода/вывода 216/216

основных команд 133

Максимальная потребляемая мощность, Вт 1,75

Тип корпуса 2123.40-6(7)

Рисунок 1 — Структурная схема микропроцессора К1810ВМ86

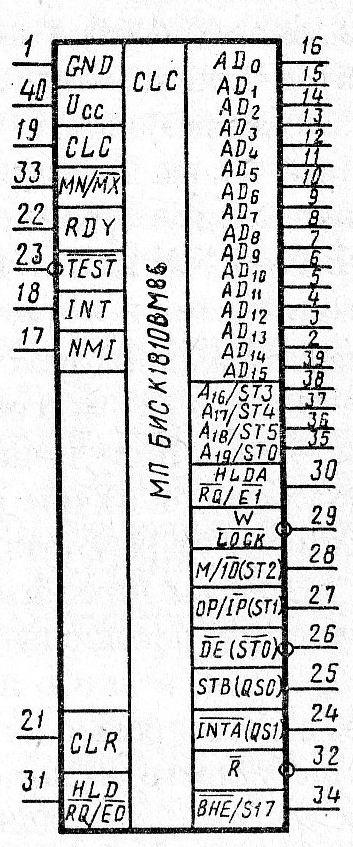

Структурная схема микропроцессора К1810ВМ86 представлена на рисунке 1, она включает следующие устройства: арифметико-логическое устройство (ALU) с тремя регистрами временного хранения операндов (RGB) и регистром признаков (RS); группу регистров общего назначения (R0-R7); микропрограммное устройство управления (МСU) для управления выполнением команд; схему упра-вления доступом к магистрали (DMU); схему внутренней синхронизации (СLG), преобразующую внешние тактовые импульсы во внутренние последовательности синхроимпульсов и обеспечивающую синхронизацию МП с медленными ЗУ и УВВ; схему обработки запросов прерываний (INTU); схему управления циклами обмена (СU), осуществляющую управление работой 16-разрядного канала адреса/данных; буферы канала адреса/данных (ВD/А); указатель команд (IР), выполняющий функции программного счетчика; сегментные регистры (RGS), содержащие базовые адреса программ, данных и стека; сумматор адреса (Sm), служащий для вычисления 20-разрядного физического адреса; регистры очереди команд (RI), предназначенные для формирования шестибайтной очереди команд, готовых к исполнению. Условное обозначение микропроцессора К1810ВМ86 представлено на рисунке 2.

Рисунок 2 — Условное обозначение микропроцессора К1810ВМ86

Отличительной особенностью архитектуры микропроцессора К1810ВМ86 является наличие двух основных асинхронно работающих устройств: устройства обработки (УО) и устройства сопряжения канала (УСК). УО декодирует и выполняет команды, а УСК осуществляет связь с внешними устройствами, обеспечивает выборку команд и данных из памяти, формирует очередь команд. Организация параллельной работы УО и УСК и уменьшение конфликтных ситуаций при обращении к памяти за счет применения очереди команд позволяет существенно повысить производительность систем на основе микропроцессора К1810ВМ86.

Микропроцессор

К1810ВМ86 предназначен для использования

как в простых однопроцессорных, так и

в сложных мультипроцессорных системах

управления и обработки информации. В

связи с этим МП имеет специальный вывод

![]() для задания минимального или максимального

режимов функционирования. Каждый

режим характеризуется некоторым набором

управляющих сигналов, соответствующим

сложности проектируемой системы.

При подключении вывода

для задания минимального или максимального

режимов функционирования. Каждый

режим характеризуется некоторым набором

управляющих сигналов, соответствующим

сложности проектируемой системы.

При подключении вывода

![]() к выводу UСС

микропроцессор настраивается на

работу в минимальном режиме, в котором

все сигналы управления периферийными

устройствами вырабатываются самим

МП. При подключении вывода

к выводу UСС

микропроцессор настраивается на

работу в минимальном режиме, в котором

все сигналы управления периферийными

устройствами вырабатываются самим

МП. При подключении вывода

![]() к выводу GND

происходит изменение функций ряда

управляющих сигналов и МП перенастраивается

на работу в максимальном режиме. В этом

режиме МП используется обычно с системным

контроллером, генерирующим сигналы

управления системой. Управляющие сигналы

максимального режима работы на рисунке

1 заключены в круглые скобки.

к выводу GND

происходит изменение функций ряда

управляющих сигналов и МП перенастраивается

на работу в максимальном режиме. В этом

режиме МП используется обычно с системным

контроллером, генерирующим сигналы

управления системой. Управляющие сигналы

максимального режима работы на рисунке

1 заключены в круглые скобки.

Назначения выводов МП и соответствующих им сигналов, общих как для максимального, так и для минимального режимов представлены в таблице 1.

Таблица 1 — Описание выводов МП, общих для максимального и минимального режимов

-

Обозначение

вывода

Номер

контакта

Назначение вывода

1

2

3

АD(15-0)

39; 2-16

Тристабильные входы/выходы канала, образующие адресную шину в такте обращения к памяти Т1 и шину данных в последующих тактах (Т2, Т3, Тw, Т4)

Продолжение таблицы 1

-

1

2

3

А19/SТ6;

А18/SТ5;

А17/SТ4;

А16/SТЗ

35-38

Тристабильные выходы, образующие четыре старших разряда адреса памяти в такте Т1 и сигналы состояния в последующих тактах: SТ5 — состояние триггера разрешения прерывания; SТ4 и SТЗ служат для указания используемого в цикле обмена сегментного регистра, SТ6 — сигнал L-уровня

ВНЕ/SТ7

34

Тристабильный выход, используемый для разрешения передачи данных по старшей половине шины АD(15-8) в такте Т1 по L-уровню сигнала ВНЕ и как сигнал состояния SТ7 в тактах T2, T3, T4

R

32

Тристабильный выход сигнала чтения L-уровня, используемого для считывания информации из устройств, подключенных к каналу МП, и выдаваемого в тактах Т2, Tз, Тw каждого цикла чтения

RDY

22

Вход сигнала готовности H-уровня, поступающего от внешних устройств и подтверждающего их готовность к обмену

INT

18

Вход маскируемого запроса прерывания H-уровня

NMI

17

Вход немаскируемого запроса прерывания (по положительному перепаду на входе)

TEST

23

Вход сигнала проверки, анализируемый специальной командой ожидания WAIТ

CLR

21

Вход сигнала установки внутренних схем МП

CLK

19

Вход тактовых сигналов синхронизации

33

Вход сигнала управления режимом работы МП

UСС

40

Напряжение питания ( + 5 В)

GND

1; 20

Напряжение питания (0 В)

Микропроцессор К1810ВМ86 осуществляет обмен информацией с ЗУ и ВУ через 16-разрядный канал адреса/данных с помощью временного мультиплексирования. Цикл функционирования канала включает обычно выдачу адресов ЗУ или УВВ, данных, а также сигналов, сопровождающих процесс обмена и состоит из четырех машинных тактов (Т1, Т2, Т3, Т4). В такте Т1 в канал выдается адрес ЗУ или УВВ. Обмен данных для цикла записи происходит в тактах Т2, Т3, Т4, а для цикла чтения – в тактах Т3, Т4. Такт Т2 в цикле чтения используется для переключения МП из режима записи в режим чтения, а канал переводится в высокоимпедансное состояние. Для согласования с медленными УВВ или ЗУ с помощью сигнала RDY между тактами Т3 и Т4 могут включаться дополнительные такты ожидания (Tw), в течение которых данные в канале остаются неизменными. Наконец, в ряде случаев между отдельными циклами канала могут вводиться холостые такты (T5).

Назначения выводов, относящиеся только к минимальному режиму представлены в таблице 2.

Таблица 2 — Описание выводов МП, используемых для минимального режима

-

Обозначение вывода

Номер контакта

Назначение вывода

1

2

3

W

29

Тристабильный выход сигнала записи L-уровня, используемого для записи информации в ЗУ или УВВ в зависимости от состояния сигнала

и

выдаваемого в тактах Т2, Т3 и Тw каждого

цикла записи

и

выдаваемого в тактах Т2, Т3 и Тw каждого

цикла записи

28

Тристабильный выход сигнала обращения к ЗУ или УВВ, вырабатываемого в такте предшествующего цикла и поддерживаемого до завершающего такта Т4 текущего цикла: L-уровень сигнала соответствует обращению к УВВ, а Н-уровень — обращению к ЗУ

27

Тристабильный выход передачи или приема данных, предназначенный для управления направлением обмена информацией через шинные формирователи

DE

26

Тристабильный выход сигнала разрешения передачи данных L-уровня, выдаваемый в каждом цикле обращения к ЗУ или УВВ и в циклах подтверждения прерывания

Продолжение таблицы 2

-

1

2

3

STB

25

Выход строба адреса — сигнал Н-уровня, используемого для записи адреса во внешний буферный регистр адреса и генерируемого в такте Т1 любого цикла канала

INTA

24

Выход сигнала подтверждения прерывания L-уровня, генерируемого в тактах Т2, Т3 и Тw, каждого цикла подтверждения прерывания

HLD

31

Выход сигнала захвата, указывающего на запрос канала другим процессором

HLDA

30

Выход сигнала подтверждения захвата, сопровождающегося переводом канала и шин управления в высокоимпедансное состояние

Назначения выводов, относящиеся только к максимальному режиму, представлены в таблице 3.

Таблица 3 — Описание выводов МП, используемых для максимального режима

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

ST0-ST2 |

26; 27; 28; |

Тристабильные выходы сигналов состояния цикла канала, генерируемых в тактах Т4, Т1 и Т2 и используемых контроллером канала для выработки сигналов управления обменом информации с ЗУ и УВВ

|

|

RQ/E1 RQ/E0 |

30; 31 |

Двунаправленные выводы сигналов запроса/разрешения доступа к магистрали, используемых другими устройствами, чтобы отключить МП от канала в конце текущего цикла канала; приоритет вывода RQ/E0 выше, чем вывода RQ/E1 |

|

LOCK |

29 |

Тристабильный выход сигнала блокировки системного канала, указывающего другим устройствам на запрет использования системного канала, пока сигнал LOCK имеет L-уровень |

|

QS1, QS0 |

24; 25 |

Выход сигналов состояния очереди команд |

В максимальном режиме МП использует лишь три вывода SТ0 — SТ2 для управления периферией и ЗУ через контроллер, а на остальных пяти выводах генерируются сигналы, необходимые для организации работы МП в мультипроцессорных системах.

Три 16-разрядных регистра очереди команд (RI) микропроцессора обеспечивают временное хранение 6 байт очереди команд. УО микропроцессора при выполнении команды извлекает из очереди байт кода команды, не требуя доступа к каналу. УСК микропроцессора следит за состоянием очереди команд, пополняя ее, когда другие системные элементы не занимают память. При выполнении команд передачи управления очередь сбрасывается и после завершения перехода в место передачи управления начинает заполняться вновь. В макси-мальном режиме МП передает информацию о состоянии очереди на выходы QS0 и QS1. Эта информация используется внешними процессорами.