Схемотехника / Учебники и методички / lect11_m5_vt_vt_aloiscevm_niy06

.pdfЛекция. Шифраторы

План лекции

1.Шифратор шестнадцатеричной клавиатуры.

2.Шифратор десятичной клавиатуры.

3.Приоритетные шифраторы.

3.1. Приоритетный шифратор как многофункциональный элемент.

Шифратором в цифровой технике называют комбинационный узел, преобразующий один из совокупности входных функционально однотипных однопозиционных кодов в двоичный код. Примерами таких совокупностей могут служить кнопки у клавиатур и пультов различного назначения, сигналы запросов на прерывание от внешних устройств, взаимодействующих с ЭВМ, угловые положения поворотных переключателей и т.п. Из данного определения следует, что шифратор выполняет микрооперацию обратную микрооперации дешифратора. Если m - число входных однопозиционных кодов, то минимальная разрядность n двоичного кода будет равна ближайшему большему целому от log2m.

1. Шифратор шестнадцатеричной клавиатуры

Клавиатура является одним из популярных и широко распространенных аппаратных средств для ввода данных в цифровую систему. Рассмотрим для примера структуру выполненного на логических элементах шифратора клавиатуры, предназначенной для ввода шестнадцатеричных чисел. Работу шифратора представим таблицей истинности (табл.1), где x3, x2, x1, x0 - переменные четырёхразрядного двоичного кода с весами соответственно 8, 4, 2, 1 (естественный двоичный код), z - осведомительный сигнал, который принимает значение 1 при нажатии любой клавиши и значение 0 при всех не нажатых клавишах. Сигнал такого типа принято обозначать специальным термином - сигналуниверсум. При z = 1 разрешается принимать для дальнейшей обработки двоичный код нажатой клавиши.

Примечание. Шестнадцатеричные цифры от 0 до 9 - это обычные десятичные числа, остальные шесть цифр обозначают большими латинскими буквами A, B, C, D, E, F. В общем случае для кодирования может быть применен произвольный двоичный код.

Таблица кодирования цифр на |

Таблица 1 |

||||||

|

|

||||||

шестнадцатеричной клавиатуре |

|

|

|

||||

Шестнадцатеричная |

x3 |

x2 |

x1 |

|

x0 |

z |

|

цифра |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

8 |

1 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

A |

1 |

0 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

B |

1 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

C |

1 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

D |

1 |

1 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

E |

1 |

1 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

F |

1 |

1 |

1 |

|

1 |

1 |

|

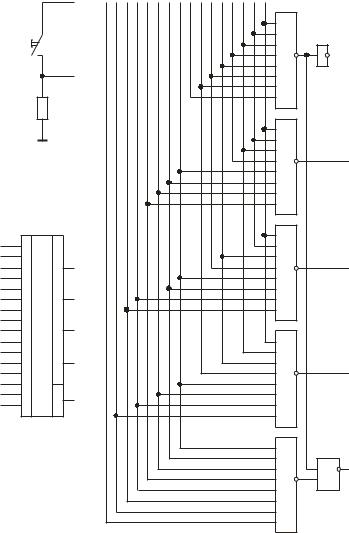

Допустим, что при нажатии какой-либо клавиши в соответствующей цепи формируется сигнал 1, а при не нажатой клавише - сигнал 0 (рис.3.1,а).

Для разряда x3 выходного двоичного кода можно записать выраже-

ние

x3 = 8 + 9 + A + B + C + D + E + F, |

(3.1) |

которое надо понимать следующим образом: в разряде x3 появится 1, если нажимается клавиша либо с цифрой 8, либо 9, либо А и т.д.

|

UИП |

0 1 2 3 4 5 6 7 8 9 A B C DE F |

|

|

1 |

Кн«0» |

|

|

|

0 |

|

|

R |

|

|

|

1 |

а |

|

|

0 CD |

|

1 |

|

|

|

1 |

8 |

|

2 |

|

|

3 |

|

|

4 |

4 |

|

5 |

|

|

6 |

|

|

7 |

2 |

|

8 |

1 |

|

9 |

|

|

A |

1 |

|

B |

|

|

C |

|

|

D |

|

|

E |

z |

|

F |

|

|

в |

|

1 |

|

|

|

|

|

б |

1 |

x3 |

|

x2 |

|

x1 |

|

x0 |

& |

z |

Рис.3.1. Шифратор цифр шестнадцатеричной клавиатуры:

а - схема включения одной кнопки (цифра «0»); б - схема шифратора на логических элементах; в - функциональное обозначение

Аналогично можно записать |

|

|

|

||

x2 |

= 4 + 5 + 6 |

+ 7 |

+ C + D + E + F, |

(3.2) |

|

x1 |

= 2 + 3 + 6 |

+ 7 |

+ A + B + E + F, |

(3.3) |

|

x0 |

= 1 + 3 + 5 |

+ 7 |

+ 9 |

+ B + D + F, |

(3.4) |

z = 0 + 1 + ... + 7 + 8 |

+ 9 + ... + F. |

(3.5) |

|||

Для реализации выражений (3.1) - (3.4) потребуется четыре восьмивходовых элемента ИЛИ, а для выражения (3.5) - один шестнадцативходовый. Пусть из соображений динамики, конструктивных требований или каких-либо других ограничений не допускается использовать логические элементы с числом входов больше восьми. Тогда выражение (3.5) можно преобразовать к следующему виду:

z (0 1 7) (8 9 F)

(3.6)

(0 1 7) (8 9 F),

откуда видно, что для реализации сигнала z потребуются два восьмивходовых элемента ИЛИ-НЕ и один двухвходовый элемент И-НЕ. Чтобы не использовать два восьмивходовых элемента: ИЛИ (3.1) и ИЛИ-НЕ с теми же переменными (3.6), реализуем уравнение (3.1) в виде

x3 8 9 F .

Тогда достаточно просто добавить инвертор, и схема шифратора будет иметь вид, показанный на рис.3.1,б.

По такой схеме шифратор реализован в виде р-МОП ИС КР501ИВ1 и КР501ИВ1П и в основном он используется в специализированных ЭВМ, пультах отладки и т.п. Функциональное обозначение его приведено на рис.3.1,в, где CD - coder - аббревиатура, принятая для обозначения шифраторов.

2. Шифратор десятичной клавиатуры

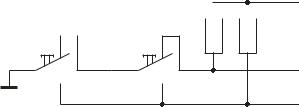

Учитывая возможность простой реализации ФАЛ на механических переключательных элементах, реализуем в качестве следующего примера шифратор десятичной клавиатуры (см. первые десять строк в табл.1) без логических элементов или хотя бы с их минимальным количеством. Предварительно рассмотрим простую схему, приведённую на рис.3.2.

Uип

R

R  R

R

x1 |

|

x0 |

y1 |

y2 |

Рис.3.2. Простая логическая схема с двумя выходами на переключателях

Примем, что положение переключателей, указанное на рис.3.2, соответствует значениям логических переменных x1 = x0 = 0, а выходные функции y1 и y2 кодируются в положительной логике, тогда для последних можно записать

y1 x1 x0 , |

(3.7) |

||||

y2 |

|

|

|

. |

|

x1 |

x0 |

(3.8) |

|||

Число переменных двоичного кода, кодирующего десятичные цифры, равно четырем. Запишем для них выражения, начиная с цифры 9

для удобства оформления схемы шифратора: |

|

||||

x3 |

= 9 |

+ 8, |

|

|

(3.9) |

x2 |

= 7 |

+ 6 |

+ 5 + 4, |

(3.10) |

|

x1 |

= 7 |

+ 6 |

+ 3 |

+ 2, |

(3.11) |

x0 |

= 9 |

+ 7 |

+ 5 |

+ 3 + 1. |

(3.12) |

Поскольку выражение (3.9) |

с точностью до замены переменных |

||||

совпадает с выражением (3.7), то переменная x3 реализуется так же, как y1 на рис.3.2. Переменная x2 реализуется аналогичной схемой, но число последовательно включенных переключателей в ней будет четыре. Переменная x1 также реализуется четырьмя переключателями, причём группа 7 + 6 в выражении (3.11) может использоваться из схемы, реализующей выражение (3.10). Анализ выражения (3.12) показывает, что

переменная x0 не может быть реализована так же, как x3, x2 и x1 без применения сдвоенных переключателей. Тогда запишем выражение для инверсного значения переменной x0:

x0 |

8 6 4 2 0 . |

(3.13) |

Проинвертируем левую и правую части выражения (3.13) и в правой части применим правило де-Моргана, тогда получим

x0 |

x0 |

|

8 6 4 2 0 |

|

8 |

|

6 |

|

4 |

|

2 |

|

0 |

. |

(3.14) |

Выражение (3.14) по структуре совпадает с формулой (3.8), следовательно, переменную x0 можно реализовать так же, как y2 на рис.3.2. Осведомительный сигнал z для шифратора десятичной клавиатуры реализуем как

z = (9 + 7 + 5 + 3 + 1) + (8 + 6 + 4 + 2 + 0). (3.15)

Применив к правой части выражения (3.15) закон двойного отрицания и правило де-Моргана, окончательно получим

z (9 7 5 3 1) (8 6 4 2 0)

(3.16)

(9 7 5 3 1) (8 6 4 2 0).

Так как в выражении (3.16) правая группа, заключенная в скобки, равна переменной x0, а левая группа также может быть реализована как функция y2 на рис.3.2, то для окончательного получения сигнала z дополнительно потребуется один двухвходовый логический элемент И-НЕ

(см. рис.3.3).

Следует отметить, что поскольку верхнее положение переключателей, соответствующих десятичным цифрам 1 и 0 не используется, нет необходимости применять резистор в этой цепи. Эти переключатели вообще могут быть заменены на выключатели, замыкаемые на цепь «Общий».

Структуры шифраторов, приведённые на рис.3.1 и рис.3.3, предна-

значены для обработки зависимых однопозиционных сигналов. Этот термин применительно к шифраторам клавиатуры обозначает, что из всех клавиш должна быть нажата только одна, как например в поворотном переключателе, который может находиться только в одном угловом положении. При нажатии нескольких клавиш на выходе шифратора получается код, соответствующий операции «поразрядное ИЛИ» над кодами отдельных клавиш. Так, при нажатии клавиш 5 и 9 (см. рис.3.1) на выходе получается двоичный код клавиши D. Такая ситуация в большинстве случаев неприемлема.

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

U ИП |

|

||||||||||

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

x3 |

|

|

|

|

|

|

|

|

|

|

x2 |

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

|

x0 |

|

|

|

|

|

|

|

|

|

& |

z |

Рис.3.3. Шифратор цифр десятичной клавиатуры на переключателях |

||||||||||

3. Приоритетные шифраторы

Если одновременно действуют несколько активных однопозиционных сигналов, то они называются независимыми. Типичным примером таких сигналов являются сигналы запросов на прерывание от внешних (периферийных) устройств, взаимодействующих с ЭВМ. Для обработки независимых однопозиционных кодов (сигналов) применяют приоритетные шифраторы. Это название связано с тем, что различным одновременно действующим сигналам присваивается приоритет. Например, в большинстве ЭВМ максимальным приоритетом обладает сигнал прерывания «Авария источника питания». После появления этого сигнала в распоряжении ЭВМ имеются только единицы миллисекунд, в течение которых она должна сохранить важнейшие данные на магнитных носителях или в другой энергонезависимой памяти.

Далее будем предполагать, что входные сигналы с большим индексом обладают большим приоритетом. Приоритетные шифраторы могут быть выполнены по двум структурам: 1) схема выделения старшего сигнала плюс обычный шифратор; 2) приоритетный шифратор как единое целое.

Схема выделения старшего сигнала имеет k входов и k выходов и работает по следующему алгоритму: из нескольких активных входных сигналов на выход этой схемы передается только один активный сигнал, имеющий максимальный приоритет, а все остальные активные сигналы с меньшим приоритетом передаются на выход как неактивные. Выделенный один активный сигнал далее легко может быть преобразован в двоичный код обычным шифратором.

Рассмотрим два примера. Пусть на входе схемы выделения старшего сигнала действуют четыре сигнала - в одном случае активным является уровень 1 (табл.2), а в другом - уровень 0 (табл.3). В таблицах xi - входные сигналы, а yi - выходные.

Таблица 2

Таблица истинности для схемы выделения старшего сигнала с активной единицей на входах и выходах

Номер |

x3 |

x2 |

x1 |

x0 |

y3 |

y2 |

y1 |

y0 |

набора |

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

6 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

7 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

9 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

10 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

11 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

12 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

13 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

14 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

15 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

Из табл.2 могут быть получены (например, с помощью карт Карно) следующие выражения:

y3 x3 ;

y2 |

x3 |

x2 x3 |

x2 |

; |

(3.17) |

y1 x3 x2 x1 x3 x2 x1 ;

y0 x3 x2 x1 x0 x3 x2 x1 x0

Таблица 3

Таблица истинности для схемы выделения старшего сигнала с активным нулём на входах и выходах

Номер |

x3 |

x2 |

x1 |

x0 |

y3 |

y2 |

y1 |

y0 |

набора |

|

|

|

0 |

|

|

|

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

2 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

3 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

5 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

6 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

8 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

9 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

10 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

11 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

12 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

13 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

14 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

15 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

и соответственно из табл.3: y3 x3 ;

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y2 |

x3 |

x2 x3 |

x2 |

; |

|

|

(3.18) |

||||||

|

|

|

|

|

|

|

|

|

|

||||

y1 |

|

|

|

|

x1 x3 x2 |

|

; |

|

|||||

x3 |

x2 |

x1 |

|

||||||||||

y0 x3 x2 x1 x0 x3 x2 x1 x0 .

Схемы, реализующие уравнения типа (3.17) и (3.18), называются дейзи-цепочками и широко используются для аппаратной обработки сигналов запроса на прерывание от периферийных устройств, взаимодействующих с ЭВМ.

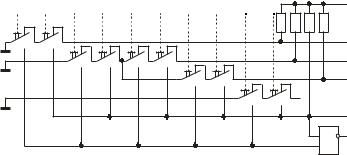

Рассмотрим структуру и функционирование приоритетного шифратора как единого целого. Функциональное обозначение таких ИС, обрабатывающих восемь входных сигналов, приведено на рис.3.4.

Прежде всего отметим, что все входы и выходы этой ИС имеют в качестве активного сигнала низкий уровень, т.е. логический нуль. На рис.3.4 I0,...,I7 - входные сигналы, причём сигнал с большим индексом имеет больший приоритет.

|

Вход EI (enable input |

|

|

|

|

|

|

|

||||

|

|

|

|

PRCD |

EO |

|

|

|||||

- разрешение |

по |

входу) |

|

|

I0 |

|

|

|||||

|

|

|

|

|

||||||||

при |

активном уровне |

0 |

|

|

I1 |

|

|

|

|

|||

|

|

|

GS |

|

|

|||||||

разрешает работу ИС, а |

|

|

I2 |

|

|

|

||||||

|

|

|

|

|

|

|||||||

при неактивном уровне 1 |

|

|

I3 |

|

|

|

|

|||||

формирует на всех выхо- |

|

|

|

|

|

|

||||||

|

|

I4 |

|

A0 |

|

|

||||||

дах неактивные уровни 1. |

|

|

|

|

|

|||||||

|

|

I5 |

|

|

|

|

||||||

Этот |

сигнал |

служит для |

|

|

|

|

|

|

||||

|

|

I6 |

|

A1 |

|

|

||||||

наращивания |

числа |

обра- |

|

|

|

|

|

|||||

|

|

|

|

|

||||||||

|

|

I7 |

|

|

|

|

||||||

батываемых |

информаци- |

|

|

|

A2 |

|

|

|||||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|||||||

онных входов. |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

EI |

|

||||||

|

Выход EO (enable |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||

output - разрешение |

по |

|

|

|

|

|

|

|

||||

Рис.3.4. Функциональное обозначение при- |

||||||||||||

выходу) также служит для |

||||||||||||

наращивания |

числа |

обра- |

оритетного шифратора «из 8-ми в 3» с ак- |

|||||||||

тивными нулями на входах и выходах |

||||||||||||

батываемых |

информаци- |

|||||||||||

|

|

|

|

|

|

|

||||||

онных входов, причём выход EO ИС, обрабатывающей сигналы, имеющие больший приоритет, соединяется со входом EI ИС, обрабатывающей сигналы, имеющие меньший приоритет. Если на входы ИС, обрабатывающей сигналы с большим приоритетом, не поступает ни одного активного сигнала, то значение выхода EO устанавливается равным 0 и тем самым разрешается обработка входных сигналов с меньшим приоритетом, поступающих на соответствующие ИС. Наличие одного любого активного сигнала на входах ИС, обрабатывающей сигналы с большим приоритетом, автоматически запирает все ИС, обрабатывающие сигналы с меньшим приоритетом.

Выход GS (group signal - групповой сигнал) принимает активное значение 0, если на входах данной ИС имеется хотя бы один активный сигнал, т.е. GS выполняет функцию осведомительного сигнала о том, что на входах приоритетного шифратора есть хотя бы один активный сигнал. На выходе GS формируется неактивная 1, когда на выбранной (разрешенной к работе) ИС нет ни одного активного входа.

На выходах A2, A1 и A0 формируется адрес входного направления, имеющего активный сигнал с максимальным приоритетом (в обратном коде!).

Исходя из сказанного, можно оформить таблицу (табл.4), иллюстрирующую работу такого приоритетного шифратора, где крестиком обозначены безразличные значения сигналов.