Схемотехника / Учебники и методички / lab_m3_vt_vt_aloiscevm_niy06

.pdfАрифметико-логические основы

исхемотехника электронных вычислительных машин

Лабораторный практикум

«Регистры»

для подготовки бакалавров по ООП НИУ по направлению 230100.62 "Информатика и вычислительная техника" (факультет МПиТК),

Профиль "Элементы и устройства микропроцессорных ин- формационно-управляющих систем"

1

Лабораторная работа «Регистры»

Цель работы: изучить виды и состав регистров; овладеть методами синтеза регистровых структур на базе современных типов триггеров и регистров; приобрести навыки в создании, отладке и экспериментальном исследовании регистровых структур в среде MAX+PLUS II.

Продолжительность работы - 4 часа.

Лабораторное задание

1. Ознакомить с правилами техники безопасности в учебном каби-

нете.

2.Выполнить синтез структур, заданных в индивидуальном задании, построить временные диаграммы работы.

3.Получить допуск к лабораторной работе, показав преподавателю выполненные задания и ответив на вопросы теоретической части.

Краткие теоретические сведения на примере выполнения индивидуального задания

1.Используя сдвиговый регистр на JK-триггерах, разработать самовосстанавливающийся делитель частоты на 13.

2.Используя D-триггеры, разработать 4-разрядный регистр, выполняющий микрооперации:

-приём данных ( Qit 1 xit );

-логическое «И» ( Qit 1 Qit xit );

-«счётный режим» ( Qit 1 Qit ).

Порядок выполнения работы

Используя сдвиговый регистр на JK-триггерах, разработаем самовосстанавливающийся делитель частоты на 13.

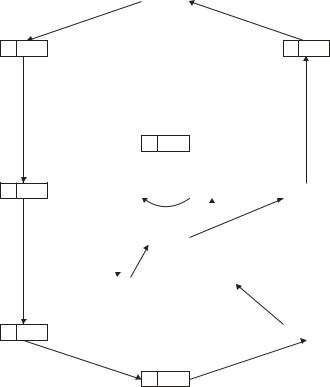

Для синтеза делителя частоты с использованием сдвигового регистра на JK-триггере необходимо выделить на графе переходов (рис.1)

2

замкнутый контур, содержащий столько вершин, на какое число необходимо синтезировать делитель частоты. В нашем - случае контур с 13 вершинами (13 переходов). Один из возможных контуров изображён на рис.2.

0

|

|

|

1 |

|

|

|

0 |

0000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

1 |

|

|

|

|

1 |

0001 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

0 |

|

|

|

|

|

|

0 |

||

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

1 |

|

2 |

0010 |

|

4 |

0100 |

|

|||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

1 |

|

9 |

1001 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

0 |

|

|

1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

0011 |

|

5 |

0101 |

|

1 |

10 |

1010 |

|

|||

|

|

|

0 |

|

|

|

|

|

0 |

|||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

6 |

0110 |

|

|

0 |

|

|

|

1 |

|

|

|

0 |

|

1 |

|

|

||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

11 |

1011 |

|

13 |

1101 |

1 |

|||

|

|

|

|

0 |

||||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

0111 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

1 |

|

|

|

|

|

0 |

|

||

|

|

|

|

|

|

|

15 |

1111 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

8 1000

0

121100

0

14 1110

14 1110

Рис.1. Полный граф переходов 4-разрядного сдвигового регистра

3

1 0001

1

30011

1

7 0111

1 |

0 |

0000 |

|

|

0 |

||

|

|

||

8 1000

2 |

0010 |

|

4 |

0100 |

0

9 1001

5 |

0101 |

|

1 |

10 |

1010 |

|

12 |

1100 |

||

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

6 |

0110 |

|

|

0 |

|

|

|

|

|

0 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

1011 |

|

|

13 |

1101 |

1 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

1110 |

1 |

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

15 |

1111 |

|

|

|

|

|

|

Рис.2. Замкнутый путь из 13 вершин на графе переходов

Если сдвиговый регистр, реализующий выбранный цикл, в исходном состоянии находится в какой-либо вершине графа, то ровно за 13 тактов он вернётся в эту же вершину. Поведение сдвигового регистра полностью определяется состоянием самого младшего триггера, поэтому после выбора маршрута на графе переходов необходимо задать логику работы для входов младшего триггера сдвигового регистра.

Воспользуемся характеристической таблицей для JK-триггера (табл.1). Используя её, заполним таблицу переходов (табл.2). Согласно выбранному маршруту, показанному на рис.2, сдвиговый регистр из состояния «0» (0000) должен перейти в состояние «1» (0001), следовательно, младший триггер должен принять значение Q0t+1 = 1. Из характеристической таблицы видно, что для перехода 0 → 1, входы J0K0

4

должны принять значения «1» и «×» соответственно, что и записано в табл.2 в строчке с номером набора «0».

Таблица 1

Характеристическая таблица JK-триггера

Qt → Qt+1 |

J0 |

K0 |

|

0 |

0 |

0 |

× |

0 |

1 |

1 |

× |

1 |

0 |

× |

1 |

1 |

1 |

× |

0 |

C: 1 → 0 |

|

|

|

Таблица 2

Таблица переходов для младшего JK-триггера сдвигового регистра

Номер |

Q3 |

Q2 |

Q1 |

Q0 |

|

Q0t+1 |

J0 |

K0 |

набора |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

× |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

× |

0 |

3 |

0 |

0 |

1 |

1 |

|

1 |

× |

0 |

7 |

0 |

1 |

1 |

1 |

|

1 |

× |

0 |

15 |

1 |

1 |

1 |

1 |

|

0 |

× |

1 |

14 |

1 |

1 |

1 |

0 |

|

1 |

1 |

× |

13 |

1 |

1 |

0 |

1 |

|

0 |

× |

1 |

10 |

1 |

0 |

1 |

0 |

|

1 |

1 |

× |

5 |

0 |

1 |

0 |

1 |

|

1 |

× |

0 |

11 |

1 |

0 |

1 |

1 |

|

0 |

× |

1 |

6 |

0 |

1 |

1 |

0 |

|

0 |

0 |

× |

12 |

1 |

1 |

0 |

0 |

|

0 |

0 |

× |

8 |

1 |

0 |

0 |

0 |

|

0 |

0 |

× |

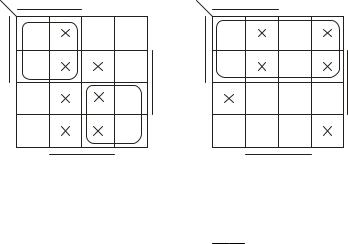

Перенесём J0 и K0 на карты Карно с целью минимизации функций алгебры логики J0 и K0. Выбираем покрытия, показанные на рис.3.

5

J0 |

Q1 |

|

K0 |

Q1 |

|

|

|

|

|

|

|

||

1 |

- |

0 |

1 |

|

- |

|

Q3 |

|

|

Q3 |

|

|

|

1 |

|

0 |

1 |

|

1 |

|

|

|

Q2 |

|

|

|

Q2 |

0 |

|

- |

|

0 |

0 |

- |

- |

|

1 |

- |

0 |

0 |

|

|

Q0 |

|

|

Q0 |

|

|

|

а |

|

|

|

б |

|

|

Рис.3. Карты Карно: а - для J0; б - для K0 |

|

|

|||

В результате минимизации получаем:

J0 Q3Q1 Q3 Q1 ;

K0 Q3 .

Теперь, когда выбраны покрытия, определяющие значения входов J0 и K0 на всех наборах, включая нерабочие, следует выполнить проверку, подтверждающую, что сдвиговый регистр является самовосстанавливающимся, т.е. за конечное число тактов он войдёт в рабочий цикл. Так как в нашем рабочем цикле использует 13 различных состояний из 16 возможных, необходимо проверить оставшиеся 16–13 = 3 нерабочих состояния: «2», «4» и «9».

Начнём с состояния «2». Так как клетка с номером набора «2» не попала ни в один из контуров в покрытиях карт Карно на рис.3, то состояния сигналов J0 и K0 на этом наборе доопределились до J0 = «0» и K0 = «0». По определению работы JK-триггера [2], если на входы J, K подать комбинацию «0», «0», то он сохранит своё значение выхода. В наборе «2» (0010) Q0 принимает значение логического «0», значит, после перехода в новое состояние он также должен принять значение логического «0». Из графа переходов на рис.1 видно, что это соответствует переходу из вершины «2» в вершину «4», которая также является нерабочей.

Рассуждая аналогично, для «4» состояния видим, что на этом наборе J0 и K0 доопределились до J0 = «1» и K0 = «0» это приведёт к тому, что выход триггера установится в логическую «1». Это соответствует переходу из вершины «4» в «9», которая тоже не является рабочей.

6

K0 |

В вершине «9» входы J0 и |

K0 |

доопределились до J0 = «0» и |

||||||

= «1». Это означает сброс младшего триггера после прихода тактово- |

|||||||||

го импульса. Это обеспечит переход из вершины «9» в вершину «2». |

|||||||||

|

В итоге получился паразитный цикл, показанный на рис.4. |

||||||||

|

Состояние “2” |

0 |

0 |

1 |

0 |

|

0 |

||

|

|

||||||||

|

|

||||||||

|

Состояние “4” |

0 |

1 |

0 |

0 |

|

|

1 |

|

|

|

||||||||

|

|

||||||||

|

Состояние “9” |

1 |

0 |

0 |

1 |

|

0 |

||

|

|

||||||||

|

|

||||||||

|

Состояние “2” |

0 |

0 |

1 |

0 |

|

|

|

|

|

Рис.4. Паразитный цикл, приводящий к |

||||||||

неработоспособности делителя частоты

Подобное состояние эквивалентно отказу, поэтому необходимо скорректировать логику работы сдвигового регистра так, чтобы обеспечить вход в рабочий цикл. Для этого скорректируем цикл так, чтобы, например, из состояния «9» произошёл переход в состояние «3», которое является рабочим (рис.5). В связи с этим, измененим в карты Карно для набора номер «9», внеся туда комбинацию ×,0. В результате изменений выбираем новые покрытий для функций J0 и K0 (рис.6).

Состояние “2” |

0 |

0 |

1 |

0 |

|

0 |

||

|

||||||||

|

||||||||

Состояние “4” |

0 |

1 |

0 |

0 |

|

|

1 |

|

|

||||||||

|

||||||||

Состояние “9” |

1 |

0 |

0 |

1 |

|

1 |

||

|

||||||||

|

||||||||

Состояние “3” |

0 |

0 |

1 |

1 |

|

|

|

|

Рис.5. Скорректированная логика работы сдвигового регистра

Избавившись от паразитных циклов, получаем окончательные выражения для информационных входов младшего триггера сдвигового регистра:

J0 Q3Q1 Q3 Q1 ;

K0 Q3Q1 Q3Q2 .

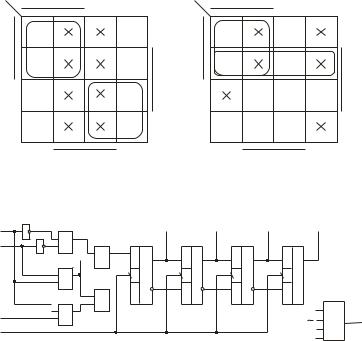

Следует помнить, что делитель частоты - это двухполюсник, у которого есть вход (ТИ) и выход. На выходе делителя частоты должны появляться переходы в 13 раз реже, чем на входе (делитель частоты на 13). Для синтеза функции выхода достаточно сформировать осведомительный сигнал о том, что сдвиговый регистр находится в каком-либо наборе из рабочего цикла. Выберем для этого, например, набор номер

«11» (10112). Очевидно, что Fвых Q3Q2Q1Q0 принимает значение

логической «1» только на «11» наборе. Таким образом, окончательная схема делителя частоты показана на рис.7.

7

J0 |

|

Q1 |

|

K0 |

Q1 |

|

|

|

|

1 |

|

0 |

1 |

|

0 |

|

|

Q3 |

|

|

|

Q3 |

|

|

|

|

|

1 |

|

0 |

1 |

|

1 |

|

|

|

|

|

Q2 |

|

|

|

|

Q2 |

|

0 |

|

- |

|

0 |

0 |

- |

|

|

- |

|

1 |

- |

0 |

0 |

|

|

|

|

Q0 |

|

|

Q0 |

|

|

|

|

|

а |

|

|

б |

|

|

|

|

Рис.6. Модифицированные карты Карно: а - для J0; б - для K0 |

|

||||||

Q |

1 |

|

Q0 |

Q1 |

Q2 |

Q3 |

|

|

3 |

& |

|

|

|

|

|

|

|

Q1 |

1 |

J* J TT |

J TT |

J TT |

J TT |

|

|

|

|

1 |

|

|

|||||

|

|

& |

C |

C |

C |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

K |

K |

K |

K |

|

|

|

|

K* |

|

|

Q3 |

& |

|

|

Q2 |

|

& |

|

|

|

Q2 |

Fвых |

|

|

|

|

|

|

||||

Т.И. |

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

Рис.7. Делитель частоты на D-триггерах |

|

|

|

|||

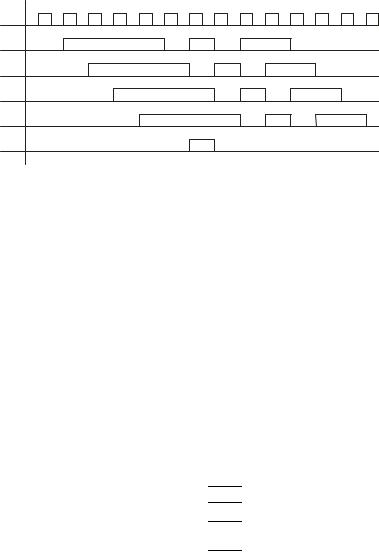

Временная диаграмма работы делителя частоты показана на рис.8. На ней основными сигналами являются ТИ (входной сигнал) и Fвых (выходной сигнал). Необязательные сигналы Q3, Q2, Q1, Q0 представлены для пояснения работы сдвигового регистра.

8

Т.И.

Q0

Q1

Q2

Q3

Fвых

Рис.8. Временная диаграмма работы делителя частоты

Используя D-триггеры, разработаем 4-разрядный параллельный регистр, выполняющий микрооперации:

-приём данных;

-логическое «И»;

-«счётный режим».

Разрабатываемый регистр должен знать, какая операция выполняется в тот или иной момент. Для этого введём дополнительные сигналы A1, A0, которые однозначно зададут режим работы. Двух сигналов достаточно, чтобы задать 4 операции. В нашем случае операций 3, поэтому одна из комбинаций будет не определена. Способ кодирования микроопераций показан в табл.3. В общем случае порядок операций в таблице может быть произвольным.

|

|

|

|

|

|

Таблица 3 |

|

Кодирование микроопераций |

|

|

|

||||

|

|

|

|

|

|

|

|

Микрооперация |

A1 |

A0 |

|

|

Примечание |

||

|

|

0 |

|

|

|

|

|

Хранение данных |

0 |

|

|

Qt+1 = Qt |

|||

Лог. «И» |

0 |

1 |

|

|

Qt+1 = Xt ·Qt |

||

|

|

|

|

|

Qt 1 |

|

|

«Счётный режим» |

1 |

0 |

|

|

Qt |

|

|

- |

1 |

1 |

|

|

Не определена |

||

Для создания 4-разрядного регистра достаточно спроектировать один разряд, оформить его в виде отдельного компонента и продубли-

9

ровать его на одной схеме 4 раза. Поэтому дальнейшие рассуждения будут вестись касательно одного разряда регистра. Заполним таблицу переходов одного разряда (табл.4). A1, A0 - входы, задающие микрооперацию, Q - выход регистра, X - входные данные регистра (все двухместные операции выполняются между X и Q). Левая половина таблицы до двойной черты заполняется простым перебором всех возможных значений. Правая часть заполняется с использованием таблицы микроопераций табл.3. Сначала заполним столбец «Микрооперация», в соответствии с ним заносятся правильные значения в столбец Qt+1, он же будет входом D*. Там, где операция не определена, ставится знак «×» - безразличное состояние, которое при минимизации функции доопределится до значений «1» или «0».

|

|

|

|

|

|

|

|

Таблица 4 |

|

|

Таблица переходов одного разряда регистра |

||||||||

|

|

|

|

|

|

|

|

|

|

Номер |

A1 |

A0 |

Xit |

Qit |

|

Qit 1 |

|

Микрооперация |

|

набора |

|

|

|

|

* |

|

|

|

|

|

|

|

|

|

|

Di |

|

|

|

0 |

0 |

0 |

0 |

0 |

|

0 |

|

Хранение данных: |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

|

||

|

|

|

|

|

|

|

|

Qt+1 = Qit |

|

2 |

0 |

0 |

1 |

0 |

0 |

|

|||

3 |

0 |

0 |

1 |

1 |

|

1 |

|

|

|

4 |

0 |

1 |

0 |

0 |

|

0 |

|

лог. «И»: |

|

5 |

0 |

1 |

0 |

1 |

|

0 |

|

||

6 |

0 |

1 |

1 |

0 |

|

0 |

|

Qit 1 = Xit *Qit |

|

7 |

0 |

1 |

1 |

1 |

|

1 |

|

|

|

8 |

1 |

0 |

0 |

0 |

|

1 |

|

«счётный режим»: |

|

9 |

1 |

0 |

0 |

1 |

|

0 |

|

||

10 |

1 |

0 |

1 |

0 |

|

1 |

|

Qit 1 =Qit |

|

11 |

1 |

0 |

1 |

1 |

|

0 |

|

|

|

12 |

1 |

1 |

0 |

0 |

|

× |

|

|

|

13 |

1 |

1 |

0 |

1 |

|

× |

|

Не определена |

|

14 |

1 |

1 |

1 |

0 |

× |

|

|||

|

|

|

|||||||

15 |

1 |

1 |

1 |

1 |

|

× |

|

|

|

Переносим табл. 4 на карту Карно и минимизируем функцию D* (рис.9). Выбранные покрытия доопределяют неопределённые состояния «×» до логической «1», если «×» попало хотя бы в один контур, до логического «0», если «×» не попало ни в один контур.

10