Avdeev

.pdf

41

задатчиком (имеют три состояния и активный высокий уровень). Для доступа к портам используются биты А0–А9 (в пределах материнской платы) или А0–А15. Двунаправленные линии D0–D15 образуют шину данных. Каждая линия Di имеет три состояния: высокий (активный) уровень, низкий (пассивный) уровень и выключено. Сигналразрешенияадреса(AEN)устанавливаетсяконтроллером ПДП. Низкийуровень этого сигнала указывает на обычный ввод–вывод (обращение к портам), а высокий уровень – на выполнение циклов ПДП и запрещает декодирование адреса порта адаптера ПУ. Сигналы MEMR , MEMW, IOR, IOW (с активным низким уровнем) управляют операциями чтения и записи данных в ячейки памяти и порты адаптера ПУ. Сигнал «готовность канала ввода–вывода» (I/O CH RDY) устанавливается источником и служит для согласования работы "медленных" ПУ с П. Низкий уровень этого сигнала удлиняет цикл шины ISA (П выполняет такты ожидания). Сигнал RESET (сброс) устанавливается П после включения источника питанияислужитдляпереводаресурсов ПК висходное(начальное)состояние.Сигналы системной частоты 8МГц (CLK) могут быть использованы платами адаптеров ПУ. Все циклы шины пропорциональны CLK.

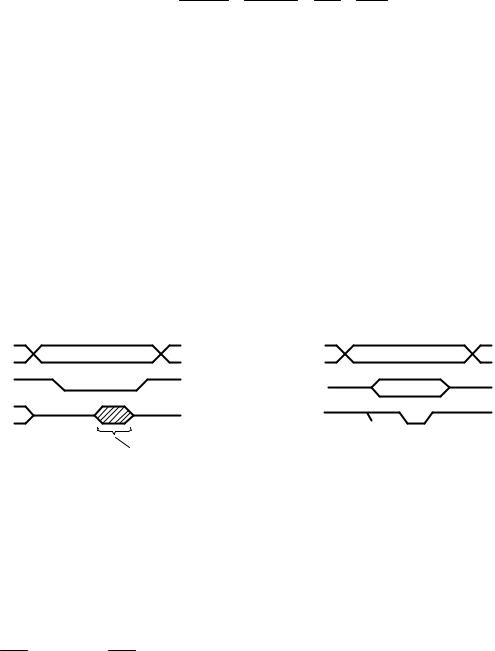

Рассмотрим временные диаграммы обычных циклов чтения и записи данных для 8–разрядных портов ввода–вывода (рис. 2.7 и рис. 2.8).

Адрес |

|

A0 - A15 |

Адрес |

A0 - A15 |

||||||||||||||

(A0 - A9) |

(A0 - A9) |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Чтение |

|

|

|

|

Данные |

|

D0 - D7 |

|||||||||||

|

IOR |

|||||||||||||||||

Данные |

|

|

D0 - D7 |

Запись |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

IOW |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

момент выдачи |

достоверные данные, |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

момент |

|

|

|

||||||||||

данных портом |

принимаемые П |

|

|

|

|

|

записи |

|

|

|

||||||||

Рис. 2.7. |

Чтение данных |

Рис. 2.8. Запись данных |

||||||||||||||||

Шинный цикл чтения данных реализуется каждый раз когда П |

выполняет |

|||||||||||||||||

команду IN (Ввод). |

Если адаптер ПУ декодировал собственный адрес А0–А15 |

|||||||||||||||||

или А0–А9 (с учетом сигнала AEN=0), то с появлением сигнала |

|

|

он выдает |

|||||||||||||||

IOR |

||||||||||||||||||

данные на шину D0–D7. Затем П считывает данные с шины D0–D7 |

до снятия |

|||||||||||||||||

сигнала IOR и линия IOR переводится в пассивное состояние (высокий уровень). Шинный цикл записи инициируется при выполнении П команды OUT (Вывод). П

42

устанавливает адрес и данные на шины А0–А15 (А0–А9) и D0–D7. Затем П формирует низкий активный уровень сигнала IOW, сообщающий адаптеру, опознавшему свой адрес с учетом сигнала AEN=0, о том, что ему следует записать информацию с шины D0–D7. Данные гарантированно установлены за 32 нс до снятия сигнала IOW и за 22 нс до появления сигнала IOW. Когда адаптер обнаруживает свой адрес, он записывает данные с шины D0–D7 в свой порт по спаду (снятию) сигнала IOW. Адрес устанавливается за 91 нс до появления сигнала IOW (IOR ). Это время отводится на компенсацию эффекта гонок сигналов по линиям шины адресаидекодированияадреса.Структурнаясхемаподключениядвух портовадаптера ПУ к шине ISA мало чем отличается от структурной схемы (см. рис. 2.3).

На рис. 2.9 изображена структурная схема подключения регистров РВв и РВыв к шине ISA.

ША |

A0 - A9 |

AEN |

ШУ |

IOR

IOW

|

|

ШД |

|

|

|

в ПУ |

|

из ПУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

ПП |

7 |

0 |

7 |

0 |

|

|

|

|

|

РВыв |

|

РВв |

|

ДшА |

ВыбПУ |

D0 - D7 |

В |

A |

BD0 - BD7 |

|

|

|

|

|

|

Т |

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

|

ЧтРДВв |

ДшУС |

ЗпРДВыв |

Рис. 2.9. Структурная схема подключения РВв и РВыв к шине ISA

Работа схемы описывается в соответствии с временными диаграммами (см. рис. 2.7 и 2.8) и аналогична принципу работы схемы (см. рис. 2.3) Следует обратить внимание, что в схеме запись в РВыв осуществляется по снятию сигнала IOW, логическая 1 на шине ISA представлена высоким активным уровнем, выходы регистра РВв с тремя состояниями и ПП не инвертирует сигналы данных. В качестве ПП можно использовать микросхемы 580 ВА86, 1533 АП6 и т.д. На рис. 2.10 представлены сигналы управления ПП.

D0

D1

D7

IOR

ВыбПУ

1533 АП6

BD

|

B0 |

A0 |

|

||

|

B1 |

A1 |

|

||

. . . . . . |

.. . |

|

|

B7 |

A7 |

|

||

|

DIR |

|

|

|

|

|

OE |

|

|

|

|

43

BD0

BD1

... BD7

Рис. 2.10. Сигналы управления ПП

Интерфейсный сигнал I/O CH RDY не следует путать с сигналом квитирования (например, с XACK) и сигналом готовности принтера к приему следующего символа (ACK или BUSY). Сигнал квитирования XACK обязательно вырабатывается исполнителем после каждого обращения к порту. Этот сигнал указывает на завершение операции записи или чтения на интерфейсе. Кроме того, сигнал XACK может быть использован и для согласования с "медленными" ПУ, как и сигнал I/O CH RDY, который является необязательным для "быстрых" ПУ. Время ожидания активного уровня сигнала I/O CH RDY (XACK) задатчиком на интерфейсе занимает не больше 10 машинных тактов. Появление сигнала готовности принтера в П занимает гораздо большее время, так как работа принтера связана с его механикой. На рис. 2.11 показана принципиальная схема формирования I/O CH RDY (XACK) при сопряжении с "медленным" ПУ.

|

|

|

|

|

531 ИР11 |

|

|

|

|

1533 ЛН1 |

5B |

R=1,8 k |

D |

RG |

|

|

|

|

|

D + |

|

|

|

|||

|

CLK |

1 |

|

|

C |

|

|

|

|

|

|

|

1 |

|

|

||

|

|

|

|

|

D1 |

|

|

|

|

1533 ЛП8 1533 ЛЛ1 |

|

D2 |

2 |

1533 ЛП8 |

|

||

MEMR |

1533 ЛА3 |

D3 |

3 |

I/O CH RDY |

||||

|

1 |

1 |

|

& |

D4 |

4 |

1 |

|

MEMW |

|

|

|

R |

|

|

||

1 |

1 |

|

|

|

|

|||

|

|

|

V1 |

|

|

|

||

|

|

|

|

|

V2 |

|

|

|

|

ВыбПУ |

|

|

|

1533 ЛН1 |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

Рис. 2.11. Принципиальная схема формирования I/O CH RDY |

|||||||

44

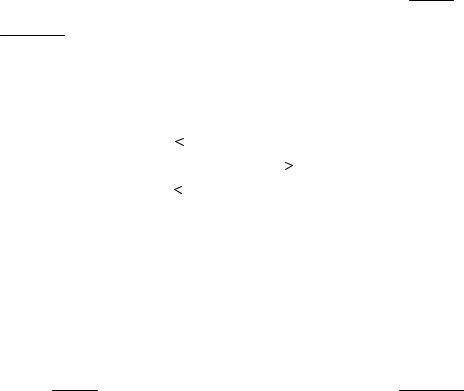

Для захвата шины ISA внешней платой (задатчиком (З)) используются интерфейсные сигналы : запрос ПДП (DRQi ), разрешение ПДП ( i ) и сигнал ведущий (MASTER ). На рис. 2.12 представлена схема связи контроллера ПДП материнской платы и внешней платы для реализации цикла захвата шины.

|

|

|

DRQi |

|

|||

Контроллер |

Внешняя |

||||||

|

|

|

i |

||||

DACK |

|||||||

ПДП |

|

|

|

плата (З) |

|||

|

|

|

|

|

|||

|

MASTER |

||||||

|

|

|

|

|

|

|

|

Рис. 2.12. Схема связи контроллера ПДП и внешней платы (З)

В этом режиме внешняя плата устанавливает сигнал DRQi , поступающий в резервный i–й канал контроллера ПДП, предварительно запрограммированного для каскадного соединения. Контроллер ПДП выполняет процедуру арбитража и осуществляет захват шины ISA. После этого контроллер ПДП устанавливает сигнал разрешения DACK i , а внешняя плата – ответный сигнал MASTER , заканчивающий процедуру захвата шины.

При работе с устройствами ввода/вывода шина ISA реализует режим доступа к 16или 8-битному исполнителю (16или 8-битной внешней плате). Эти режимы имеют различные временные характеристики интерфейсных сигналов. При разработке дешифратора адреса 16или 8-битной внешней платы необходимо учитывать минимальное время установки сигнала –IOR после вывода битов адреса, равное 91 нс. За это время с учетом распространения сигналов по адресной шине следует успеть опознать (декодировать) адрес контроллера. Минимальная длительность сигнала –IOW (-IOR) 8-битного исполнителя – 519 нс, а 16-битного исполнителя – 176 нс. Кроме того, важным временным соотношением является минимальное (гарантированное) время удержания данных после снятия сигнала –IOW, которое для 8-бит- ного исполнителя соответствует 185 нс [5]. Время появления переднего фронта сигнала –IOW не является стандартным для разных моделей компьютеров и критическим, так как запись данных в порт исполнителя происходит по заднему фронту сиг-

нала –IOW.

45

Приобработкеилиформированииинтерфейсныхсигналовисполнителемследует учитывать временные задержки применяемых микросхем (приемников) серии КР1533 (SN74ALS), К555 (SN74LS) и КР1554 (74AC), которые имеют следующие соответствующие пороговые величины: 15 нс, 20 нс и 10 нс. Временная задержка приемопередатчика КР580ВА86 равна 30 нс, КР559ИП13 – 18 нс и КР1533АП6 – 10 нс.

Стандарт шины ISA предъявляет следующие требования к электрическим характеристикам передатчиков, приемников и микросхем, подключаемых к линиям этой шины. Выходной ток низкого уровня передатчиков должен быть не менее 24 мА. Входной ток низкого уровня приемников (микросхемы) необходим не более 0.8 мА. Этим требованиям удовлетворяют входы микросхем серии КР1533 (SN74), КР1554 (74AC), входы/выходы А и В приемопередатчиков КР1533АП6, входы/выходы В КР580ВА86 (КР580ВА87), входы/выходы В КР559ИП3, входы/выходы В КР589АП16, выходы передатчиков 1533АП5, К555АП4 и т.д. Например, приемопередатчик КР1533АП6 имеет входные/выходные токи низкого уровня шин А и В соответственно 0.1/30 мА, которые удовлетворяют требованиям электрических характеристик шин ISA. У микросхемы КР580ВА86 токи низкого уровня входов/выходов В соответствуют требованиям стандарта (0.2/32 мА), а токи низкого уровня входов/выходов А – нет (0.2/16 мА). Поэтому входы/выходы В КР580ВА86 подключаются всегда к линиям данных шины ISA. При использовании микросхем серии К555 для подключения к линиям шины ISA рекомендуют использовать специальные (интерфейсные) схемы приемников, передатчиков и приемопередатчиков с целью буферизации сигналов магистрали. Кроме того, длина печатного проводника от контакта разъема до вывода микросхемы не должна быть больше 65 мм и емкость любого контакта разъема относительно земли не должна превышать 20 пФ.

2.3. Системная шина EISA

Системная шина EISA (расширенная промышленная стандартная архитектура) была разработана группой фирм (Compaq, Epson, AST, NEC и т.д.) и ее основной особенностью является то, что она является совместимой с шиной ISA. Совместимость двух шин конструктивно достигается тем, что используется специальный разъем (слот), в котором верхний ряд контактов соответствует шине ISA, а нижний

46

ряд контактов – шине EISA. Благодаря новым функциональным и параметрическим возможностям, шина EISA используется в высокопроизводительных системах, например, в серверах.

По сравнению с шиной ISA в шине EISA используются:

32 – битная шина данных и 32 – битная шина адреса;

централизованный системный арбитр с фиксированным или циклическим приоритетом, обеспечивающий приоритетный доступ к шине задатчиков, процессоров, устройств ПДП с помощью контроллера ПДП и контроллера регенерации динамической памяти;

расширенная подсистема ПДП с 8-, 16- и 32-битными передачами данных со скоростью до 33 Мбайт в секунду;

радиальный способ выбора каждого слота внешних плат, что позволяет реализовать режим автоконфигурации компонентов системы;

линии прерывания с сигналами запросов, действующих по фронту или по уровню (линия запроса по уровню позволяет подключить несколько устройств);

различные режимы передачи данных (стандартный, пакетный и сжатый). Режимы передачи данных определяют соответствующие структуры данных, указанные в морфологической графе классификации интерфейсов.

Таким образом, шина EISA продолжает традиционный путь развития системных интерфейсов: увеличение числа линий связи (линий данных, адреса и управления), расширение функций арбитража, ПДП, прерывания и реализацию режима автоконфигурации (технологии Plug & Play, чтобы исключить конфликт ресурсов на главной ЭВМ и использование перемычек (переключателей) для настройки системы на этапе ее инициализации).

Рассмотрим назначение дополнительных к шине ISA следующих сигналов:

AENi (i = 0, 1, …, 15). Сигнал разрешения адреса, используемый для выбора i-го слота на системной плате (каждая i-ая радиальная линия связана с контактом AENi слота). С помощью этого сигнала осуществляется выбор требуемой внешней платы во время автоконфигурирования системы;

47

(BE3 – BE0)#. Сигналы разрешения байтов (формируемые процессором) низкими активными уровнями определяют в текущем цикле используемые байты на 32-битной шине данных, например, BE0# = 0 указывает на байт D0-D7, а BE3# = 0 – на байт D31D24;

CMD#. Сигнал строба окончания команды, устанавливаемый процессором и применяемый вместе с сигналом START# для выполнения сжатых циклов на шине. Этот сигнал формируется по положительному сигналу BCLK, если сброшен сигнал START#, и удерживается до конца цикла шины;

EXRDY. Сигнал готовности исполнителя EISA, указывающий на завершение цикла передачи данных. Отсутствие этого сигнала на соответствующемвходезадатчикавызываетвегоработепоявлениетактовожидания;

EX32# и EX16#. Сигналы, соответственно, 32-битного и 16-битного исполнителей EISA, которые вырабатываются в начале цикла шины. Сигналы EX32# и EX16# анализируются 32-битным задатчиком с целью организации дополнительных циклов на шине в случае необходимости. Еслиуказанныесигналынеустановленынашине,то задатчик определяет это как наличие 8-битного исполнителя и организует четыре цикла на шине для передачи 32-битных данных. Для 8- и 16-битных исполнителей сигнал EX32# задатчика указывает исполнителям о завершении обмена данными;

LOCK# (Блокировка). Сигнал длительностью не более 8 мкс, устанавливаемый задатчиком при получении исключительного доступа к шине при обращении к памяти или устройству ввода-вывода;

MREQi# (Запрос от i-го задатчика). Сигнал задатчика, поступающий на соответствующий вход системного арбитра, синхронизируется BCLK и сохраняется до прихода MACKi#.

MACKi# (Подтверждение запроса). Этим сигналом системный арбитр сообщает i-му задатчику о разрешении доступа к шине, синхронизируется BCLK и удерживается до снятия сигнала MREQi#.

48

START#(Старт).Сигнал,равныйподлительностиодномупериодуBCLK и устанавливаемый задатчиком для определения начала цикла передачи данных;

MS BURST# (Пакетный режим задатчика). Этот сигнал устанавливается задатчиком и сообщает исполнителю о режиме пакетной передачи. Сигнал MS BURST# формируется по переднему фронту BCLK после выдачи сигнала START# и при наличии сигнала SL BURST#, приходящего от исполнителя;

SLBURST#(Пакетныйрежимисполнителя).Сигнал,сообщающийзадатчику о том, что исполнитель поддерживает пакетный режим;

M/IO# (память / ввод-вывод). Используется задатчиком для уведомления устройств о типе цикла шины (1- цикл передачи данных в память или 0 – цикл передачи данных в устройство ввода / вывода);

W/R# (Запись / чтение). Высокий уровень сигнала указывает на запись данных, а низкий уровень – на чтение данных;

LA2 – LA16, LA24 – 31 (Адресная шина). Сигналы соответствующих битов адреса, устанавливаемые задатчиком и не фиксируемые в течение всего цикла обмена данными. Адресные сигналы LA1 и LA0 не используется, и вместо них применяются сигналы (BE3 – BE0)#;

D16 – D31 Сигналы старших битов данных.

Различают следующие режимы передачи данных: стандартный, пакетный и сжатый, выполняемый только процессором. В стандартном режиме используются тактовые сигналы BCLK, частота которых находится в диапазоне от 6 до 8,33 МГц и зависит от частоты микропроцессора, например, для микропроцессора с частотой 25 МГц частота EISA равна 8,33 МГц.

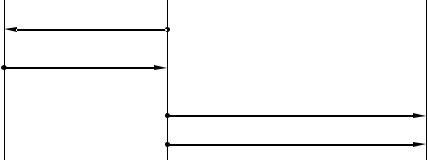

Последовательность сигналов стандартной передачи показана на рис. 2.13.

Арбитр |

Задатчик |

Исполнитель |

Уст. MREQi# 1

2Уст. MACKi#

3 |

Уст. LA31 – LA2, M/IO# |

|

|

4 |

Уст. BE3# – BE0#, W/R# |

|

Уст START# |

49

Примечание: Уст. – установка, Сбр. – сброс, знак # указывает на активный низкий уровень.

Рис. 2.13. Последовательность сигналов стандартной передачи данных

Установка сигналов в указанной последовательности производится по положительному фронту сигнала BCLK.

При выполнении стандартной передачи осуществляются следующие дей-

ствия:

1.Задатчик устанавливает сигнал MREQi #, поступающий в арбитр, для получения управления шиной EISA.

2.Арбитр выполняет процедуру арбитража и отвечает сигналом MACKi #.

3.Задатчик, захватив шину, устанавливает адрес LA31 – LA2 и сигнал исполнителя M/IO по положительному фронту BCLK.

4.Затем захватчик указывает тип операции сигналом W/R# и разрешенные байты сигналами BE3# - BE0#.

50

5.По положительному фронту BCLK задатчик формирует сигнал начала цикла на шине START#.

6.Если выполняется операция записи (W) данных в исполнитель, то задатчик устанавливает по положительному фронту BCLK данные D31 – D0.

7.Исполнитель после дешифрации адреса отвечает сигналом EX32# (EX16#), указывающим задатчику на разрядность исполнителя.

8.Задатчик анализирует сигнал EX32#(EX16#), сбрасывает сигнал START# и устанавливает сигнал CMD#.

9.Задатчик сбрасывает биты адреса LA31 – LA2 и сигналы BE3# – BE0#, кроме того, по отрицательному фронту BCLK задатчик выполняет проверку сигнала готовности исполнителя EXRDY (при его отсутствии производятся такты ожидания в работе задатчика).

10.В свою очередь, исполнитель снимает сигнал EX32#(EX16#) и устанавливает сигнал готовности EXRDY, который прекращает такты ожидания в работе задатчика.

12.Если выполняется операция чтения (R), то при наличии сигнала EXRDY задатчик осуществляет прием данных D31 – D0, которые уже были установлены исполнителем при условии опознания адреса и наличия низких уровней сигналов W/R# и CMD#.

13,14. Исполнитель сбрасывает сигнал EXRDY и снимает данные D31 – D0 при выполнении операции чтения (R).

15.Задатчикзавершаетциклодиночнойпередачиданных,сбрасываетсигнал MREQi # и снимает данные D31 – D0, если выполнялась операция (W) записи данных.

16.Арбитр сбрасывает сигнал MACKi #.

На рис. 2.14 представлена обобщенная структурная схема исполнителя.

С целью упрощения рисунка структурной схемы в ней не показаны компоненты автоконфигурирования.