KonspLektsy

.pdf

2. ФУНУЦИОНАЛЬНЫЕ УЗЛЫ КОМБИНАЦИОННОГО

ТИПА

Комбинационные логические устройства состоят только из логических элементов. Сигнал на выходе таких устройств определяется только комбинацией входных сигналов в данный момент времени.

2.1 Типовые логические схемы.

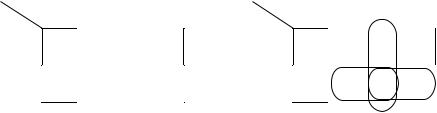

Элемент “Нечетность” (устройство неравнозначности)

Логика работы такого элемента следующая: единица на выходе присутствует при нечетном количестве единиц на входе.

Условное графическое изображение такого элемента:

x1 |

|

M2 |

|

y |

|

|

|||

x2 |

|

|

|

|

|

|

|

|

|

xn |

|

|

|

|

|

|

|

|

В простейшем случае элемент “Нечетность” представляет собой устройство неравнозначности: устройство с двумя входами, на выходе которого сигнал 1 появляется только в том случае, когда сигналы на входах неравны.

Таблица истинности и логическая функция, описывающая работу устройства неравнозначности:

F AB AB А В

21

Получили еще одну из операций булевой алгебры. Она называется сумма по модулю два. По этому принципу производится алгебраическое сложение двух одноразрядных чисел.

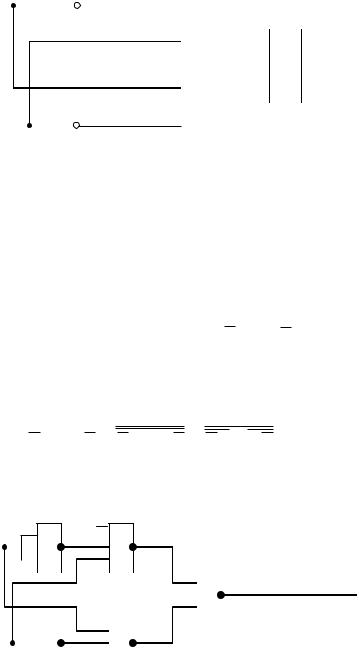

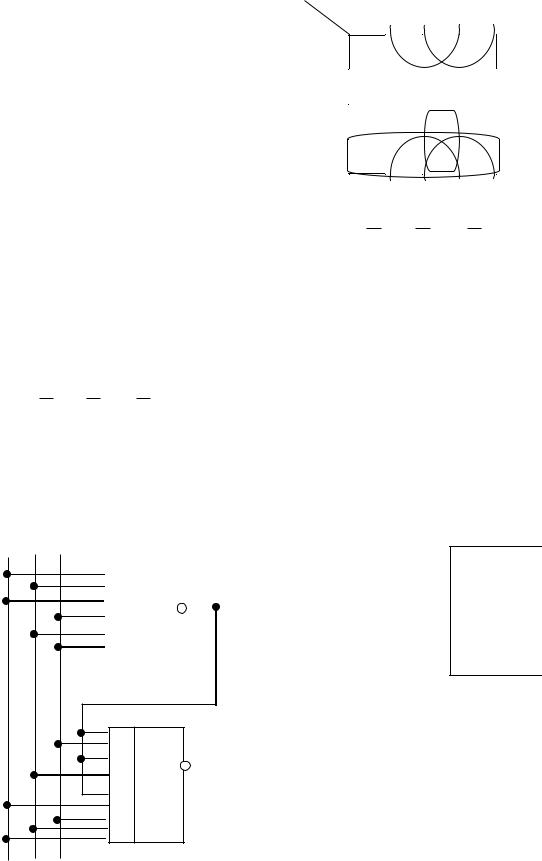

На рисунке 2.1 приведена функциональная схема устройства неравнозначности, построенная на логических элементах И, ИЛИ, НЕ.

A |

1 |

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

||||

|

& |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

AB |

|

|

||||||

|

|

|

|||||||||

|

|

|

|

|

|

|

1 |

||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

F |

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

AB AB |

||||||

|

|

& |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

1 |

B |

|

AB |

|||||||||||||

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.2.1 Логическая схема устройства неравнозначности.

Для построения устройства неравнозначности можно применить логические элементы ИЛИ-НЕ или И-НЕ, каждый из которых, как известно,

образует функционально полную систему элементов. В этом случае структурную формулу необходимо предварительно преобразовать к виду, удобному для реализации схемы с помощью этих элементов. Перейдем к базису И-НЕ:

F AB AB AB AB AB AB

Схема в базисе И-НЕ показана на рис. 2.2.

&A &

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

AB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

F AB AB |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

& |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

A |

B AB |

||||||||||||

B |

|

|

& |

& |

|

AB |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Рис.2.2 Логическая схема устройства неравнозначности в базисе И-НЕ

22

В случае двух входных сигналов функцию сумма по модулю два можно реализовать на элементе “ исключающее ИЛИ ”, логика работы которого состоит в следующем: на выходе единица, когда на входах присутствует только одна единица.

Условное графическое изображение такого элемента:

x1 |

|

=1 |

|

y |

|

||||

x2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Элемент “Четность” (устройство равнозначности)

Логика работы такого элемента следующая: единица на выходе присутствует при четном количестве единиц на входе.

Условное графическое изображение такого элемента:

x1 M2 |

y |

x2

xn

В простейшем случае элемент “Четность” представляет собой устройство равнозначности: устройство с двумя входами, на выходе которого сигнал 1

появляется только в том случае, когда сигналы на входах равны.

Таблица истинности и логическая функция, описывающая работу устройства равнозначности:

А |

В |

F |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

F |

A |

|

B AB А В |

||

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

|

|

|

|

|

В случае двух входных сигналов функцию сумма по модулю два с инверсией можно реализовать на одноразрядном компараторе.

Условное графическое изображение одноразрядного компаратора:

23

х1 |

|

|

|

|

|

= = |

|

y |

|

|

|

|||

|

|

|

||

х2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Элементы четности и нечетности являются базовыми при построении сумматоров, а также цепей контроля четности или нечетности цифровых кодов.

Полусумматор.

Полусумматор – логическая схема с двумя входами и двумя выходами,

предназначенная для суммирования двух одноразрядных чисел.

Таблица истинности полусумматора:

X2 |

X1 |

S' |

P' |

х1, х2 – входные сигналы; |

|

|

|

|

|

S′ |

- выход частичной суммы; |

0 |

0 |

0 |

0 |

||

|

|

|

|

Р′ |

- единица переноса в старший разряд |

0 |

1 |

1 |

0 |

||

|

|

|

|

|

|

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

Запишем выходные функции. По выходу суммы реализуется суммирование по модулю два, а по выходу переноса - конъюнкция входных переменных.

S x1 x2

Р x1 x2

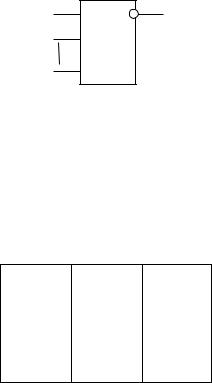

Покажем логическую реализацию и условное графическое изображение полусумматора:

x1  x2

x2

=1 |

s` |

|

|

|

|

x1 |

HS S |

s` |

|

|

|

|||

& |

p` |

x2 |

CO |

p` |

|

|

|

||

|

|

|

|

Рис 2.3

24

Полусумматор не может использоваться для сложения многоразрядных чисел, т.к. не имеет входа переноса из предыдущего разряда. Однако на нем можно суммировать младшие разряды многоразрядных чисел.

Полный сумматор

Полный сумматор – логическая схема, имеющая три входа: два из них предназначены для разрядов суммируемых чисел, а третий – для возможной единицы переноса, образовавшейся при сложении чисел предыдущего разряда.

Как и полусумматор, полный сумматор имеет два выхода: выход суммы и выход переноса. Таким образом, полный сумматор – это логическая схема для суммирования двух многоразрядных двоичных чисел..

Составим таблицу истинности для полного сумматора одноименных разрядов двух многоразрядных чисел

№ |

X2 |

X1 |

Pi-1 |

S |

Pi |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

2 |

0 |

1 |

0 |

1 |

0 |

3 |

0 |

1 |

1 |

0 |

1 |

4 |

1 |

0 |

0 |

1 |

0 |

5 |

1 |

0 |

1 |

0 |

1 |

6 |

1 |

1 |

0 |

0 |

1 |

7 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

Pi – единица переноса для данного разряда

Pi-1 – единица переноса из предыдущего разряда.

S - сумма

S x2 x1 Pi 1 x2 x1 Pi 1 x2 x1 Pi 1 x2 x1 Pi 1 Pi 1 (x2 x1 x2 x1 )

(x2 x1 x2 x1 )Pi 1 (x1 x2 )Pi 1 (x1 x2 )Pi 1 (x1 x2 )Pi 1 x1 x2 Pi 1 Pi x2 x1 Pi 1 x2 x1 Pi 1 x2 x1 Pi 1 x2 x1 Pi 1 x2 x1 Pi 1 (x2 x1 )

Видно, что схема полного сумматора реализуется на двух полусумматорах и элементе ИЛИ:

25

x1 |

|

|

HS |

S |

|

|

|

|

HS |

S |

|

|

||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

CO |

|

|

|

|

|

|

CO |

|

|

|

x2 |

|

|

|

|

|

|

|

|

|

|

|

|

||

pi-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

1 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

s`

pi

Рис.2.4

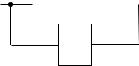

Полученная схема не является оптимальной. Попытаемся ее минимизировать. Для этого составим карты Карно для выходов суммы и переноса.

x2x1 |

|

|

|

|

Pi-1 |

00 |

01 |

11 |

10 |

|

|

|

|

|

0 |

0 |

1 |

0 |

1 |

0 |

2 |

6 |

4 |

|

|

1 |

0 |

1 |

0 |

|

1 |

3 |

7 |

5 |

x2x1 |

|

|

|

|

Pi-1 |

00 |

01 |

11 |

10 |

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

2 |

6 |

4 |

|

1 |

0 |

1 |

1 |

1 |

1 |

3 |

7 |

5 |

Pi x1 x2 x1 Pi 1 x2 Pi 1

Выражение для суммы не упрощается. Попробуем все же уменьшить число переменных в конъюнкциях, используя следующую идею: будем использовать полученное значение переноса как вспомогательный аргумент для вычисления суммы. Напротив наборов аргументов, которые являются нереальными, будем ставить знак неопределенности.

№ |

X2 |

X1 |

Pi-1 |

Pi |

S |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

X |

2 |

0 |

0 |

1 |

0 |

1 |

3 |

0 |

0 |

1 |

1 |

X |

4 |

0 |

1 |

0 |

0 |

1 |

5 |

0 |

1 |

0 |

1 |

X |

|

|

|

|

|

|

26

6 |

0 |

1 |

1 |

0 |

X |

7 |

0 |

1 |

1 |

1 |

0 |

8 |

1 |

0 |

0 |

0 |

1 |

9 |

1 |

0 |

0 |

1 |

X |

10 |

1 |

0 |

1 |

0 |

X |

11 |

1 |

0 |

1 |

1 |

0 |

12 |

1 |

1 |

0 |

0 |

X |

13 |

1 |

1 |

0 |

1 |

0 |

14 |

1 |

1 |

1 |

0 |

X |

15 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

x2x1 |

|

|

|

|

Pi-1Pi |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

X=1 |

1 |

0 |

4 |

12 |

8 |

|

01 |

X=1 |

X=1 |

0 |

X=1 |

1 |

5 |

13 |

9 |

|

11 |

X=1 |

0 |

1 |

0 |

3 |

7 |

15 |

11 |

|

10 |

1 |

X=1 |

X=1 |

X=1 |

2 |

6 |

14 |

10 |

S Pi 1 Pi x1 Pi x2 Pi Pi 1 x2 x1

Рис.2.5

Таким образом, на выходе полного сумматора реализуется система функций

S Pi 1 Pi x1 Pi x2 Pi Pi 1 x2 x1 Pi x1 x2 x1 Pi 1 x2 Pi 1

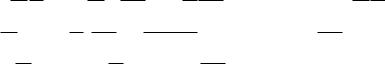

Построим схему на элементах 2-2-2-3И-ИЛИ-НЕ и покажем условное обозначение полного сумматора:

X2 X1 Pi-1

|

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

& |

1 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Pi |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

& |

|

|

|

|

x2 |

||||

|

|

|

|

|

|

|

|||||

|

|

& |

|

|

|

|

|

pi-1 |

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

& |

1 |

& |

|

|

|

S i |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

Рис. 2.6 |

& |

|

|

|

|

A |

SM |

S |

|

|

s` |

|

|||||

B |

|

|

|

|

|

CI |

|

CO |

|

|

p` |

|

|

||||

|

|

|

|

|

|

27

2.2 Сумматоры многоразрядных чисел.

Сумматоры выполняют арифметическое сложение и вычитание чисел.

Сумматоры имеют самостоятельное значение, а также являются ядром схем арифметико-логических устройств. Разработано множество вариантов построения сумматоров. Рассмотрим некоторые из них.

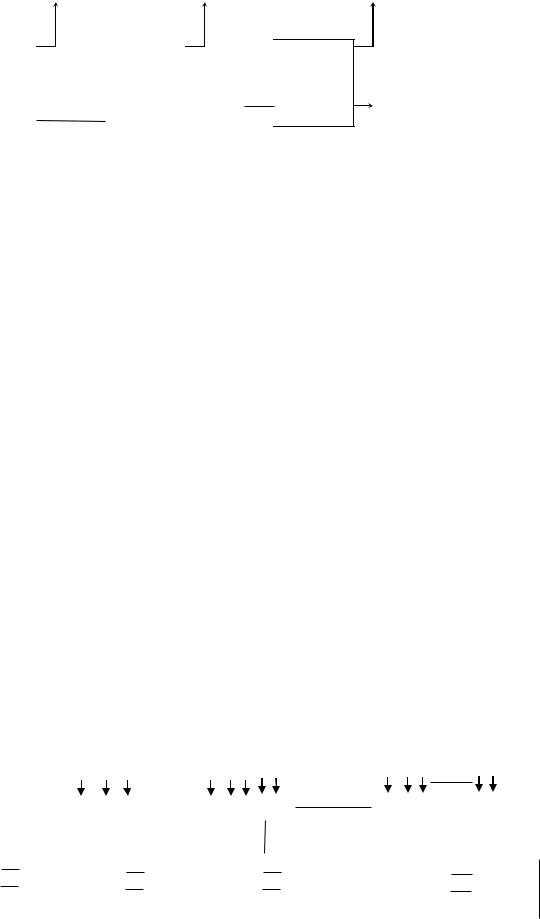

Последовательный сумматор.

Последовательный |

сумматор |

(рис. |

2.7) |

A |

|

|

|

|

|

|

|

S |

||||

|

1 |

|

SM |

S |

|

|||||||||||

содержит всего |

один |

полный |

сумматор, |

который |

|

|

|

|||||||||

B |

|

2 |

|

|

|

|

|

|

||||||||

поочередно обрабатывает |

разряды |

складываемых |

|

3 |

|

|

|

C |

|

|

||||||

Pi-1 |

|

|

|

|

|

|||||||||||

|

|

|

|

|

||||||||||||

чисел, начиная |

с |

младшего. |

Также |

содержит |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

D |

|

|

|

|||||||||

устройство задержки на один такт, которое

реализуется на D-триггере. Суммируемые числа на сумматор подаются в последовательном коде по тактам, начиная с младшего разряда.

Время выработки суммы: t = n·tSM ,

где n – число разрядов;

tSM – время суммирования в одноразрядном сумматоре.

Недостаток: тратится много времени на сложение многоразрядных чисел.

Параллельный сумматор с последовательным переносом.

В параллельных сумматорах происходит суммирование чисел в параллельном коде, результат выдаётся в параллельном коде.

Параллельный сумматор с последовательным переносом (рис.2.8)

содержит цепочку полных сумматоров, соединенных последовательно по цепям переноса. Количество полных сумматоров определяет разрядность суммируемых чисел.

28

|

|

|

|

S0 |

|

|

|

|

S1 |

|||||

|

a0 |

|

|

|

|

a1 |

|

|

|

|

|

|

am |

|

|

1 |

SM |

S |

|

1 |

SM |

S |

|

|

|||||

|

b0 |

|

b1 |

|

|

bm |

|

|||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

Pвх |

2 |

|

|

|

|

2 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||||

3 |

|

С |

|

|

3 |

|

С |

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.2.8

Sm

1 |

SM |

S |

|

||

2 |

|

|

3 |

|

С |

|

|

|

|

|

|

В таком сумматоре суммирование осуществляется за один такт и быстродействие схемы определяется временем распространения сигнала переноса вдоль цепи одноразрядных сумматоров.

Параллельный сумматор с параллельным переносом.

Такие сумматоры разработаны для получения максимального быстродействия. Они не имеют последовательного распространения переноса вдоль разрядной сетки, во всех разрядах результаты вырабатываются одновременно.

Сигналы входного переноса для данного разряда вырабатываются специальными блоками переноса CR0…CRn-1 (от слова carry – перенос), на входы которых поступают все переменные, необходимые для выработки переноса (это внешний входной перенос и значения всех разрядов слагаемых,

младших относительно данного). Одноразрядные сумматоры в такой структуре упрощены (отсутствует выход переноса).

Рассмотрим общую структуру параллельного сумматора с параллельным переносом (рис.2.9).

Pвх a0 b0 |

Pвх |

a0 b0 |

a1 |

b1 |

Pвх |

a0 b0 |

an-2 bn-2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CRn-2 |

|

|

|

|

|

|

|

|

|

CR0 |

|

|

|

CR1 |

|

|

|

|

|

|

||||

Pвх |

|

|

|

|

P0 |

|

|

|

|

P1 |

|

|

|

|

Pn-2 |

|

|

|

|

a0 |

SM0 |

|

|

a1 |

|

SM1 |

|

a2 |

SM2 |

|

|

an-1 |

SMn-1 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

b0 |

|

|

|

b1 |

|

|

|

b2 |

|

|

|

bn-1 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S0 |

S1 |

S2 |

Sn-1 |

|

Рис. 2.9 Структура параллельного сумматора с параллельным переносом

29

Для перехода к конкретному виду схемы удобно ввести две

вспомогательные функции:

1.Функция генерации принимает единичное значение, если перенос на выходе данного разряда появляется независимо от наличия или отсутствия входного переноса:

gi = ai·bi.

2.Функция прозрачности равна единице, если перенос на выходе данного разряда появляется только при наличии входного переноса:

hi = ai+bi.

Тогда выражение для сигнала переноса можно записать в виде: Pi = gi + hi·Pi-1

Выведем выражения для сигнала переноса для нулевого, первого и второго разрядов с последующим их обобщением:

P0 = g0 + PВХ·h0

P1 = g1 + P0·h1 = g1 + g0·h1 + PВХ·h1·h0

P2 = g2 + P1·h2 = g2 + g1·h2 + g0·h2·h1 + PВХ·h2·h1·h0

Формулы имеют ясный физический смысл: перенос на выходе данного разряда сгенерируется в нем или придет от предыдущих разрядов при их прозрачности.

Для произвольного разряда можем записать:

Pi = = gi + gi-1·hi + gi-2·hi·hi-1 +…+g0·hi·hi-1·…·h1+ PВХ·hi·hi-1·…·h1·h0

Диапазон разрядностей n, в котором проявляются достоинства параллельных сумматоров с параллельным переносом, невелик. При разрядности n=3,4 преимущество имеют параллельные сумматоры с последовательным переносом, при разрядности n>8 появляются перегруженные элементы и элементы с большим числом входов. В этом случае используют сумматоры групповой структуры.

30