ЛР / Основы разработки систем на кристалле (метода)

.pdf

О. Ю. КАЗЬМИН А. А. ПРАСОЛОВ

УЧЕБНО-МЕТОДИЧЕСКОЕ ПОСОБИЕ ПО ВЫПОЛНЕНИЮ ЛАБОРАТОРНЫХ РАБОТ

САНКТ-ПЕТЕРБУРГ

2023

МИНИСТЕРСТВО ЦИФРОВОГО РАЗВИТИЯ, СВЯЗИ И МАССОВЫХ КОММУНИКАЦИЙ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ

«САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ТЕЛЕКОММУНИКАЦИЙ

им. проф. М. А. БОНЧ-БРУЕВИЧА»

(СПбГУТ)

О. Ю. Казьмин, А. А. Прасолов

ОСНОВЫ РАЗРАБОТКИ СИСТЕМ НА КРИСТАЛЛЕ

Учебно-методическое пособие по выполнению лабораторных работ

САНКТ-ПЕТЕРБУРГ

2023

УДК 004.383.3(076) ББК 32.859я73

К14

Рецензент кандидат технических наук, доцент,

заведующий кафедрой телевидения и метрологии СПбГУТ

С. Л. Федоров

Утверждено редакционно-издательским советом СПбГУТ в качестве учебно-методического пособия

Казьмин, О. Ю.

К14 Основы разработки систем на кристалле : учебно-методическое пособие по выполнению лабораторных работ / О. Ю. Казьмин, А. А. Прасолов ; СПбГУТ. – Санкт-Петербург, 2023. – 96 с.

Написано в соответствии с рабочей программой дисциплины «Основы разработки систем на кристалле».

Сформулированы методики проведения лабораторных работ с использованием отладочных плат ZedBoard и среды разработки Vivado. К каждой лабораторной работе приведены индивидуальные задания для закрепления материала.

Предназначено для студентов, обучающихся по направлениям подготовки 11.03.01 «Радиотехника», 11.03.02 «Медиатехнологии и телерадиовещание», 11.03.04 «Промышленная электроника».

УДК 004.383.3(076) ББК 32.859я73

©Казьмин О. Ю., Прасолов А. А., 2023

©Федеральное государственное бюджетное образовательное учреждение высшего образования

«Санкт-Петербургский государственный университет телекоммуникаций им. проф. М. А. Бонч-Бруевича», 2023

2

СОДЕРЖАНИЕ |

|

Лабораторная работа 1 |

|

СОЗДАНИЕ ПРОЕКТА ПРОЦЕССОРНОЙ СИСТЕМЫ ДЛЯ РАБОТЫ |

|

С АППАРАТНЫМ UART-ИНТЕРФЕЙСОМ ............................................................ |

4 |

Лабораторная работа 2 |

|

СОЗДАНИЕ ПРОЕКТА ПРОЦЕССОРНОЙ СИСТЕМЫ ДЛЯ РАБОТЫ |

|

С ПОРТАМИ MIO И EMIO ....................................................................................... |

16 |

Лабораторная работа 3 |

|

СОЗДАНИЕ ПРОЕКТА ПРОЦЕССОРНОЙ СИСТЕМЫ ДЛЯ РЕАЛИЗАЦИИ |

|

ЛОГИЧЕСКИХ ВЫРАЖЕНИЙ НА ПОРТАХ EMIO ............................................. |

24 |

Лабораторная работа 4 |

|

РАЗРАБОТКА МНОГОФАЙЛОВОГО ПРОЕКТА НА ЯЗЫКЕ |

|

ПОВЕДЕНЧЕСКОГО ОПИСАНИЯ ......................................................................... |

34 |

Лабораторная работа 5 |

|

СОЗДАНИЕ ПРОЕКТА ПРОЦЕССОРНОЙ СИСТЕМЫ ДЛЯ РАБОТЫ |

|

С GPIO-ПОРТАМИ .................................................................................................... |

42 |

Лабораторная работа 6 |

|

СОЗДАНИЕ ПОЛЬЗОВАТЕЛЬСКОГО RTL-ЭЛЕМЕНТА, СОВМЕСТИМОГО |

|

С GPIO-ИНТЕРФЕЙСОМ.......................................................................................... |

52 |

Лабораторная работа 7 |

|

СОЗДАНИЕ ПРОЕКТА ДЛЯ РАБОТЫ КОНТРОЛЛЕРОМ ПРЕРЫВАНИЙ ..... |

61 |

Лабораторная работа 8 |

|

ПОСТРОЕНИЕ BRAM-ПАМЯТИ С АДРЕСНЫМ ДОСТУПОМ |

|

ИЗ ПРОЦЕССОРНОЙ ЧАСТИ СИСТЕМЫ НА КРИСТАЛЛЕ ............................. |

70 |

Лабораторная работа 9 |

|

РАЗРАБОТКА ПРОЕКТА ДЛЯ УПРАВЛЕНИЯ СЕМИСЕГМЕНТНЫМ |

|

ИНДИКАТОРОМ С ПОМОЩЬЮ ПОВОРОТНОГО ЭНКОДЕРА....................... |

77 |

Лабораторная работа 10 |

|

ИССЛЕДОВАНИЕ МУЛЬТИПРОЦЕССОРНОЙ СИСТЕМЫ |

|

НА КРИСТАЛЛЕ ........................................................................................................ |

86 |

СПИСОК РЕКОМЕНДУЕМЫХ ИСТОЧНИКОВ ................................................... |

95 |

3

Лабораторная работа 1

СОЗДАНИЕ ПРОЕКТА ПРОЦЕССОРНОЙ СИСТЕМЫ ДЛЯ РАБОТЫ С АППАРАТНЫМ UART-ИНТЕРФЕЙСОМ

Цель работы

Ознакомление с процессом создания блочного проекта (Block Design), конфигурирующего процессорную систему Zynq для работы с аппаратным интерфейсом UART, и написанием приложения, которое выводит результаты вычисления в консоль интерфейса.

Основные вопросы, изучаемые перед выполнением работы

1.Архитектура системы на кристалле Xilinx Zynq7000.

2.Структура лабораторного макета ZedBoard.

3.Подключение аппаратного UART-интерфейса.

Содержание работы

1. Создать новую отдельную директорию для лабораторной работы. При создании директории важно не допускать пробелов и использовать только латинские символы, подчеркивания и дефисы. Например, полный путь к директории для данной лабораторной работы имеет вид:

D:/(год)/(фамилия)_(группа)/soc-lab-1. 2. Создание проекта в Vivado 2016.4.

2.1.Откройте среду разработки Vivado 2016.4.

2.2.Выберите пункт Create New Project (рис. 1) и в открывшемся окне нажмите Next.

Рис. 1. Окно создания проекта

2.3.Введите имя проекта Zynq_hello_lab_variant_(номер варианта)

иукажите путь к созданной ранее директории (рис. 2), оставив отметку напротив Create project subdirectory. Это позволит создать для проекта отдельный каталог и поместить в него все файлы проекта. Данная функция будет постоянно использована в последующих работах, в рамках которых будет создано несколько проектов. Запишите цель работы в протокол.

4

Рис. 2. Окно выбора директории проекта

2.4.Нажмите Next.

2.5.Убедитесь, что в следующем окне установлены указатель RTL project и отметка Do not specify sources at this time. Нажмите Next (рис. 3).

Рис. 3. Окно выбора типа проекта

2.6. В следующем окне выберите вкладку Board и модель отладочной платы ZedBoard. Нажмите Next (рис. 4).

Рис. 4. Окно выбора отладочной платы

5

2.7. Проверьте Project summary и нажмите Finish. На данном этапе создан пустой проект для платы ZedBoard (рис. 5).

Рис. 5. Окно свойств созданного проекта

3. Создание Block Design.

3.1. Рассмотрите окно среды после создания проекта (рис. 6). Панель Flow Navigator включает в себя полный набор кнопок для создания проекта. Примечательно, что кнопки на данной панели находятся в хронологическом порядке этапов создания, отладки и тестирования на отладочной плате:

•1 – Project Manager – открывает окно менеджера проекта и позволяет добавлять, удалять файлы в проект;

•2 – IP integrator – дает возможность создать блочный проект и добавить IP-блоки;

•3 – Simulation – открывает панель симуляции проекта;

•4 – RTL-анализ – генерирует RTL-схему проекта и позволяет просмотреть, в виде каких элементов синтезируется проект;

•5 – Synthesis – содержит под собой элементы запуска синтеза проекта и позволяет получить отчеты по разрабатываемым устройствам;

•6 – Implementation – содержит под собой элементы запуска размещения синтезированного проекта и получения отчетов по результатам размещения.

6

Рис. 6. Окно среды разработки после создания пустого проекта

3.2.Создайте Block Design, нажав Create Block Design на панели Flow Navigator. В появившемся поле поиска впишите имя блочного проекта

Zynq_hello.

3.3.Во вкладке Diagram нажмите сочетание клавиш Сtrl + i и в открывшемся окне впишите имя добавляемого ip-элемента Zynq (рис. 7). Затем дважды кликните по элементу Zynq7 Processing System.

Рис. 7. Окно поиска для добавления IP-элемента

7

3.4.После появления элемента на поле диаграммы нажмите Run Block Automation.

3.5.В открывшемся окне уберите галочку с пункта Apply Board Preset, это позволит самостоятельно настроить проект под выбранную плату. Нажмите ОK (рис. 8).

Рис. 8. Окно запуска автоматической конфигурации

3.6. Вид проекта изменился: Design Assistance автоматически определил, что необходимо подключение внешних интерфейсов FIXED_IO и DDR. Данные интерфейсы служат для конфигурации внутренней периферии (например, UART, Ethernet, USB) в подсистеме Zynq. Но на данном этапе подсистема еще не сконфигурирована полностью.

4. Конфигурация процессорной системы.

4.1.Для конфигурации подсистемы Zynq щелкните указателем по блоку

Zynq7 Processing System.

4.2.Нажмите MIO Configuration на панели Page Navigator. Развер-

ните все пункты и активируйте галочку напротив UART 1, а также в верхней части окна установите значение LVCMOS 3.3 для Bank 0 и LVCMOS 1.8 для Bank 1 (рис. 9). UART сконфигурирован. Зафиксируйте установленные параметры в протокол.

Рис. 9. Окно конфигурации UART

8

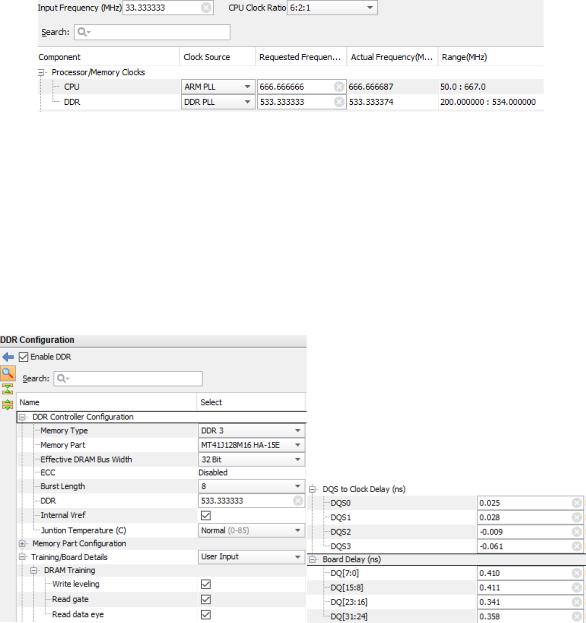

4.3. Перейдите на Clock Configuration и сверьте параметры (рис. 10).

Рис. 10. Параметры частот для процессора и оперативной памяти

4.4. Откройте DDR Configuration и установите галочки напротив Enable DDR, Internal Vref, Write leveling, Read gate, Read data eye (рис. 11). Установите Memory Type на значение DDR3, Memory Part – MT41J128M16 HA – 15E. Также установите задержки тактового сигнала для данной платы: DQS0 = 0.025, DQS1 = 0.028, DQS2 = –0.009, DQS3 = –0.061,

DQ[7:0] = 0.410, DQ[15:8] = 0.411, DQ[23:16] = 0.341, DQ[31:24] = 0.358.

Зафиксируйте эти данные в протокол.

Рис. 11. Окно параметров DDR

4.5.Необходимо отключить Master AXI Interface, так как данный интерфейс не используется: для этого откройте Ps-Pl Configuration → AXI Non secure Enablement → GP Master AXI Interface и снимите галочку напротив M AXI GP0 Interface.

4.6.На данном этапе процессорная система сконфигурирована. Нажмите ОK для выхода из окна настройки блока Zynq7 и сохраните проект. Зарисуйте в протокол блок-схему проекта и запишите основное назначение

FIXED_IO.

9