книги / Надежность и диагностика компонентов инфокоммуникационных и информационно-управляющих систем

..pdf

По окончании моделирования на выходах элементов D5 и D6 остались неопределенные значения, значит, в данной ситуации возможны критические состязания, как видно из табл. 14.2.

Варианты заданий для самостоятельных и расчетных работ

Задание: промоделировать указанную в варианте схему при отсутствии неисправности и при наличии заданной неисправности. Сравнить результаты моделирования и сделать вывод о возможности критических состязаний.

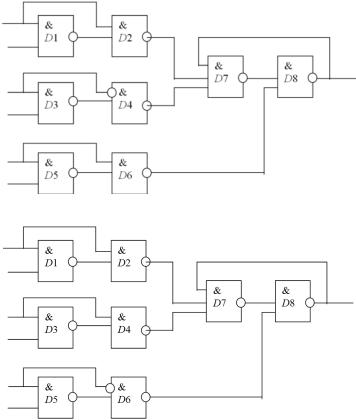

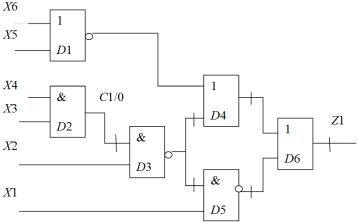

Рис. 14.2. Последовательностная схема, вариант 1

Рис. 14.3. Последовательностная схема, вариант 2

111

Рис. 14.4. Последовательностная схема, вариант 3

Рис. 14.5. Последовательностная схема, вариант 4

1.Рис. 14.2. Константа 1 на линии между входом А и элементом D1.

2.Рис. 14.3. Константа 0 на линии между входом А и элементом D1.

3.Рис. 14.4. Константа 1 на линии между входом C и элементом D3.

4.Рис. 14.5. Константа 0 на линии между входом C и элементом D3.

5.Рис. 14.2. Константа 1 на линии между входом E и элементом D5.

112

6.Рис. 14.3. Константа 0 на линии между входом E и элементом D5.

7.Рис. 14.4. Константа 1 на линии между входом А и элементом D2.

8.Рис. 14.5. Константа 0 на линии между входом А и элементом D2.

9.Рис. 14.2. Константа 1 на линии между входом C и элементом D4.

10.Рис. 14.3. Константа 0 на линии между входом C и элементом D4.

11.Рис. 14.4. Константа 1 на линии между входом E и элементом D6.

12.Рис. 14.5. Константа 0 на линии между входом E и элементом D6.

13.Рис. 14.2. Константа 0 на линии между входом B и элементом D1.

14.Рис. 14.3. Константа 0 на линии между входом D и элементом D3.

15.Рис. 14.4. Константа 0 на линии между входом F и элементом D5.

16.Рис. 14.5. Константа 1 на линии между элементами D1 и D2.

17.Рис. 14.2. Константа 0 на линии между элементами D1 и D2.

18.Рис. 14.3. Константа 1 на линии между элементами D3 и D4.

19.Рис. 14.4. Константа 0 на линии между элементами D3 и D4.

20.Рис. 14.5. Константа 1 на линии между элементами D5 и D6.

21.Рис. 14.2. Константа 0 на линии между элементами D5 и D6.

22.Рис. 14.3. Константа 1 на линии между элементами D2 и D7.

23.Рис. 14.4. Константа 0 на линии между элементами D2 и D7.

24.Рис. 14.5. Константа 1 на линии между элементами D4 и D7.

В данной теме рассматривалось троичное моделирование исправной схемы, а также троичное моделирование схем с неисправностью, что позволяет выявить критические состязания. Схема задается на структурно-логическом уровне, модель дефекта – константная неисправность.

113

ТЕМА 15. ПОСТРОЕНИЕ ТЕСТОВ ДЛЯ КОМБИНАЦИОННЫХ СХЕМ

Принципы построения тестов для комбинационных схем изложены в п. 4.2. учебного пособия [2].

Вотличие от моделирования, которое является прямой задачей диагноза, построение тестов является обратной задачей диагноза. Мы знаем, какой результат мы хотим получить на выходах схемы, и подбираем значения входов, позволяющие получить заданный результат.

Существует два типа тестов, проверяющие и локализующие. Проверяющий тест позволяет только определить, есть в схеме неисправность или нет, но не указать ее место. Локализующий же тест позволяет указать место дефекта (с определенной точностью). В данном разделе мы будем строить проверяющие тесты.

Далее, в схеме может иметь место как однократный дефект, так и кратный дефект, то есть совокупность некоторого количества дефектов, начиная с двух. В данной теме мы будем строить проверяющие тесты для однократных дефектов.

Вкачестве модели объекта будем использовать структурнологическую модель (перечень элементов и связей между ними), в качестве модели дефекта – константную модель (постоянный 0 или 1 на одной из линий схемы). Таким образом, общее количество возможных однократных дефектов равно количеству линий схемы, умноженному на 2. Полный тест для схемы является совокупностью элементарных проверок (или элементарных тестов), каждая из которых определяет наличие или отсутствие одного константного дефекта из всех возможных. В литературе часто путают поня-

тия полный тест и элементарная проверка, называя и то и другое тестом, однако обычно из контекста ясно, о чем идет речь.

Нахождение элементарных проверок по структурно-логи- ческой модели базируется на понятии существенного пути, лежащего в основе организации перебора вариантов решения.

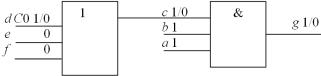

Рассмотрим структурно-логическую модель схемы, представленную на рис. 15.1. Линии обозначены буквами a–g. Пусть на линии d имеется неисправность типа константы 0 (С0).

114

Рис. 15.1. Структурно-логическая модель схемы с константным дефектом

Из очевидных соображений следует, что одиночный дефект может быть обнаружен элементарной проверкой, обладающей следующими свойствами.

Первое свойство состоит в том, что возникшая неисправность проявляется, т.е. вызывает появление значения хотя бы одного сигнала на любой линии связи объекта диагноза (ОД), отличного от значения, которое этот сигнал имел бы в исправном состоянии. Это свойство называют условием проявления неисправности.

Данная неисправность проявляется, так как при подаче на вход d единицы сигнал на линии d из-за неисправности будет не единицей, как в исправной схеме, а нулем. Это представлено на схеме записью 1/0. Запись значения сигнала в виде 1/0 означает 1 в исправном случае и 0 в неисправном случае.

Второе свойство: значения сигналов, вызванные проявлением неисправности, передаются на один или несколько выходов ОД так, чтобы они отличались для исправного и неисправного случаев. Это означает образование существенного (активизированного или чувствительного) пути распространения эффекта неисправности в объекте диагноза.

На выходе рассматриваемой схемы (линия g) при отсутствии неисправности будет 1, а при наличии заданной константной неисправности будет 0. Поскольку выходы исправной и неисправной схемы отличаются, значит, был образован существенный путь. Распространение сигнала по существенному пути происходит следующим образом.

Неисправность С0 на входе d элемента ИЛИ может быть обнаружена на его выходе набором (d = 1, e = 0, f = 0).

115

Нельзя непосредственно наблюдать значение сигнала во внутренней точке с, поэтому необходимо задать входы элемента И так, чтобы наблюдать эффект неисправности на его выходе, т.е. a = 1, b = 1. При этих значениях изменение сигнала на входе с приводит к изменению сигнала на выходе g. Если же мы поставим, например, на входе a 0, то на выходе g будет 0, как при наличии заданной неисправности, так и при ее отсутствии. В этом примере d–c–g – существенный (активизированный) путь, значения сигналов на d, e и f – условия проявления неисправности, а на b и a – условия активизации.

Сформулируем методику построения теста методом активизации существенного пути.

1. Выбираем путь от места неисправности, скажем, от элемента А (неисправность Сх) через последовательность элементов B, …, Z к некоторому выходу схемы Y (рис. 15.2). Пути в схеме могут быть как одномерные, так и многомерные, т.е. проходящие через разветвления сразу в нескольких направлениях.

Линии, принадлежащие выбранному пути, помечаем черточками.

Рис. 15.2. Выбор пути

2. Значения непомеченных входов элементов B, C, …, Z выбираются по второму свойству так, что значения выходов элементов определяются только значениями помеченных входов, а о значении выхода элемента A можно сделать вывод, наблюдая вы-

116

ход z элемента Z. Значения входов элемента A должны быть заданы так, чтобы о наличии или отсутствии неисправности можно было бы судить по значению сигнала на его выходе. Эти действия называют прямой фазой активизации существенного пути или просто активизацией.

3. Далее необходимо так установить внешние входы, чтобы обеспечить требуемые значения на входах элементов А, B, C, …, Z. Для этого прослеживаются назад пути по схеме от входов элементов А, B, C, …, Z до внешних входов схемы, и выбираются соответствующие значения сигналов на входах задействованных элементов. Эти действия называют обратной фазой активизации существенного пути, или доопределением.

Как прямая, так и обратная фазы связаны с перебором вариантов. Выбор очередного варианта происходит при возникновении противоречия, т.е. требования поставить разные значения на одном и том же входе, в момент присвоения значений линиям схемы. Задача сокращения перебора решается путем как можно более раннего обнаружения противоречия. Это приводит к уменьшению прохождения числа путей в дереве решений.

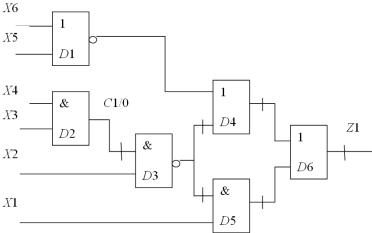

Пример 1. Построение элементарного теста по многомерному пути.

На рис. 15.3 приведена комбинационная схема с неисправностью С1 на линии, соединяющей элементы D2 и D3. Построим элементарный тест для этой неисправности.

Проведем построение теста для данной неисправности методом активизации существенного пути.

1. В месте неисправности поставим значение, которое мы должны обеспечить в исправной схеме и которое отличается от неисправного, т.е. 0. Выберем путь от места неисправности до выхода схемы Z, поскольку выход в схеме один. Разметим выбранный путь. Путь получился двумерный, так как выход элемента D3 разветвляется, а на элементе D6 разветвившийся сигнал снова сходится. Линии, принадлежащие выбранному пути, пометим черточками.

117

Рис. 15.3. Пример построения элементарного теста по многомерному пути

2.Выберем значения непомеченных входов элементов существенного пути. Для элемента D3 на непомеченный вход следует поставить 1, так как именно тогда выход элемента будет зависеть только от значения, распространяющегося по существенному пути, т.е. 0 в случае неисправной схемы и 1 в случае исправной. Для элемента D4 на непомеченный вход по аналогичным соображениям следует поставить 0, тогда на его выходе будет 0 в случае неисправной схемы и 1 в случае исправной. То же самое относится к элементу D5. У элемента D6 оба входа помеченные, поэтому мы просто моделируем его выход – 0 в неисправной схеме и 1 в исправной.

3.Далее производим доопределение. Чтобы в месте неисправности установить 0, на входы Х3 или Х4 следует подать 0. Единица по непомеченному входу элемента D3 устанавливается единицей непосредственно на входе Х2, равно как и единица по непомеченному входу элемента D5 устанавливается единицей непосредственно на входе Х1. Ноль по непомеченному входу

118

элемента D4 устанавливается нулем на выходе элемента D1, для чего либо на вход Х5, либо на вход Х6 надо подать 1.

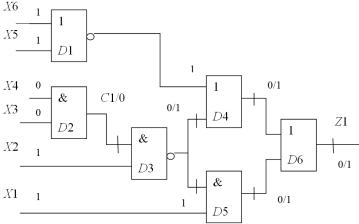

Таким образом, для заданной константной неисправности мы получили элементарный тест Х1 = 1; Х2 = 1; Х3 = 0; Х4 = 0;

Х5 = 1; Х6 = 1 (рис. 15.4).

Рис. 15.4. Элементарный тест для заданной константной неисправности

Полный тест, как уже говорилось, образуется из всех элементарных тестов для каждого возможного дефекта схемы. Однако некоторые дефекты схемы обнаруживаются одинаковыми элементарными тестами. Например, построенный элементарный тест обнаружит и неисправность С0 на линии, выходящей из элемента D3. Поэтому после построения полного теста мы сокращаем его размерность, удаляя одинаковые элементарные проверки. Однако нельзя исключить, что в ходе построения элементарных тестов были сделаны ошибки. Поэтому после сокращения мы проверяем моделированием полученный тест на полноту (т.е. составляем перечень неисправностей, которые тест реально обнаруживает).

119

Однако бывают такие комбинационные схемы, в которых для некоторых константных неисправностей не удается построить элементарный тест.

Пример 2. Схема, в которой для заданной константной неисправности нельзя построить элементарный тест, представлена на рис. 15.5.

Рис. 15.5. Неисправность, для которой нельзя построить элементарного теста

Рассмотрим схему на рис. 15.5. От предыдущей схемы на рис. 15.4 она отличается тем, что на выходе у элемента D5 теперь наличествует инверсия, это приводит к тому, что по одной ветви элемента D6 приходит сигнал 0/1, а по другой ветви – 1/0. В результате на выходе элемента D6 и при наличии, и при отсутствии неисправности на выходе будет 1, следовательно, элементарный тест для заданной неисправности построить нельзя.

Однако если бы у схемы был второй выход, например, непосредственно с элемента D4, то элементарный тест построить было бы можно и он по понятным причинам совпадал бы с тестом из примера 1.

120