итип1

.docx

|

|

|

Ордена Трудового Красного Знамени федеральное государственное бюджетное образовательное учреждение высшего образования «Московский технический университет связи и информатики»

Лабораторная работа №1

По дисциплине «Информационные технологии и программирование»

на тему: «Триггеры»

Выполнили:

поебота

Руководитель:

Воронкова М.Н

Москва 2023 г.

ЦЕЛЬ РАБОТЫ

Изучение логических возможностей триггерных схем.

ЗАДАНИЕ

Описать D-триггер, JK триггер.

Триггер – это запоминающий элемент с двумя устойчивыми состояниями, изменение которых происходит под действием входных сигналов, т.е. он хранит один бит информации (логический 0 или 1).

Схемы триггеров выполняют функции записи, считывания, стирания и индикации двоичной информации, а их состояние определяется сигналами на прямом и инверсном выходах Q и Q'. При использовании положительного кодирования информации, высокий уровень напряжения на прямом выходе отображает значение логической 1 (состояние Q = 1), а низкий уровень - значение логической 0 (состояние Q = 0). Изменение состояния триггера (его переключение) происходит при поступлении внешних сигналов.

Триггеры могут быть асинхронными или синхронными (тактируемыми) в зависимости от способа записи (приёма) информации. Асинхронные триггеры записывают информацию в любой момент времени при поступлении сигналов на информационные входы, в то время как синхронные триггеры могут записывать информацию только при совпадении сигналов на информационном и синхронном входах, что делает их более помехоустойчивыми.

Триггеры также могут быть однотактными, двухтактными или многотактными в зависимости от количества тактовых сигналов, необходимых для формирования нового состояния. По способу управления записью информации (моменту реакции на тактовый сигнал) выделяют синхронные триггеры со статическим (по уровню), динамическим (по фронтам) и двухступенчатым управлением. В первых запись информации возможна только в течение длительности тактового сигнала, а во вторых - разрешение на запись информации дается только в момент перепада тактового сигнала от нуля к единице (прямой динамический вход) и от единицы к нулю (инверсный динамический вход). В другие моменты времени он не реагирует на входные информационные сигналы, независимо от уровня тактового импульса.

Имеется несколько основных типов триггеров: RS- триггеры, D- триггеры, T- триггеры и JK-триггеры.

В данной лабораторной работе необходимо описать D- триггеры и JK-триггеры.

А) Триггер задержки, также известный как D-триггер, имеет один вход для информационного сигнала и один тактируемый (синхронизирующий) вход. Когда на вход приходит сигнал синхронизации (тактовый сигнал) CLK, триггер запоминает и хранит на выходе Q информацию, которая была на входе D в момент прихода CLK. Таким образом, триггер хранит информацию, записанную при CLK=1.

Обозначение D-триггера:

Рисунок 1 - Обозначение D-триггера

Входы D-триггера разделяются на информационные (управляющие) и вспомогательные. Вспомогательные предназначены синхронизировать работу устройства. Первые устанавливают на входе определённую комбинацию двоичных чисел, которая будет учитываться при формировании выходного сигнала. Управляет логикой работы тактовый сигнал. Именно он определяет момент срабатывания триггера, а от его характеристик зависит состояние выходного сигнала.

Способность сохранять информацию позволяет применять D-триггеры для реализации устройств памяти. Эти работающие элементы способны сохранять нужный режим на выходе до тех пор, пока не будет подан управляющий сигнал для изменения. Триггер даёт возможность, как вносить двоичную информацию, так и хранить и считывать её.

Одно из основных назначений D-триггера — использование в счетном режиме. Чтобы заставить его работать в качестве счетчика импульсов, достаточно на вход D подать сигнал с его собственного инверторного выхода. В таком режиме по приходу каждого импульса на вход С триггер будет менять свое состояние на противоположное.

Б) JK-триггер - имеет два информационных входа J и К, и тактируемый вход С. Назначение выводов J и К аналогично назначению выводов R и S, но при этом триггер не имеет запретных комбинаций. Если J = К = 1 он изменяет свое состояние на противоположное.

Обозначение JK-триггера:

Рисунок 2 - Обозначение JK-триггера

При соответствующем подключении входов, триггер может выполнять функции RS-, D-, T-триггеров, т.е. является универсальным триггером. Может выполнять функции RS-триггера (при раздельном поступлении сигналов J и К), Т-триггера (при одновременной подаче сигналов J и К), D-триггера (при подаче сигнала от входа J через инвертор на вход К).

Таким образом, при использовании JK-триггера для хранения информации - сигналы на входы J и К подаются поочередно. При совпадении же сигналов на входах J и К - реализуется счетный триггер.

Построить D-триггер, JK триггер с помощью программы Multisim.

А) Построение D-триггера:

Рисунок 3 - построение D-триггера

Рисунок 4 - временная диаграмма

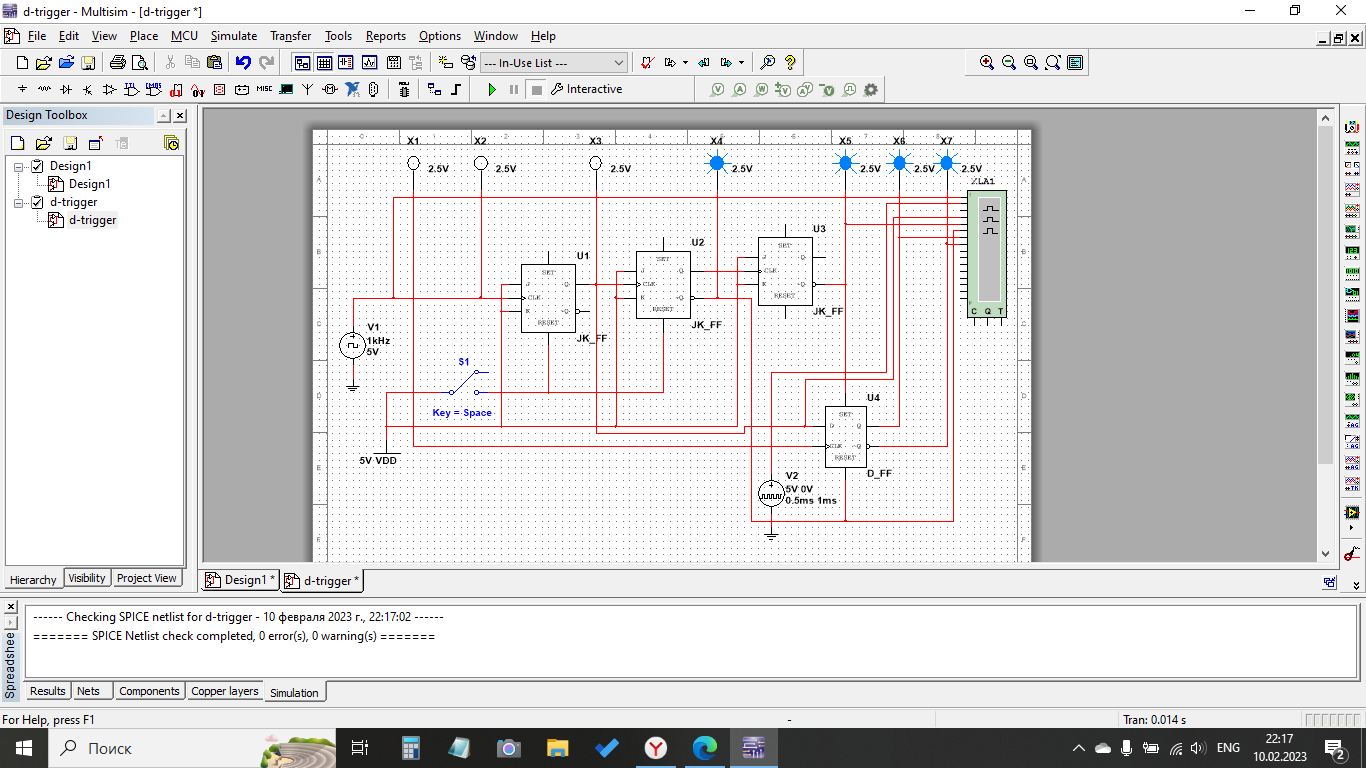

Б) Построение JK триггера:

Рисунок 5 - построение JK триггера

Рисунок 6 - временная диаграмма

ВЫВОД

В ходе данной лабораторной работы была исследована работа триггеров D и JK типа. Также, исходя из полученных временных диаграмм, сделан вывод о том, что эксперимент сходится с теорией.

|

|

|