Лабы 3 вариант / 3_3

.docxМинобрнауки России

Федеральное государственное автономное образовательное учреждение высшего образования «Национальный исследовательский университет

«Московский институт электронной техники»

Лабораторная работа №3 по дисциплине

«Синхронизация в высокоскоростных сетях передачи данных»

«Фазовая автоподстройка частоты»

Вариант 3

Цель работы: Исследование принципа работы схемы ФАПЧ

Вариант |

Несущая частота, МГц |

Полоса удержания ФАПЧ, кГц |

3 |

0,7 |

10 |

Таблица 1 – Данные по варианту

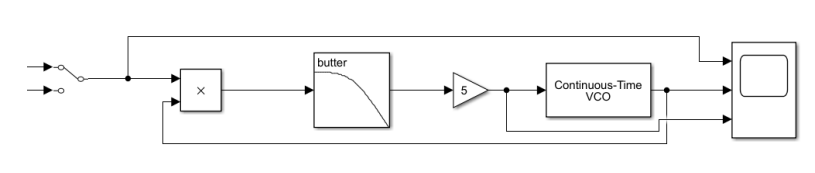

Для выполнения данной лабораторной работы в среде Matlab Simulink собрана схема ФАПЧ с использованием умножителя и ФНЧ (выделение сигнала ошибки частоты), усилителя и ГУН (подстройка под несущую) и обратной связи к умножителю. В схеме использован осциллограф для снятия входных и выходных сигналов.

Рисунок 1 – Схема ФАПЧ

Изменим входную частоту в пределах полосы удержания, т.е. +- 10 кГц.

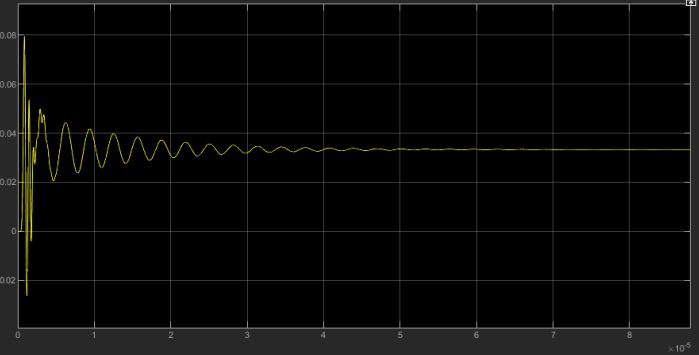

ФНЧ на низкой частоте среза позволяет выделить сигнал ошибки (разность частот входной и опорного генератора VCO). По (1) 3 заданию установлен ФНЧ 1 порядка Баттерворта с частотой среза в 5 кГц (полоса удержания 10 кГц).

Генератору задана изначальная частота в 0.7 МГц. Поскольку изначально амплитуда приходящего сигнала должна находиться в пределах ±1В, установлена чувствительность, соответствующая требуемому диапазону подстройки частоты – ±5 кГц от несущей

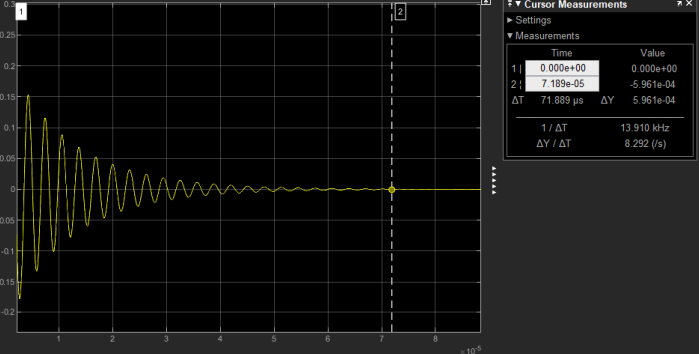

Оценим время установления синхронизации, для этого включим осциллограф после фильтра, чтобы оценить сигнал ошибки.

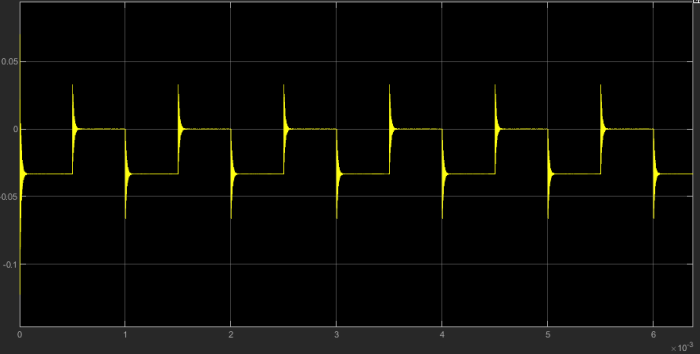

Рисунок 2 – Сигнал ошибки

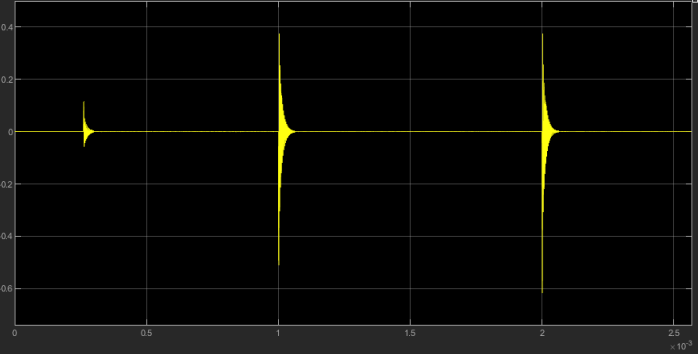

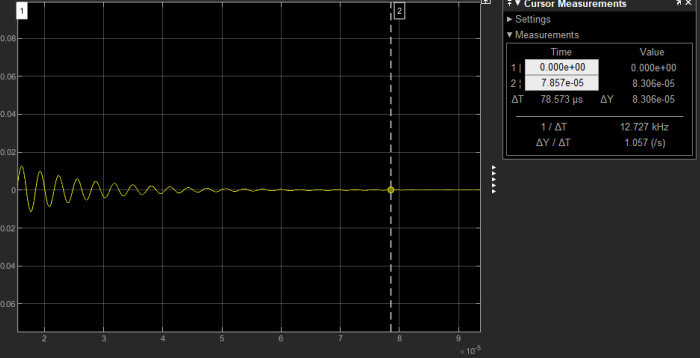

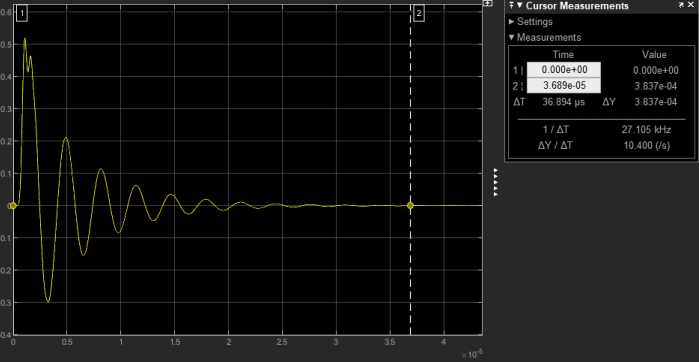

Установим блок variable time delay, чтобы добавить в сигнал задержку. Настроим его таким образом, чтобы задержка в сигнал добавлялась редко, и система успевала подстроить частоту сигнала. Значение задержки генерируется блоком случайных чисел

Рисунок 3 – Сигнал ошибки при наличии периодически добавляющейся задержки

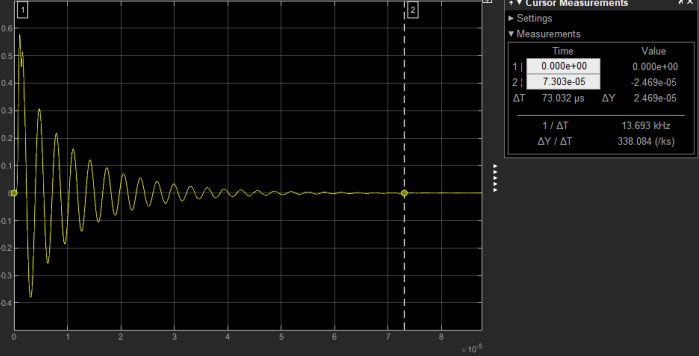

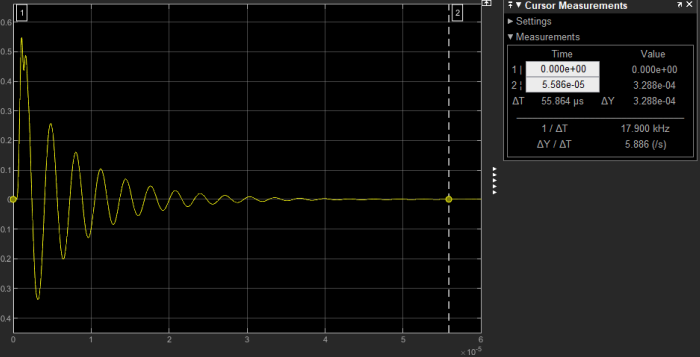

Теперь увеличим частоту появления задержки.

Рисунок 4 – Сигнал ошибки при наличии часто добавляющейся задержки

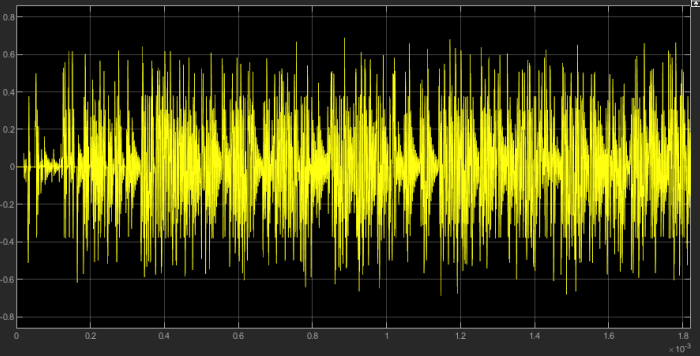

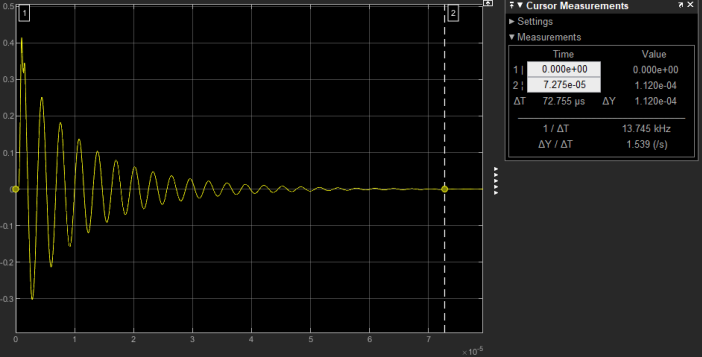

Система не успевает стабилизироваться, следовательно, ФАПЧ не работает. Теперь, будем дискретно изменять частоту

Рисунок 5 – Сигнал ошибки при дискретно изменяющейся частоте

Далее, оценим как зависит длительность переходного процесса от начального фазового рассогласования, частотного рассогласования и коэффициента усиления.

Рисунок 6 – Без фазового рассогласования

Рисунок 7 – Фазовое рассогласование рi/2

Рисунок 8 – Фазовое рассогласование рi/4

Рисунок 9 – Фазовое рассогласование рi/8

Самая большая длительность переходного процесса в схеме без рассогласования. Наименьшая – при отклонении фазы на pi/8.

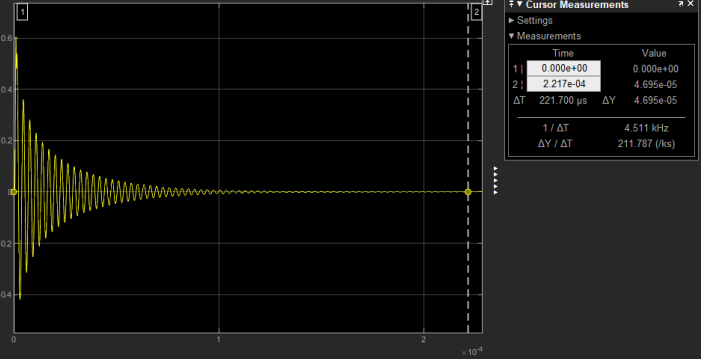

Добавим в схему усиление:

Рисунок 10 – Усиление 0,9

Рисунок 11 – Усиление 0,95

Рисунок 12 – Усиление 1,05

При увеличении коэффициента усиления увеличивается и время переходного процесса.

Вывод:

В данной лабораторной работе была собрана и промоделирована схема ФАПЧ для несущей частоты 0.7 МГц и полосы удержания 10 кГц, как показали моделирования, схема корректно работает в заданном диапазоне. Были проверены основные режимы работы схемы ФАПЧ: синусоидальный входной сигнал, сигнал с фазовыми искажениями. Изучено влияние изменения параметров схемы на скорость подстройки частоты.

2023