Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

ПРИМЕНЕНИЕ РЕГИСТРОВ И СЧЁТЧИКОВ

Отчет по лабораторной работе №7

по дисциплине «Электроника и схемотехника»

Вариант №7

Студент гр. 739-1

![]() Климанов

М. Д.

Климанов

М. Д.

6.06.2021

Руководитель

Доцент БИС

___________ Мальчуков А. Н.

6.06.2021

Томск 2021

Цель работы

Научиться совместно применять регистры и счётчики

Постановка задачи

Для

того чтобы выполнить лабораторную

работу необходимо: составить таблицы

истинности для всех 4-х функций (для 8,

7, 6, 5 вариантов из 1 лабораторной работы:

F5= x

⊕

y∙z

˅w

F6 = x

⊕

y∙ F7=

F7= ,

F8 = x

∙ y⊕z

⊕w

и обозначить в таблице порядок разрядов

(старший и младший). Порядок разрядов

во всех таблицах должен совпадать.

,

F8 = x

∙ y⊕z

⊕w

и обозначить в таблице порядок разрядов

(старший и младший). Порядок разрядов

во всех таблицах должен совпадать.

Для выполнения 4-х параллельных операций над полубайтом необходимо организовать приём и выдачу данных согласно варианту из таблицы (прием: синхронизация по нарастающим фронту, параллельным кодом, младшими разрядами вперед с синхронным сбросом, выдача: синхронизация по убывающему фронту, с последовательной выдачей и активным уровнем сигнала 1). Собрать необходимую схему, используя встроенные блоки регистров (lpm_dff, lpm_shiftreg). Также необходимо создать схемы, которые с помощью регистров обеспечат «чистый» выходной сигнал для асинхронного и синхронного счётчиков своего варианта из ЛБ5(асинхронный, суммирующий счетчик на D триггерах с модулем счета равным 21, синхронный, вычитающий счетчик с убывающим фронтом, асинхронным сбросом и модулем счета равным 26). Промоделировать работу схем в двух режимах. Провести анализ результатов моделирования разных режимов. Сверить результаты моделирования с составленными таблицами истинности. Сделать тоже самое, только для описания устройств вместо схем на холстах .bdf использовать заданный вариантом HDL (VHDL) и написать выводы о проделанной работе.

1. 1. Вычислитель функций

1.1 Таблица истинности

В таблице 1 представлены комбинации нулей и единиц, которые может обработать схема.

Таблица 1 – Вычислитель функций, таблица истинности

Входы |

Выходы |

||||||

F |

|||||||

x |

y |

z |

w |

8 |

7 |

6 |

5 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

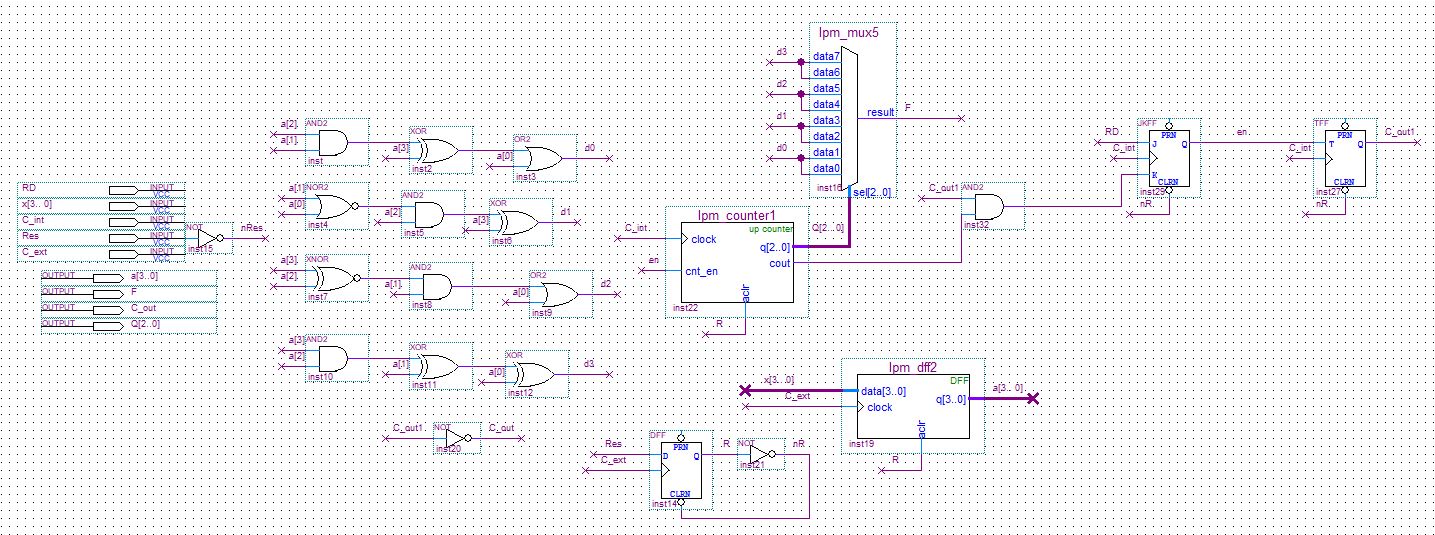

На рисунке 1 представлена функциональная схема «Вычислитель функций». Данные поступают на вход «x» в регистр lmp_shiftreg и для синхронизации по убывающему фронту подана инверсия входа «С_ext». На выходе получается параллельный код, который подается на входы в 4 функции.

Рисунок 1 – Функциональная схема «Вычислитель функций»

1.3 МОДЕЛИРОВАНИЕ

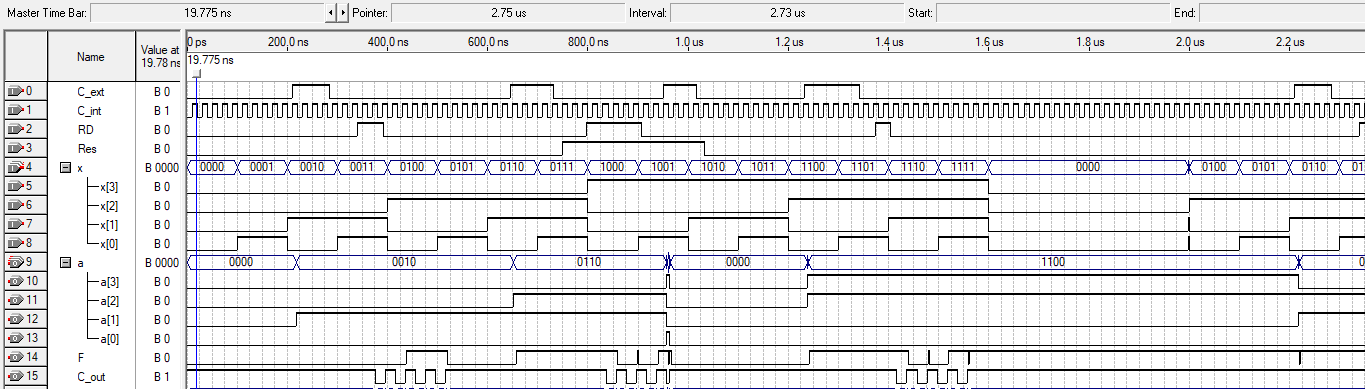

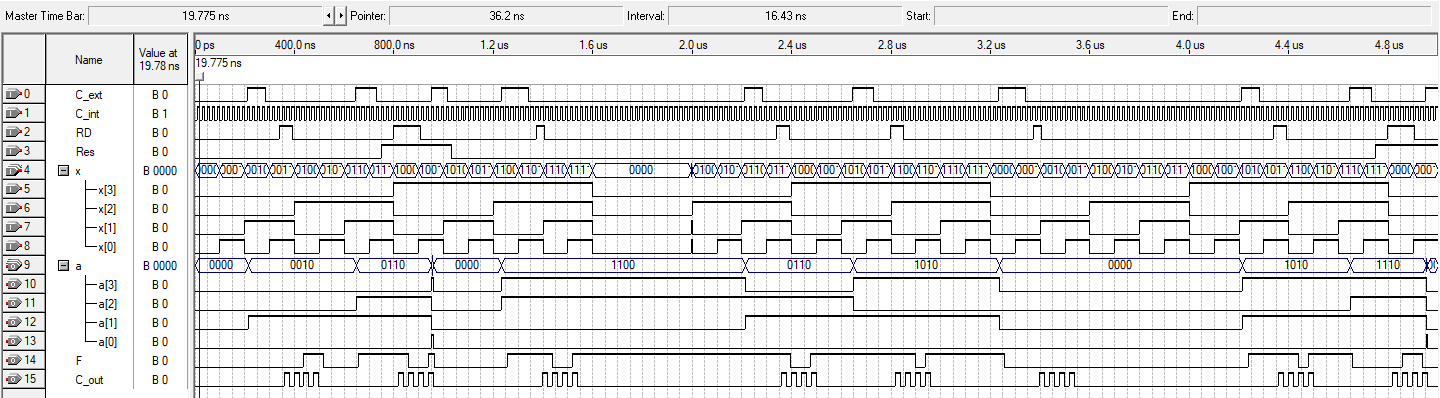

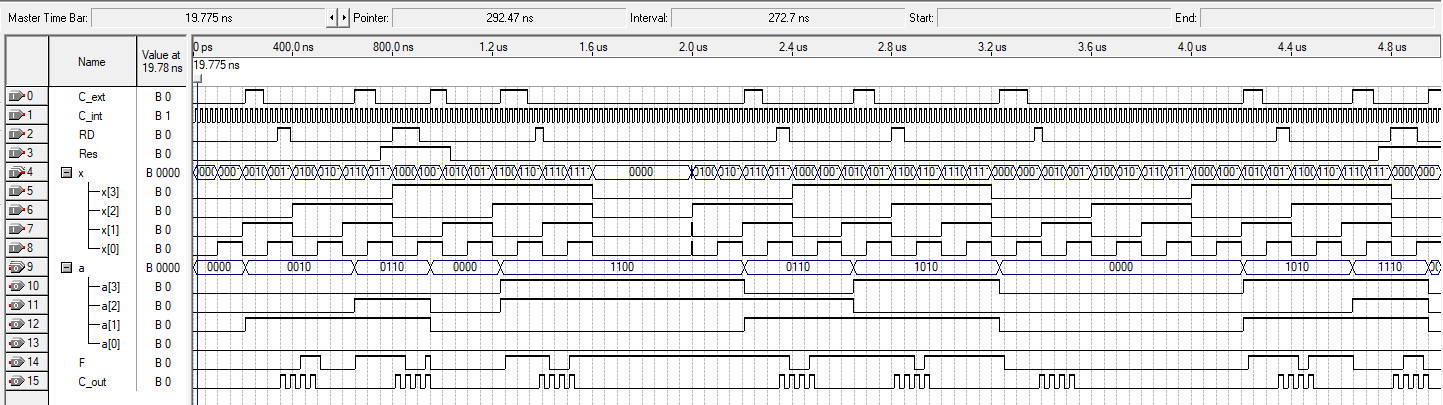

На рисунках 2-3 приведено моделирование функциональной схемы.

Рисунок 2 – Моделирование вычислителя функций, Timing

Рисунок 3 – Моделирование вычислителя функций, Functional

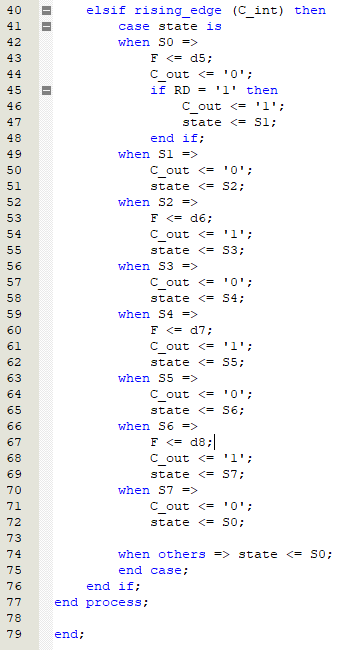

1.4 КОД НА VHDL ДЛЯ ВЫЧИСЛИТЕЛЯ ФУНКЦИЙ.

На языке VHDL написан код для вычислителя функций. Использовалось блочное описание схемы. Код приведен на рисунках 4-5.

Рисунок 4 – Код на VHDL языке для вычислителя функций (часть1)

Рисунок 5 – Код на VHDL языке для вычислителя функций (часть2)

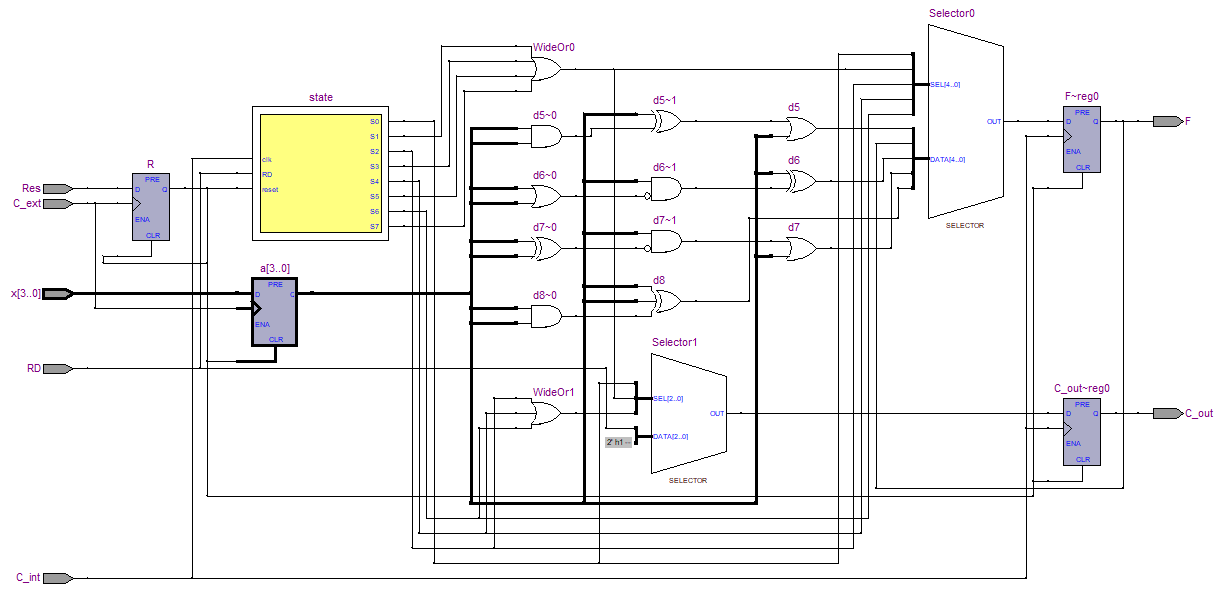

1.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДАVHDL

На рисунке 6 приведена схема, которую собрала программа, на основании кода, описанного в предыдущем пункте.

Рисунок 6 – Схема из RTL VIEWER

1.6 МОДЕЛИРОВАНИЕ КОДА VHDL

На рисунках 7-8 приведено моделирование кода, описанного в пункте 1.4. и приведенного на рисунках 4-5.

Рисунок 7 – Моделирование кода на VHDL, Timing

Рисунок 8 – Моделирование кода на VHDL, Functional

Моделирование кода аналогично моделирование схемы, собранной на .bdf холсте и полностью соответствует таблице истинности.

2. АСИНХРОННЫЙ СЧЁТЧИК С ВЫХОДНЫМ БУФЕРОМ

2.1 ТАБЛИЦА ФУНКЦИОНИРОВАНИЯ

В таблице 2 приведены значения, которые получаются на выходе у асинхронного счетчика.

Таблица 2 – Асинхронный счетчик.

№ сигнала |

Выходы |

||||

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

0 |

1 |

1 |

0 |

7 |

0 |

0 |

1 |

1 |

1 |

8 |

0 |

1 |

0 |

0 |

0 |

9 |

0 |

1 |

0 |

0 |

1 |

10 |

0 |

1 |

0 |

1 |

0 |

11 |

0 |

1 |

0 |

1 |

1 |

12 |

0 |

1 |

1 |

0 |

0 |

13 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

1 |

1 |

1 |

0 |

15 |

0 |

1 |

1 |

1 |

1 |

16 |

1 |

0 |

0 |

0 |

0 |

17 |

1 |

0 |

0 |

0 |

1 |

18 |

1 |

0 |

0 |

1 |

0 |

19 |

1 |

0 |

0 |

1 |

1 |

20 |

1 |

0 |

1 |

0 |

0 |

21 |

0 |

0 |

0 |

0 |

0 |

22 |

0 |

0 |

0 |

0 |

1 |

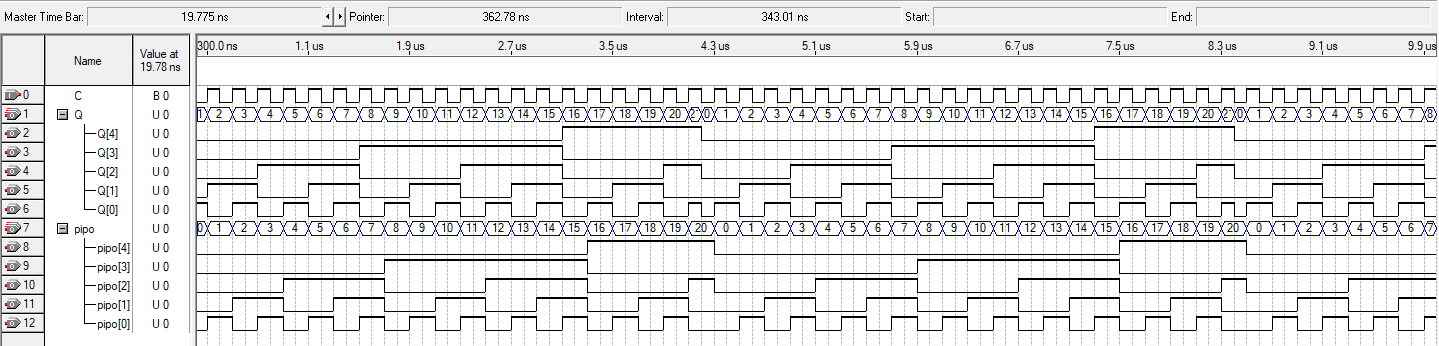

2.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

Асинхронный, суммирующий счетчик строится на D триггерах, все они соединены последовательно. С помощью функций ПО QUARTUS II, был создан символ такого счетчика и собрана схемы для очищения сигнала. Она приведена на рисунке 9.

Рисунок 9 – Функциональная схема, для асинхронного счетчика с выходным буфером

2.3 МОДЕЛИРОВАНИЕ

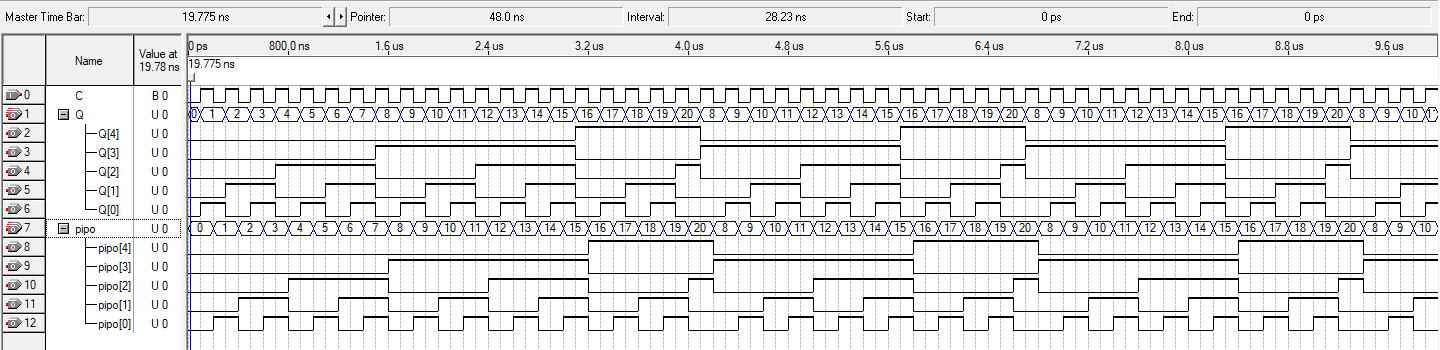

На рисунках 10-11 приведено моделирование схемы в двух режимах.

Рисунок 10 - Моделирование схемы, Timing

Рисунок 11 – Моделирование схемы в режиме, Functional

На рисунках перебор всех значений происходит в соответствии с таблицей функционирования (таблица 2). Все значения совпадают с теми, что прописаны в таблице (В режиме Timing).

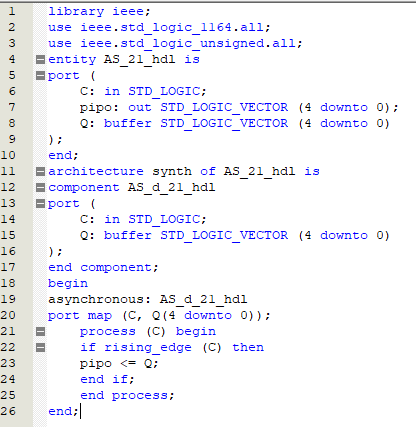

2.4 КОД НА VHDL

На рисунке 12 приведен код для схемы, собранной на .bdf.

Рисунок 12 – Код на VHDL, для асинхронного счетчика

2.5 СХЕМА ИЗ RTL VIEWER

На рисунке 13 приведена схема из RTL VIEWER.

Рисунок 13 – Схема из RTL VIEWER

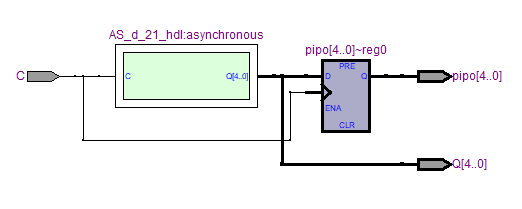

2.6 МОДЕЛИРОВАНИЕ КОДА НА VHDL

НА рисунках 14 - 15 приведено моделирование кода, описанного в пункте 2.4, в разных режимах.

Рисунок 14 – Моделирование кода, режим Timing

Рисунок 15 – Моделирование кода, режим Functional

3. СИНХРОННЫЙ СЧЕТЧИК С ВЫХОДНЫМ БУФЕРОМ

3.1 ТАБЛИЦА ФУНКЦИОНИРОВАНИЯ

В таблице 3 приведены значения, которые может обработать схема.

№ сигнала |

Выходы |

|||||

PR |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

2 |

0 |

1 |

1 |

0 |

0 |

0 |

3 |

0 |

1 |

0 |

1 |

1 |

1 |

4 |

0 |

1 |

0 |

1 |

1 |

0 |

5 |

0 |

1 |

0 |

1 |

0 |

1 |

6 |

0 |

1 |

0 |

1 |

0 |

0 |

7 |

0 |

1 |

0 |

0 |

1 |

1 |

8 |

0 |

1 |

0 |

0 |

1 |

0 |

9 |

0 |

1 |

0 |

0 |

0 |

1 |

10 |

0 |

1 |

0 |

0 |

0 |

0 |

11 |

0 |

0 |

1 |

1 |

1 |

1 |

12 |

0 |

0 |

1 |

1 |

1 |

0 |

13 |

0 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

0 |

1 |

1 |

0 |

0 |

15 |

0 |

0 |

1 |

0 |

1 |

1 |

16 |

0 |

0 |

1 |

0 |

1 |

0 |

17 |

0 |

0 |

1 |

0 |

0 |

1 |

18 |

0 |

0 |

1 |

0 |

0 |

0 |

19 |

0 |

0 |

0 |

1 |

1 |

1 |

20 |

0 |

0 |

0 |

1 |

1 |

0 |

21 |

0 |

0 |

0 |

1 |

0 |

1 |

22 |

0 |

0 |

0 |

1 |

0 |

0 |

23 |

0 |

0 |

0 |

0 |

1 |

1 |

24 |

0 |

0 |

0 |

0 |

1 |

0 |

25 |

0 |

0 |

0 |

0 |

0 |

1 |

26 |

0 |

0 |

0 |

0 |

0 |

0 |

27 |

0 |

1 |

1 |

0 |

0 |

1 |

28 |

0 |

1 |

1 |

0 |

0 |

0 |

29 |

1 |

1 |

1 |

0 |

0 |

1 |

30 |

0 |

1 |

1 |

0 |

0 |

0 |

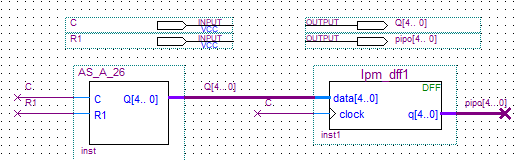

3.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

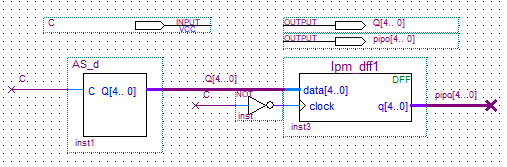

На рисунке 16 приведена функциональная схема синхронного счетчика с выходным буфером.

Рисунок 16 - Функциональная схема синхронного счетчика с выходным буфером

Для синхронного счетчика был создан символ и назван AS_A_26. Выходные значения счетчика подаются на выход в регистр lpm_dff и в результате получается «чистый» сигнал. Результат работы схемы приведен в пункте 3.3

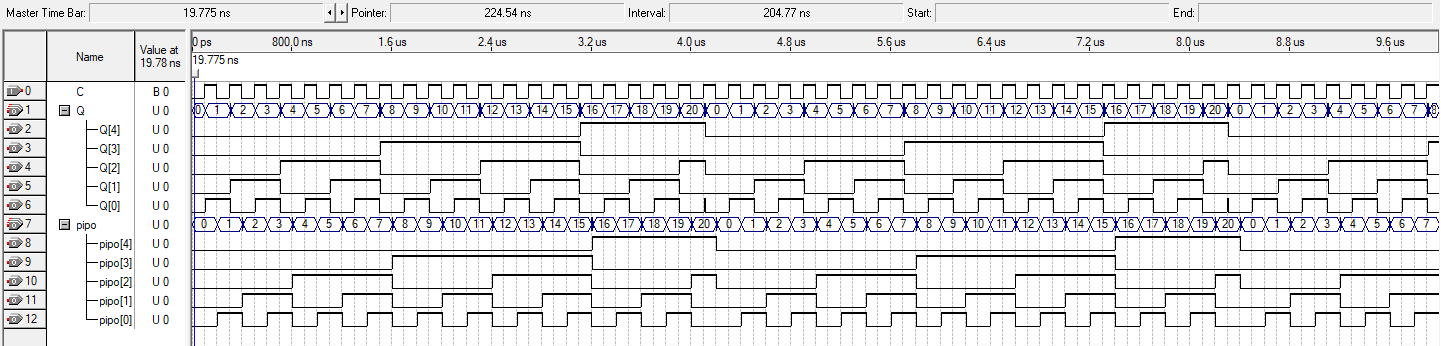

3.3 МОДЕЛИРОВАНИЕ

На рисунках 17-18 приведено моделирование схемы в двух режимах.

Рисунок 17 – Моделирование схемы, режим Timing

Рисунок 18 – Моделирование схемы, режим Functional

3.4 КОД НА VHDL

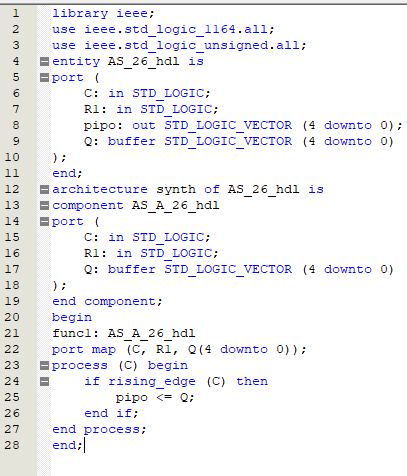

На рисунке 19 приведен код для схемы, собранной на .bdf холстах. Из рисунка 19 видно, что использовалось модульное подключение т.е. реализация счетчиков на VHDL, скрыта.

Рисунок 19 – Код на VHDL

3.5 СХЕМА ИЗ RTL VIEWER

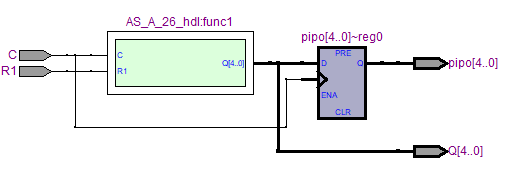

На рисунке 20 приведена схема из RTL viewer.

Рисунок 20 – Схема из RTL viewer

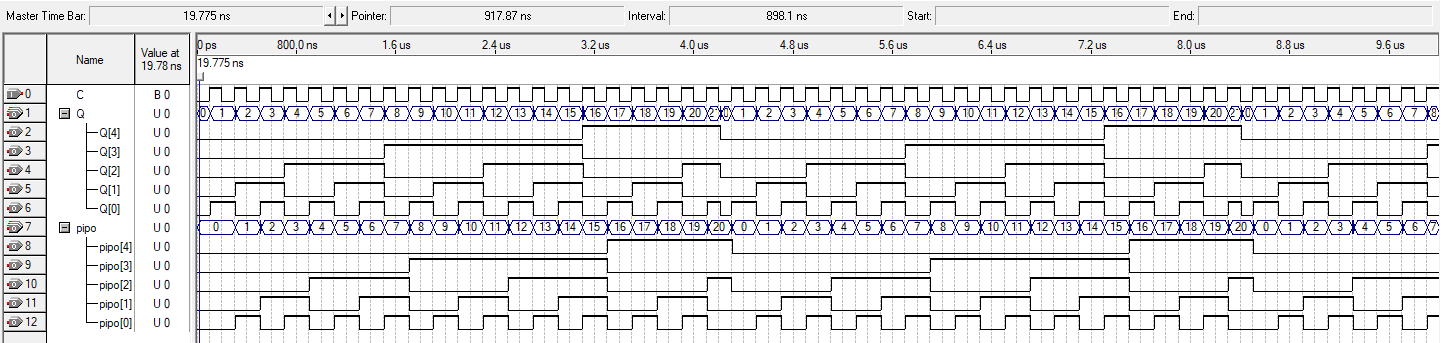

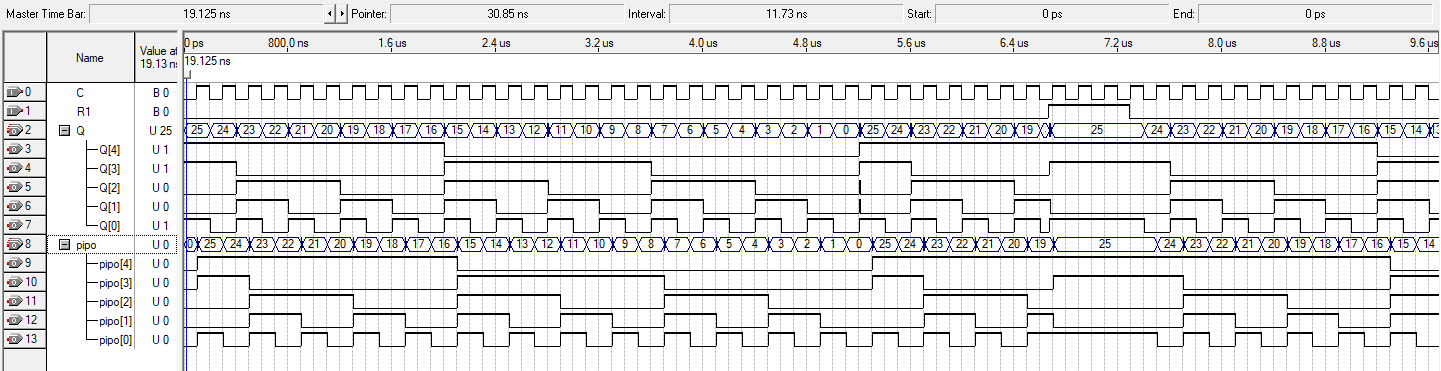

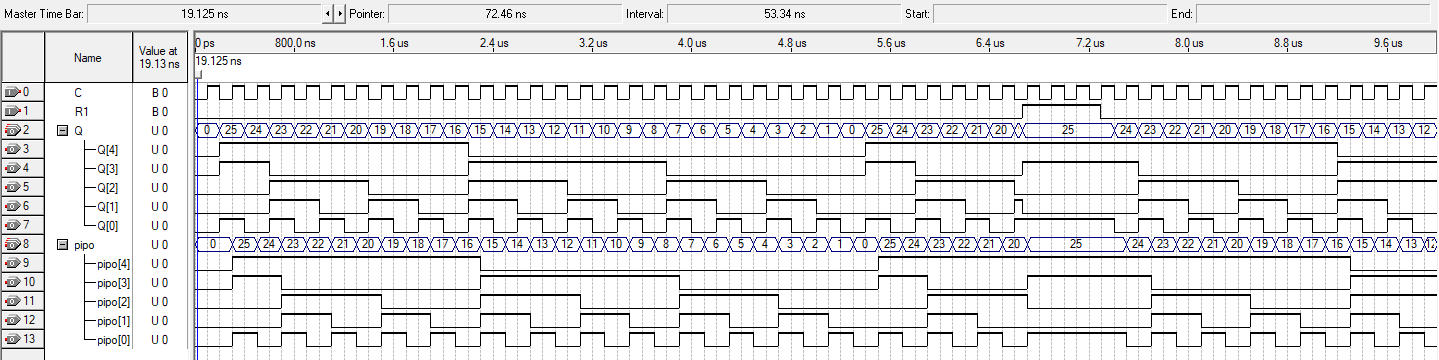

3.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ VHDL

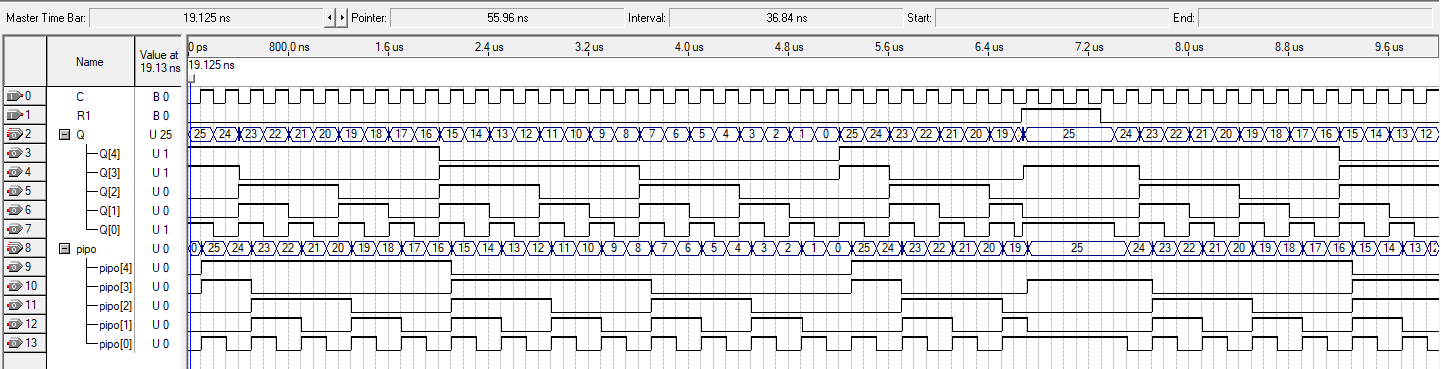

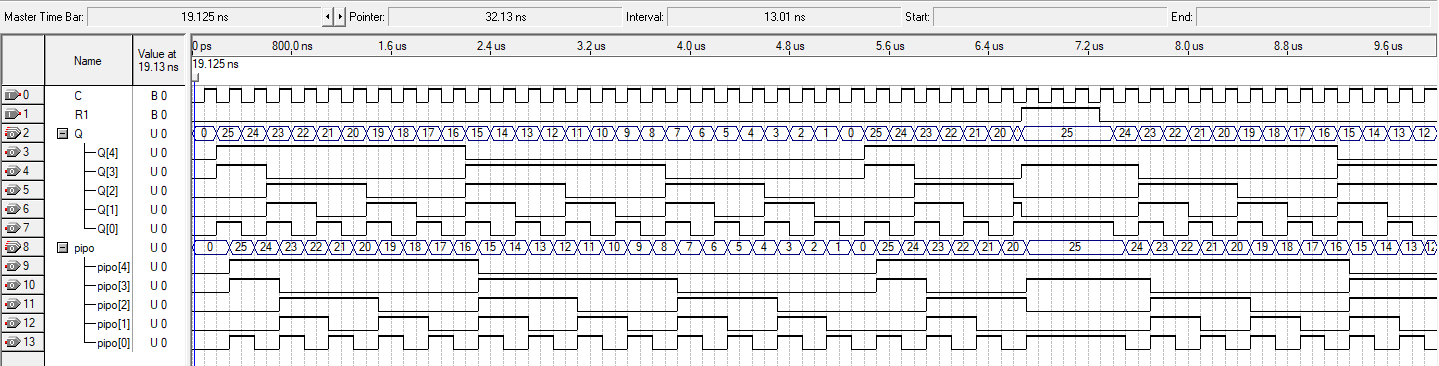

На рисунках 21 – 22 приведено моделирование кода.

Рисунок 21 – Моделирование кода на VHDL, режим Timing

Рисунок 22 – Моделирование кода на VHDL, режим Functional

Моделирование кода аналогично моделированию схемы на .bdf холстах. В обоих случаях моделирование совпадает с таблицей истинности и получается ожидаемый результат.

4. ЗАКЛЮЧЕНИЕ

В результате выполнения лабораторной работы были составлены таблицы истинности для всех 4-х функций (для 8, 7, 6, 5 вариантов из 1 лабораторной работы: F5= x ⊕ y∙z ˅w F6 = x ⊕ y∙ F7= , F8 = x ∙ y⊕z ⊕w. В таблицах обозначены порядки разрядов (старший и младший). Порядок разрядов во всех таблицах совпадает.

Для выполнения 4-х параллельных операций над полубайтом организован приём и выдача данных согласно варианту из таблицы прием: синхронизация по нарастающим фронту, параллельным кодом, младшими разрядами вперед с синхронным сбросом, выдача: синхронизация по убывающему фронту, с последовательной выдачей и активным уровнем сигнала 1). Схема была собрана, используя встроенные блоки регистров (lpm_dff, lpm_shiftreg). Также созданы схемы, обеспечивающие «чистый» выходной сигнал для асинхронного и синхронного счётчиков своего варианта из ЛБ5 (асинхронный счетчик: суммирующий, с модулем счета 21 на D триггерах, синхронный: вычитающий с нарастающим фронтом, с синхронным сбросом и модулем счета 26).

Проведено моделирование работы схем в двух режимах и проведен анализ результатов моделирования. Результаты моделирования сравнивались с составленными таблицами истинности и получен ожидаемый результат. Сделано также тоже самое, только для описания устройств вместо схем на холстах .bdf использовался заданный вариантом HDL (VHDL). Результаты аналогичны тем, что получены с помощью схем составленных на .bdf холстах.