2 семестр / ЭИС4.2

.docxМинистерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ ТРИГГЕРОВ

Отчет по лабораторной работе №4

по дисциплине «Электроника и схемотехника»

Вариант №7

Студент гр. 739-1

![]() Климанов

М. Д.

Климанов

М. Д.

11.04.2021

Руководитель

Доцент БИС

___________ Мальчуков А.Н.

11.04.2021

Томск 2021

ЦЕЛЬ РАБОТЫ

Изучить основные типы триггеров, их принципы построения и работы.

ПОСТАНОВКА ЗАДАЧИ

В ходе данной лабораторной работы требуется выполнить следующие задачи:

1. Составить таблицы функционирования для схем из таблицы согласно 7 варианту. В таблице подписать режимы работы триггера.

2. Соберать схемы заданных триггеров согласно варианту.

3. Промоделировать работу всех схем в двух режимах и исследовать минимальный порог длительности активного уровня управляющего сигнала. Провести анализ результатов моделирования разных режимов.

4. Сверить результаты моделирования с составленными таблицами функционирования.

5. Повторить п. 2-4, только для описания устройств вместо схем на холстах .bdf использовать заданный 7 вариантом HDL.

6. Написать выводы о проделанной работе.

1 s1-JK ТРИГГЕР В БАЗИСЕ И-НЕ

1.1 Таблица истинности

В таблице 1 представлены комбинации нулей и единиц, которые может обработать схема.

Таблица 1 – s1-JK триггер.

s1-JK |

|||||||

Вход |

Выход |

Переход |

|||||

J |

K |

C |

Q(t) |

Q(t+1) |

|||

X |

X |

0 |

0/1 |

0/1 |

хранение |

||

0 |

1 |

1 |

X |

0 |

установка в 0 |

||

1 |

0 |

1 |

X |

1 |

установка в 1 |

||

1 |

1 |

1 |

1 |

0 |

счётный из 1 в 0 |

||

1 |

1 |

1 |

0 |

1 |

счётный из 0 в 1 |

||

1.2 Функциональная схема

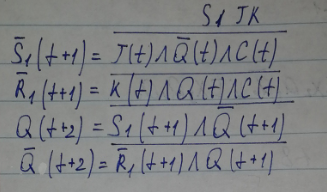

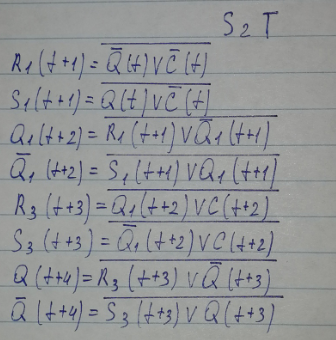

Ниже представлен рисунок 1 с формулами для s1-JK триггера.

Рисунок 1 - Формулы для s1-JK триггера

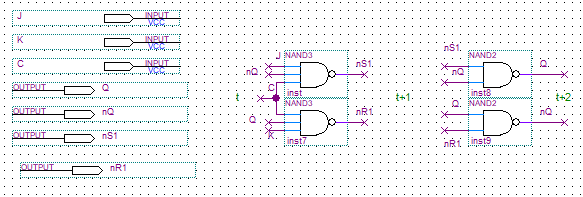

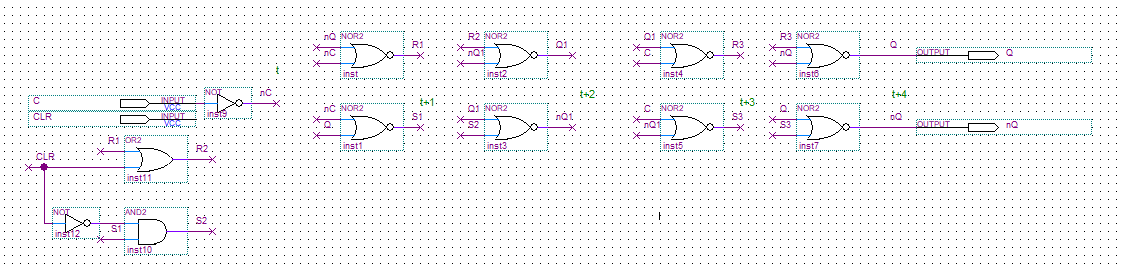

1.3 Функциональная схема

На рисунке 2 представлена функциональная схема s1-JK триггера, составленная на основе формулы из прошлого пункта.

Рисунок 2 – Функциональная схема s1-JK триггер

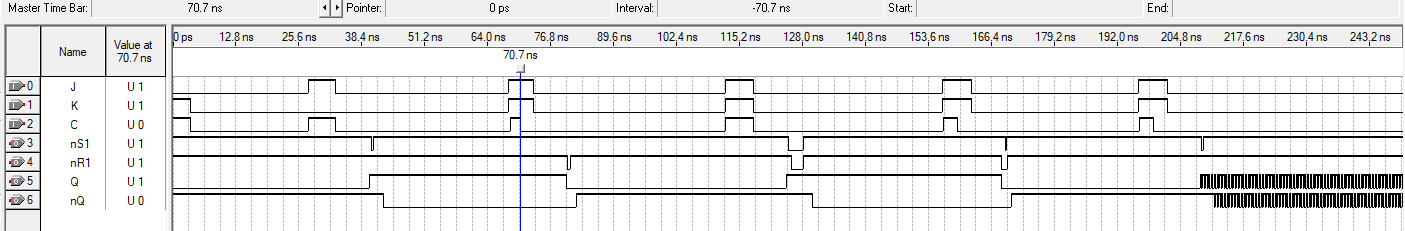

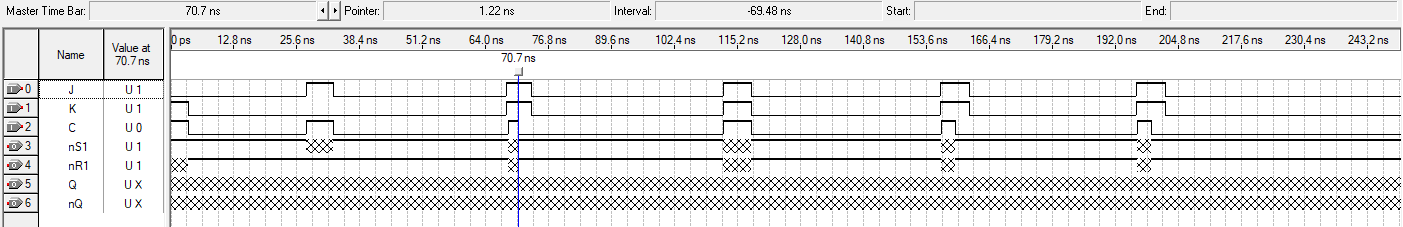

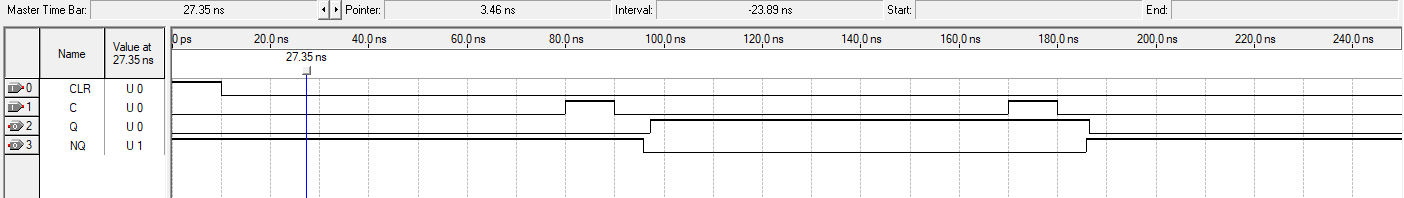

1.4 Моделирование функциональной схемы

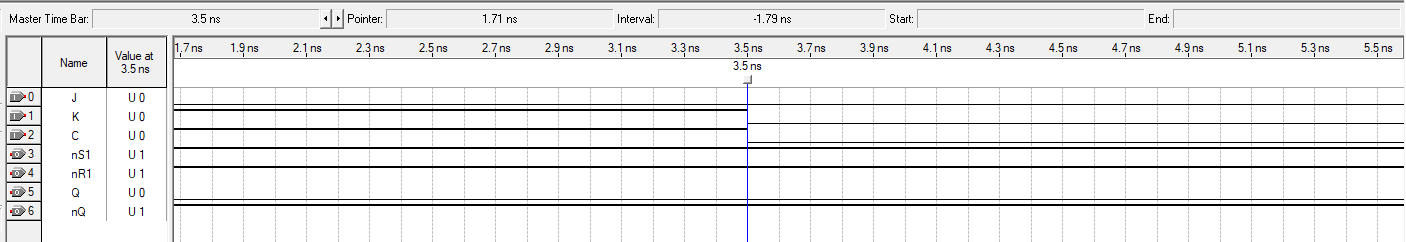

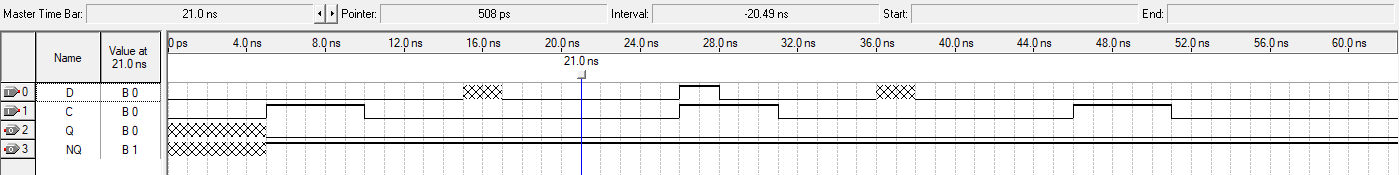

На рисунках 3 - 4 представлены результаты временного и функционального моделирований s1-JK триггер.

Рисунок 3 – Результат временного моделирования s1-JK триггер

Рисунок 4 – Результат функционального моделирования s1-JK триггер

В режиме без учета задержки результаты моделирование не соответствуют таблице истинности из-за того, что происходит зацикливание моделирования. В режиме Timing результаты вырны.

Также необходимо исследовать минимальный порог длительности активного уровня управляющего сигнала. При значении 3.5 ns схема работает стабильно и выдает ожидаемый результат рисунок 4.

Рисунок 4 – Работа s1-JK триггера при длительности сигнала 3.5 ns

1.5 Код на HDL

Ниже представлен код описания s2-JK триггера на System Verilog.

module s2_JK_SV (

input J,K,C, PR, CLR,

output Q,nQ);

logic nS1, nS2, nR1, nR2, Q1, nQ1;

assign nS1 = ~(J & nQ & C);

assign nR1 = ~(K & Q & C);

assign Q1 = ~(nS1 & nQ1 & ~PR);

assign nQ1 = ~(nR1 & Q1 & ~CLR);

assign nS2 = ~(Q1 & ~C);

assign nR2 = ~(nQ1 & ~C);

assign Q = ~(nS2 & nQ);

assign nQ = ~(nR2 & Q);

endmodule

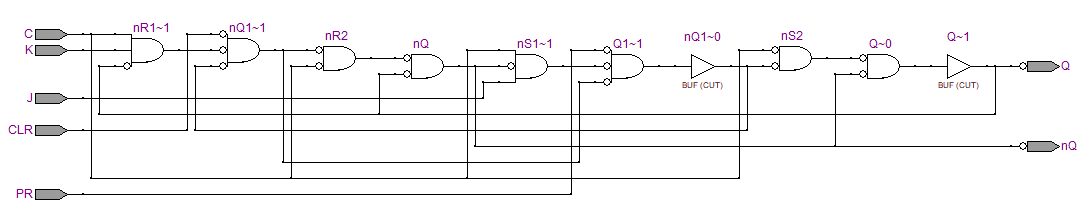

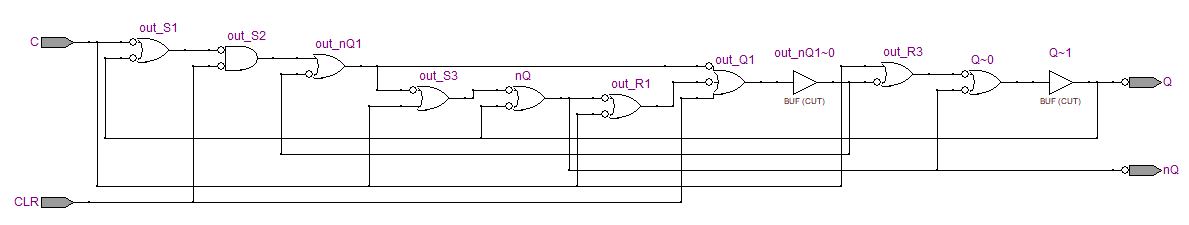

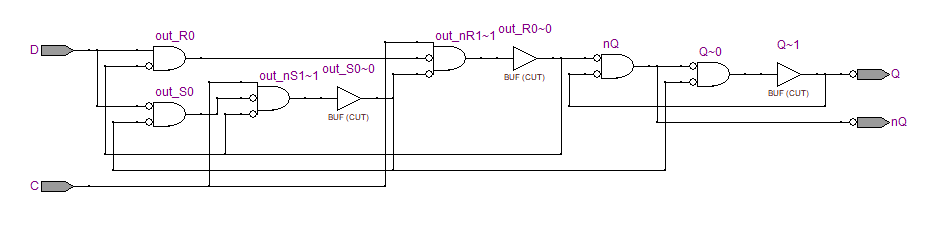

1.6 Схема из RTL viewer для кода HDL

На рисунке 5 представлена схема из RTL viewer для System Verilog кода. Данная схема соответствует функциональной схеме, составленной ранее.

Рисунок 5 – Схема из RTL viewer

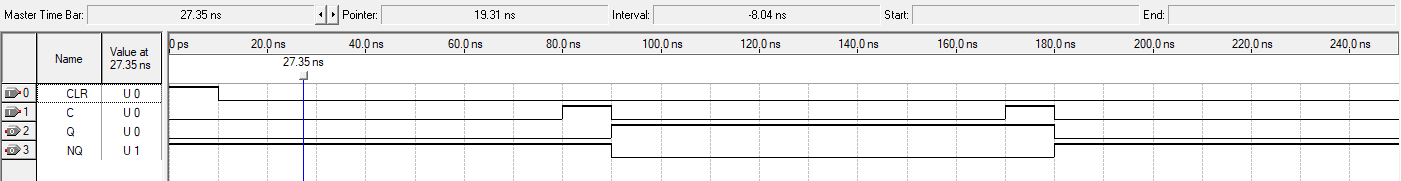

1.7 Моделирование устройства, описанного кодом HDL.

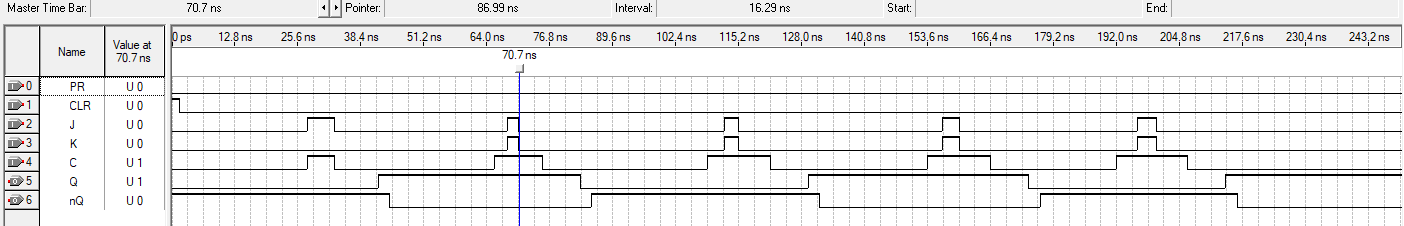

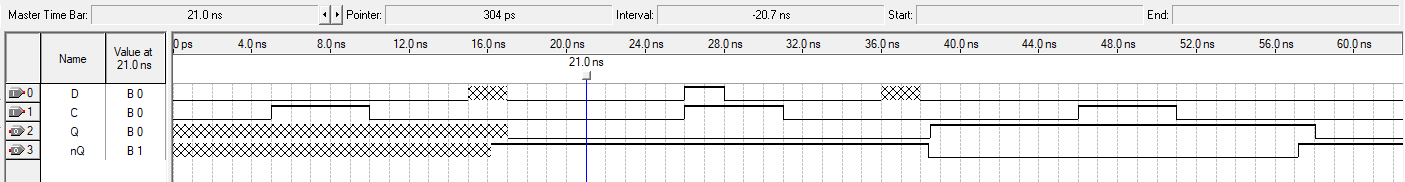

На рисунке 6-7 представлены результаты временного и функционального моделирований s2-JK триггера, описанного на System Verilog.

Рисунок 6 – Результат временного моделирования s2-JK триггера, описанного на System Verilog

Рисунок 7 – Результат функционального моделирования s2-JK триггера, описанного на System Verilog

Необходимо исследовать минимальную длительность сигнала рисунок 8.

Рисунок 8 - Работа s2-JK d триггера при длительности сигнала 27.5 ns

2. s2-T ТРИГГЕР НА БАЗИСЕ ИЛИ-НЕ

2.1 Таблица истинности

Таблица 2 – комбинации нулей и единиц для s2-T триггера.

Таблица 2 – s2-T триггер

s2-T |

|||

Входы |

Выходы |

Состояние |

|

С(t) |

Q(t) |

Q(t+1) |

|

0-0 |

0 |

0 |

Хранение |

0 |

1 |

1 |

Хранение |

1 |

0 |

1 |

Счетный 0→1 |

1 |

1 |

0 |

Счетный 1→0 |

2.2 Формула

Ниже представлен рисунок 9 с формулами схемы для s2-T триггера.

Рисунок 9 – Формулы схемы для s2-T триггера

2.3 Функциональная схема

На рисунке 10 представлена функциональная схема s2-T триггера, составленная на основе формул из прошлого пункта.

Рисунок 10 – Функциональная схема s2-T триггера

2.4 Моделирование функциональной схемы

На рисунке 11 - 12 представлены результаты временного и функционального моделирования s2-T триггера.

Рисунок 11 – Результат временного моделирования s2-T триггера

Рисунок 12 – Результат функционального моделирования s2-T триггера

2.5 Код на HDL

Ниже представлен код описания s2-T триггера на System Verilog.

module s2_T_SV (

input CLR,C,

output Q,nQ);

logic out_nC, out_S1, out_R1, out_Q1, out_nQ1, out_S2, out_R2, out_R3, out_S3, out_nCLR;

assign out_nC= ~C;

assign out_nCLR=~CLR;

assign out_R1 = ~(nQ | out_nC);

assign out_S1 = ~(Q | out_nC);

assign out_R2 = out_R1 | CLR;

assign out_S2 = out_S1 & out_nCLR;

assign out_Q1 = ~(out_R2 | out_nQ1);

assign out_nQ1 = ~(out_S2 | out_Q1);

assign out_R3 = ~(out_Q1 | C);

assign out_S3 = ~(out_nQ1 | C);

assign Q = ~(out_R3 | nQ);

assign nQ = ~(out_S3 | Q);

endmodule

2.6 Схема из RTL viewer для кода HDL

На рисунке 13 представлена схема из RTL viewer для кода, написанном на System Verilog. Данная cхема соответствует функциональной схеме, составленной ранее.

Рисунок 13 – Схема из RTL viewer для кода s2-T триггера

2.7 Моделирование устройства, описанного кодом HDL

На рисунке 14 - 15 представлены результаты временного и функционального моделирования s2-T триггера.

Рисунок 14 – Результат временного моделирования s2-T триггера, описанного на System Verilog

Рисунок 15 – Результат функционального моделирования s2-T триггера, описанного на System Verilog

3 d-D триггер, на базисе И - НЕ

3.1 Таблица истинности

В таблице 3 представлены значения, которые может обработать схема.

Таблица 3 – Таблица истинности, d-D триггер

d-D |

||||

Входы |

Выходы |

Состояние |

||

D |

C |

Q(t) |

Q(t+1) |

|

X |

0 |

0/1 |

0/1 |

Хранение |

1 |

1 |

0 |

1 |

Установка в 1 |

0 |

1 |

1 |

0 |

Установка в 0 |

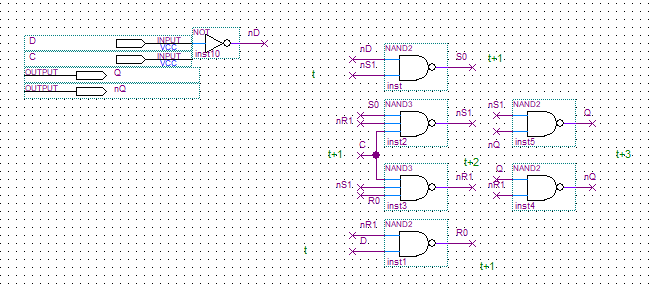

3.2 Функциональная схема

На рисунке 16 представлена функциональная схема d-D триггера

Рисунок 16 – Функциональная схема d-D триггера

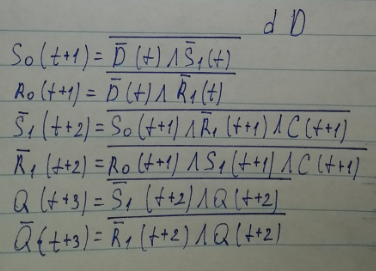

3.3 Формула

Ниже представлен рисунок 17 с формулами схемы для d-D триггера.

Рисунок 17 – формулы схемы для d-D триггера

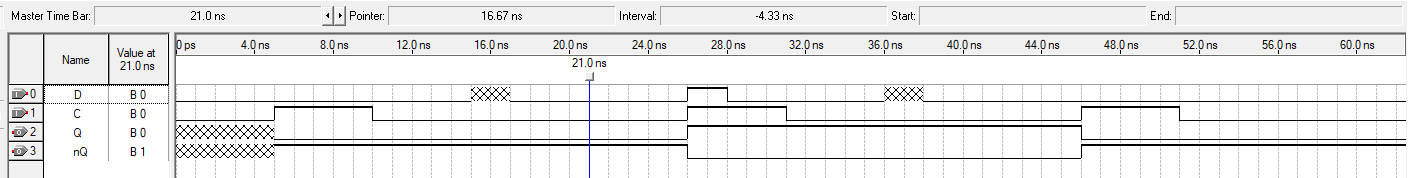

3.4 Моделирование функциональной схемы

На рисунке 18 - 19 представлены результаты временного и функционального моделирования d-D триггера.

Рисунок 18 – Результат временного моделирования логической функции на основе d-D триггера

Рисунок 19 – Результат функционального моделирования логической функции на основе d-D триггера

В режиме без учета задержки результаты моделирование не соответствуют таблице истинности, это происходит из-за, зацикливания моделирования. В режиме Timing результаты верны.

3.5 КОД НА SYSTEM VERILOG d-D триггера

Код для d-D триггера представлен ниже.

module d_D_SV (

input D,C,

output Q,nQ);

logic out_nD, out_S0, out_R0, out_nS1, out_nR1, out_R3, out_S3, out_nCLR;

assign out_nD= ~D;

assign out_S0 = ~(out_nD & out_nS1);

assign out_R0 = ~(D & out_nR1);

assign out_nS1 = ~(out_S0 & out_nR1 & C);

assign out_nR1 = ~(out_R0 & out_nS1 & C);

assign Q = ~(out_nS1 & nQ);

assign nQ = ~(out_nR1 & Q);

endmodule

3.6 СХЕМА ИЗ RTL VIEWER d-D триггера

Схема из RTL VIEWER указана на рисунке 20

Рисунок 20 – Схема из RTL VIEWER d-D триггера

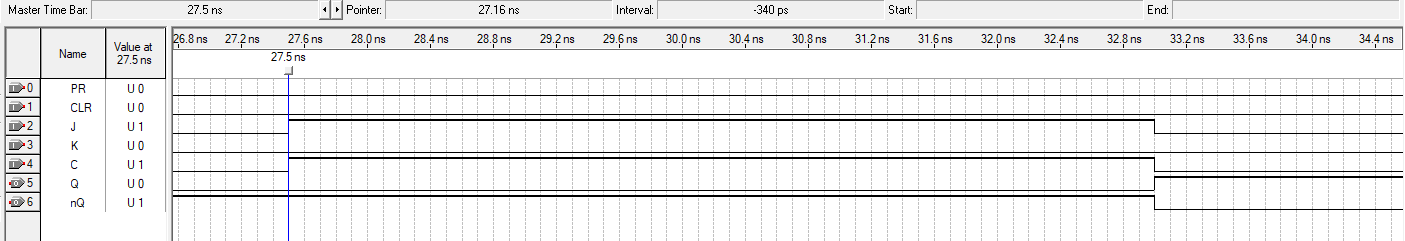

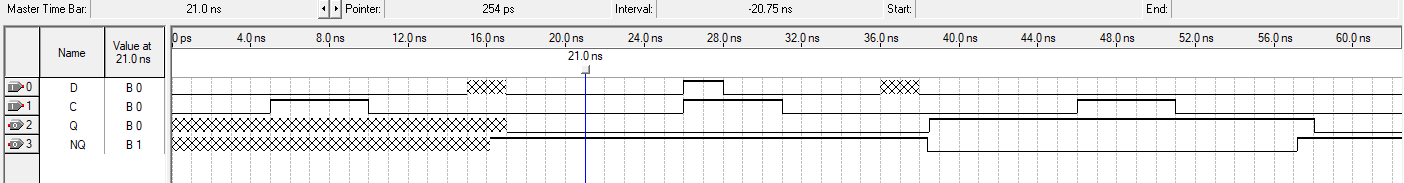

3.7 МОДЕЛИРОВАНИЕ КОДА НА SYSTEM VERILOG

На рисунках 21, 22 представлены результаты моделирования схемы.

Рисунок 21 – Результат временного моделирования логической функции на основе d-D триггера

Рисунок 22 – Результат функционального моделирования логической функции на основе d-D триггера

В режиме без учета задержки результаты моделирование не соответствуют таблице истинности, это происходит из-за, зацикливания моделирования. В режиме Timing результаты верны.

ВЫВОДЫ

В результате выполнения лабораторной работы было выполнено:

Собраны схемы для s1-JK триггера на базисе И – НЕ.

Собраны схемы для s2-T триггера ИЛИ – НЕ.

Собраны схемы для d-D триггера И – НЕ.

Каждая схема была промоделирована при помощи временных диаграмм.

Все выше перечисленные пункты были выполнены в виде кода на System Verilog и схемы брались из RTL viewer. Результаты получились точно такие же.

Отчет был оформлен согласно требованиям ОС ТУСУР 2013.