КР пуму 2ой сем

.pdf

Министерство образования Республики Беларусь Учреждение образования

«Белорусский государственный университет информатики и радиоэлектроники»

КОНТРОЛЬНАЯ РАБОТА

Студент: Дашкевич А. А.

гр. 790241

Вариант 7

Минск 2021

Задание 1

Цель работы: Спроектировать логическую схему при помощи графического редактора САПР MAX+PLUS II. Исследовать работу схемы с использованием сигнального редактора САПР MAX+PLUS II.

Ход работы:

1. Необходимо синтезировать электрическую принципиальную схему логического устройства, описанного заданным преподавателем уравнением в алгебраической форме в соответствии с прил. 1. Для варианта № 7 ФАЛ:

Y =(BD +CA)D

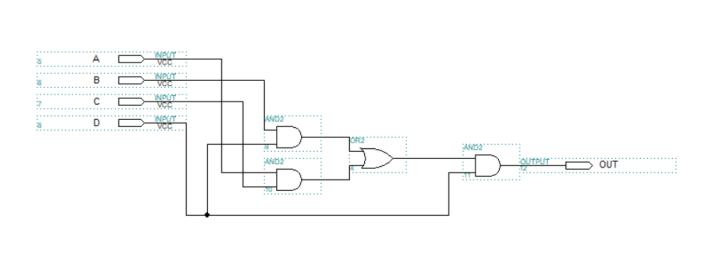

Полученная схема в графическом редакторе САПР MAX+PLUS II, будет выглядеть так:

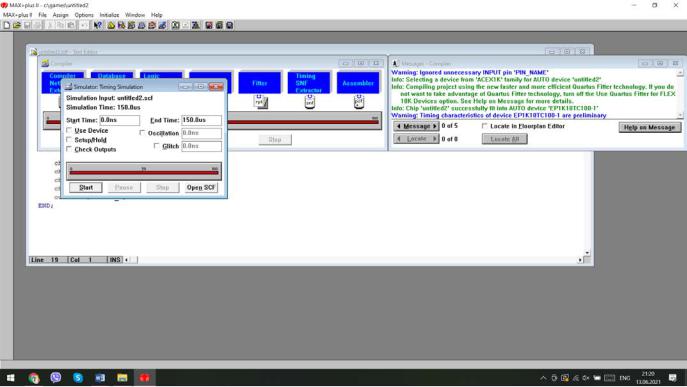

2. Далее необходимо произвести симуляцию работы схемы. Зарисовать диаграммы работы и по ее результатам заполнить таблицу истинности смоделированной схемы.

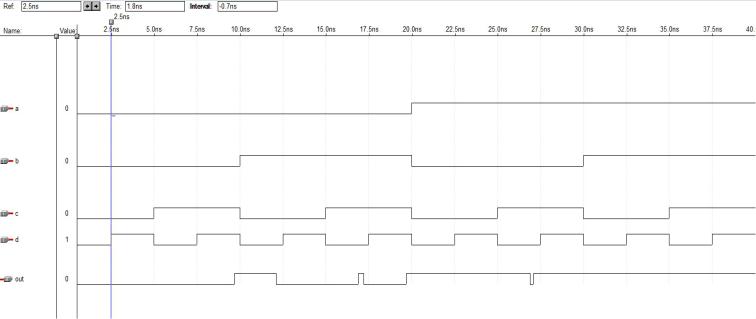

Временные диаграммы работы синтезированной схемы:

Заполним таблицу истинности:

A |

B |

C |

D |

Y |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

Вывод: В ходе работы мы реализовали проект цифровой схемы в графическом редакторе САПР MAX+PLUS, получили временные диаграммы и таблицу истинности. Можно сделать вывод, что ФАЛ любой сложности можно реализовать при помощи графического редактора САПР MAX+PLUS II.

1

Контрольные вопросы:

1. Назовите основные логические (булевы) функции и изобразите элементы их реализующие. Для каждой из функции запишите таблицу истинности.

Основными логическими функциями являются: - логическое отрицание (инверсия):

Y = X ;

- логическое сложение (дизъюнкция):

Y = X1 + X 2 или Y = X1 X2 ;

- логическое умножение (конъюнкция):

Y = X1 • X 2 или Y = X1 X 2 .

На рис. 1 показан элемент «НЕ», который реализует функцию логического отрицания X Y =.

X 1 Y

X |

Y |

1 |

0 |

|

|

0 |

1 |

Рис. 1 Элемент «НЕ»

Элемент «ИЛИ» (рис. 2) и элемент «И» (рис. 3) реализуют функции логического сложения и логического умножения соответственно.

X1 |

|

|

|

X1 |

X2 |

Y |

|

|

Y |

0 |

0 |

0 |

|||

X2 |

1 |

1 |

0 |

1 |

|||

0 |

1 |

1 |

|||||

|

|

|

|||||

|

|

|

|

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

Рис. 2 Элемент «ИЛИ»

2

X1 |

|

|

|

|

|

X1 |

X2 |

Y |

|

|

Y |

|

0 |

0 |

0 |

||||

& |

|||||||||

X2 |

0 |

1 |

0 |

||||||

|

|

|

|

|

1 |

0 |

0 |

||

|

|

|

|

|

1 |

1 |

1 |

||

|

|

|

|

|

|

|

|

|

|

Рис. 3 Элемент «И»

2. Перечислите логические элементы, доступные в библиотеке примитивов графического редактора MAX+PLUS II.

and2, and3, and4, or2, or4, not, nand2, nor2 и т.д.

3.Укажитепроцессы,протекающиевсистемеприкомпиляциипроекта.

Compiler Netlist Extractor – Database Builder – Logic Synthesizer – Partitioner –Fitter – Timing SNF Extractor - Assembler

4. Объясните результаты моделирования работы схемы лабораторной работы.

По результатам работы были получены точные данные, как и в таблице истинности.

3

Задание 2

Цель работы: Приобрести основные навыки описания цифровых схем с помощью языка описания аппаратуры AHDL. Смоделировать логическую схему при помощи текстового редактора САПР MAX+PLUS II.

Ход работы:

Согласно прошлой лабораторной работы для варианта № 7 ФАЛ:

Y=(BD +CA)D

1.Необходимо сделать описание электрической схемы заданной в предыдущей работе при помощи текстового редактора САПР MAX+PLUS II.

Файл .tdf: |

|

SUBDESIGN untitled3 |

|

( |

|

a, b, c, d |

: INPUT; |

out |

: OUTPUT; |

) |

|

4

VARIABLE |

|

check_1 |

: NODE; |

check_2 |

: NODE; |

check_3 |

: NODE; |

BEGIN |

|

check_1 = b & c; check_2 = a & c;

check_3 = check_1 # check_2 ; out = check_3 & d;

END;

Файл .fit:

CHIP "untitled3" BEGIN

DEVICE = "EP1K10TC100-1";

"a" |

: INPUT_PIN = 38 |

; |

"b" |

: INPUT_PIN = 91 |

; |

"c" |

: INPUT_PIN = 89 |

; |

"d" |

: INPUT_PIN = 40 |

; |

"out" |

: OUTPUT_PIN = 23 |

; |

":40" |

: LOCATION = LC7_C23; |

|

END;

5

INTERNAL_INFO "untitled3" BEGIN

DEVICE = EP1K10TC100-1;

OD2P38 : LORAX = "1:FB2|2:FH2R2,PA6R2C22->LC7_C23||"; OD0P91 : LORAX = "1:FB0|2:FH0R2,PA0R2C22->LC7_C23||"; OD1P89 : LORAX = "1:FB1|2:FH1R2,PA20R2C22->LC7_C23||"; OD3P40 : LORAX = "1:FB3|2:FH3R2,PA5R2C22->LC7_C23||"; LC7_C23 : LORAX = "1:MSW6R2C23,G70R2->OH6R2P23|";

LC7_C23 : LORAX2 = "OD0P91, OD1P89, OD2P38, OD3P40";

END;

2. Далее необходимо произвести симуляцию работы схемы. Зарисовать диаграммы работы и по ее результатам заполнить таблицу истинности смоделированной схемы.

Временные диаграммы работы синтезированной схемы:

Заполним таблицу истинности:

A |

B |

C |

D |

Y |

1 |

1 |

1 |

0 |

0 |

6

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

Вывод: Приобретены основные навыки описания цифровых схем с помощью языка описания аппаратуры AHDL. Смоделирована логическая схема при помощи текстового редактора САПР MAX+PLUS II. При этом был получен тот же результат, что и в прошлой лабораторной работе.

Контрольные вопросы:

1. Дайте определение языка описания аппаратуры. Назовите существующие языки описания аппаратуры, укажите их отличия.

Язык описания аппаратуры AHDL разработан фирмой Altera и предназначен для описания комбинационных и последовательностных логических устройств, групповых операций, цифровых автоматов (state machine) и таблиц истинности с учетом архитектурных особенностей ПЛИС фирмы Altera.

Основные |

практически |

используемые |

языки |

описания |

аппаратуры — Verilog и VHDL; |

также существует |

несколько |

десятков |

|

альтернативных языков. |

|

|

|

|

Изначально как Verilog, так и VHDL использовались для документированияи моделирования схемныхрешений,реализованныхв иной форме (например, в виде схем). Моделирование при помощи HDL позволило инженерамработатьнаболеевысокомуровнеабстракции,чеммоделирование на уровне схемы, и, следовательно, упростить моделирование проектов, состоящих из тысяч транзисторов и более.

7

2. Назовите основные элементы языка AHDL, дайте их краткую характеристику.

Зарезервированныеключевые слова используются для следующих целей:

-для обозначения начала, конца и переходов в объявлениях языка AHDL;

-для обозначения предопределенных констант, т.е. GND и VCC.

Ключевые слова можно использовать как символические имена, только если они заключены в символы одинарных кавычек ('). Их можно также использовать в комментариях.

3. Перечислите способы описания логических элементов в AHDL.

Операторы булевых выражений AHDL

Оператор |

Пример |

Описание |

|

! |

!tob |

Дополнение |

(префиксное |

|

|

обращение) |

|

NOT |

NOT tob |

|

|

& |

bread & butter |

Логическое И |

|

AND |

bread AND butter |

|

|

!& |

a[3..1] !& b[5..3] |

Обращение логического И |

|

NAND |

a[3..1] NAND b[5..3] |

|

|

# |

trick # treat |

Логическое ИЛИ |

|

OR |

trick OR treat |

|

|

!# |

c[8..5] !# d[7..4] |

Обращение логического ИЛИ |

|

NOR |

c[8..5] NOR d[7..4] |

|

|

$ |

foo $ bar |

Исключающее ИЛИ |

|

XOR |

foo XOR bar |

|

|

!$ |

x2 !$ x4 |

Обращение исключающего |

|

XNOR |

x2 XNOR x4 |

логического ИЛИ |

|

8