Федеральное агентство связи

федеральное государственное бюджетное образовательное учреждение

высшего образования

«Сибирский государственный университет телекоммуникаций и

информатики»

(СибГУТИ)

Кафедра Передачи дискретных сообщений и метрологии (ПДСиМ)

10.05.02 Информационная безопасность телекоммуникационных систем, специализация Защита информации в системах связи и управления (очная форма обучения)

Сверточное кодирование

отчет по лабораторной работе № 6

дисциплины «Передача дискретных сообщений»

Выполнил:

студент ФАЭС,

гр. АБ-66 / А.В. Полянский/

«__»_________ 2018 г. (подпись)

Проверил:

доц. каф. ПДСиМ / И.Е. Шевнина/

«__»_________ 2018 г. (подпись)

Новосибирск 2018

Цель работы:

Изучение принципов сверточного кодирования.

Получение практического навыка работы с кодером и декодером сверточного кодирования.

Выполнение работы:

Сверточные коды относятся к классу помехоустойчивых кодов, то есть кодированию с прямым исправлением ошибок, являются непрерывными, цепными. Кодер для свёрточных кодов работает с информационной последовательностью без разбиения ее на независимые блоки. В каждый момент времени кодер из небольшого текущего блока информационных символов размером в b символов (блока-сообщения) образует блок, состоящий из v кодовых символов (кодовый блок), причем v>b. При этом кодовый v-символьный блок зависит не только от b-символьного блока-сообщения, присутствующего на входе кодера в настоящий момент, но и от предшествующих m блоков-сообщений. В этом и состоит наличие памяти в кодере.

Кодер сверточного кода

Основными элементами сверточного кодера являются: регистр сдвига, сумматоры по модулю 2 и коммутатор. Регистр сдвига является динамическим запоминающим устройством, в котором хранятся двоичные символы 0 или 1.

Число триггерных ячеек m в регистре сдвига и определяет память кода. В момент поступления на вход регистра нового информационного символа символ, хранящийся в крайнем правом разряде, выводится из регистра и сбрасывается.

Каждый из остальных, хранящихся в регистре символов перемещается на один разряд вправо, освобождая тем самым крайний левый разряд, куда и поступает новый информационный символ.

Сумматор по модулю 2 осуществляет сложение поступающих на его входы символов 0 и 1. Правило сложения по модулю 2 следующее: сумма двоичных символов равна 0, если число единиц среди поступающих на входы символов четно, и равна 1, если это число нечетно.

Коммутатор осуществляет последовательное считывание поступающих на его входы (контакты) символов и устанавливает на выходе очередность посылки кодовых символов в канал связи.

Параметры кодера:

— число информационных символов, поступающих за один такт на входе декодера, k=1;

— число символов на выходе декодера, соответствующих k поступившим на вход символам за такт, n=2;

— относительная скорость кода R=1/2.

Кодер состоит из регистра сдвига, содержащего 3 ячейки, двух сумматоров и коммутатора переключения. Нумерация ячеек слева направо. Внутреннее состояние кодера определяется первой и второй ячейками.

Начальное состояние кодера нулевое.

Рассматриваемый сверточный код является несистематическим. Порождающие многочлены, описывающие работу кодера, равны:

G1(X)=1+X2; G2(X)=1+X+X2

На каждом такте работы формируется выходная последовательность из двух бит, которые поступают в дискретный канал связи. При прохождении по каналу связи информация может подвергаться воздействию помех. Если ошибок нет, то полином ошибок равен нулю: Е(1,0)=00000000000…

При воздействии помех в полиноме ошибок появляются единицы: Е(1,0)=00001000100…, причем положение единиц указывает, в каком такте происходит ошибка.

Последовательность, образующаяся на выходе кодера, накладывается на полином ошибок, в результате чего на вход декодера поступает искаженная последовательность.

Рисунок 1 – Кодер сверточного кода

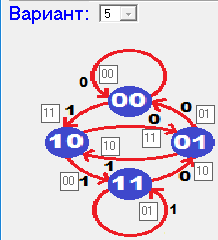

Диаграмма состояний:

Рисунок 2 – Диаграмма состояний

Сформируем кодовую последовательность:

![]()

Закодируем кодовую последовательность:

Рисунок 3 – Кодирование кодовой последовательности

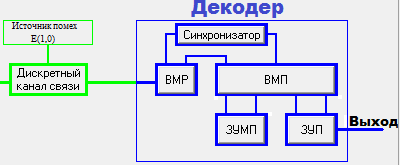

Декодер сверточного кода

Схема декодера состоит из вычислителя метрики ребер (ВМР), вычислителя метрики путей (ВМП), запоминающего устройства метрики путей (ЗУПМ) и запоминающего устройства путей (ЗУП). Для узловой синхронизации используется синхронизатор.

Вычислитель метрики ребер (ВМР). Для каждого такта работы, соответствующего приему кодовых символов, полученных за один цикл опроса коммутатора кодера, BMP вычисляет правдоподобие ребер, сливающихся в каждом узле. В случае двоичного симметричного канала с жесткими решениями он вычисляет Хеммингово расстояние между каждым из путей, сливающихся в любом узле, и соответствующей последовательностью принимаемых кодовых символов, поступивших с выхода первой решающей схемы приемника, выносящей жесткие решения о значении каждого принимаемого кодового символа. Вычислитель метрики путей (ВМП) для каждого из путей, выживших на предыдущем такте декодирования и хранимых в ЗУ путей, осуществляет следующие операции: вводит каждый из этих путей в аналог кодера, где генерируются 2q его возможных продолжений; вычисляет правдоподобие каждого из этих продолжений, для чего суммирует метрики выживших путей, хранимые в ЗУ метрики путей, с новыми вычисленными значениями метрик ребер; заносит вновь полученные пути в ЗУ путей, а их метрики - в ЗУ метрики путей, а затем отбирает из них пути, каждый из которых максимально правдоподобен для одного из узлов и сохраняет его в ЗУ путей, а его метрику - в ЗУ метрики путей. Затем эта же последовательность операций повторяется для следующего такта работы и т. д.

Запоминающее устройство метрики путей (ЗУМП) хранит метрики путей, выживших на предыдущих тактах. Данные перезаписываются на каждом такте по команде от ВМП.

Запоминающее устройство путей (ЗУП) хранит пути, выжившие на предыдущих актах. Какие пути считать выжившими, решает ВМР, который сообщает эту информацию в ЗУП.

Работа ВМР и ЗУМП представлена в виде таблиц, где отображаются вычисленные метрики ребер и метрики путей на каждом такте. В качестве метрики используется расстояние Хемминга. Состояние ячеек таблиц изменяется на каждом такте.

Вычислитель метрики путей управляет блоками ВМР, ЗУМП и ЗУП: на основании данных, полученных от ВМР и ЗУМП, он выносит решение о дальнейших действиях и выдает команды в эти блоки для последующей работы.

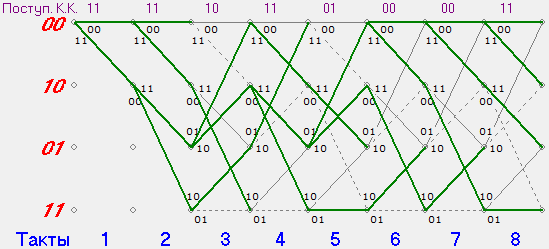

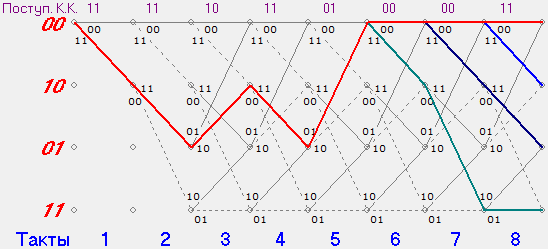

Работа ЗУП отображается на решетчатой диаграмме. Поскольку для демонстрационной работы выбраны случайные последовательности, состоящие из восьми символов, то на решетчатой диаграмме отображается восемь тактов: за каждый такт кодируется и декодируется один бит входной последовательности. Длина входной последовательности выбрана исходя из того, что за восемь тактов уже возможно исправление ошибки.

На диаграмме отображаются пути, имеющие минимальную метрику для каждого состояния на каждом из тактов.

Рисунок 4 – Декодер сверточного кода

Декодируем кодовую последовательность:

Рисунок 5 – Решетчатая диаграмма всех путей

Рисунок 6 – Решетчатая диаграмма только «выживших» путей

Последовательность на выходе декодера:

![]()

Вывод: в результате выполнения лабораторной работы были изучены принципы сверточного кодирования, сформирована диаграмма состояний кодера, закодирована кодовая последовательность, сформирована решетчатая диаграмма декодера и декодирована закодированная кодовая последовательность.