Labra5_Dtr_RgSch_Sinkhr_veri

.docxЛабораторная работа: Исследование синхронной логики на языке описания Verilog

Цель работы

Закрепить знания по применению языка Verilog для описания синхронной логики (D-триггеры, регистры, счетчики).

Задание на работу в лаборатории

Запустить САПР QuartusII.

На языке Verilog описать исследуемое цифровое устройство.

Произвести компиляцию проекта (исследуемого цифрового устройства).

Посмотреть синтезированную пакетом САПР QuartusII схему (RTL Viewer).

Осуществить функциональное моделирование (симуляцию) проекта.

Проверить правильность работы проекта и показать преподавателю.

Исследование D-триггера

Описание D-триггера на языке Verilog

module dff

(

input d, clk,

output regq

);

always @(posedgeclk)

q <=d ;

endmodule

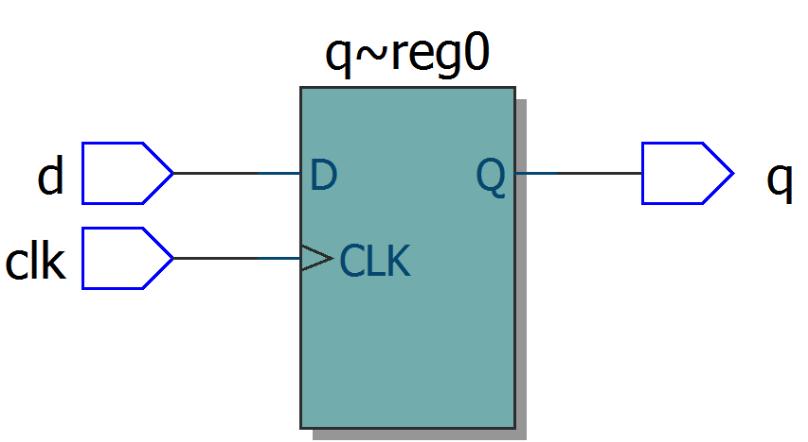

Схема D-триггера (RTL Viewer)

Сигнал управления синхронной логикой (D-триггером)

module dff_sync

(

input d, clk, sclr,

output regq

);

always @(posedgeclk) begin

if (sclr)

q <= 1’b0;

else

q <= d;

end

endmodule

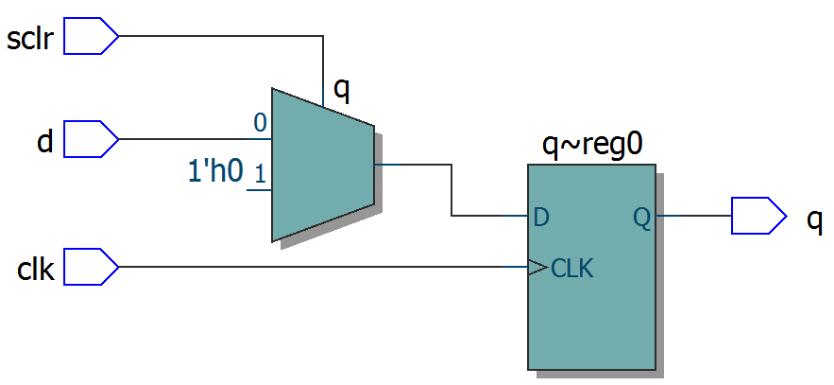

Схема D-триггера (RTL Viewer) с управлением синхронной логикой

Исследование регистра:

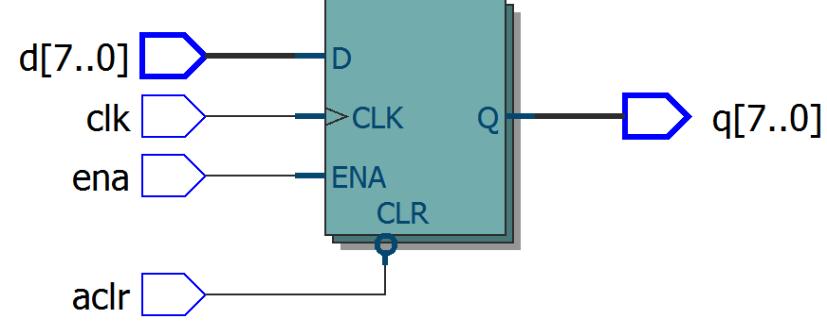

а) Регистр памяти (параллельный регистр)

Схема регистра памяти (RTL Viewer)

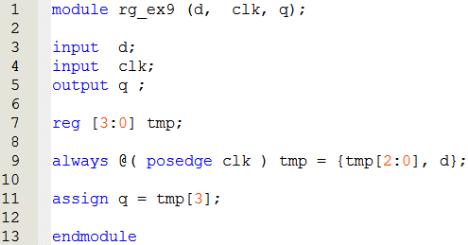

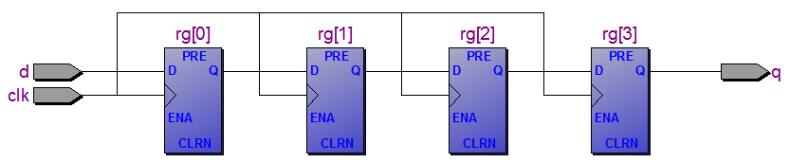

б) Регистр сдвига

Схема регистра сдвига (RTL Viewer)

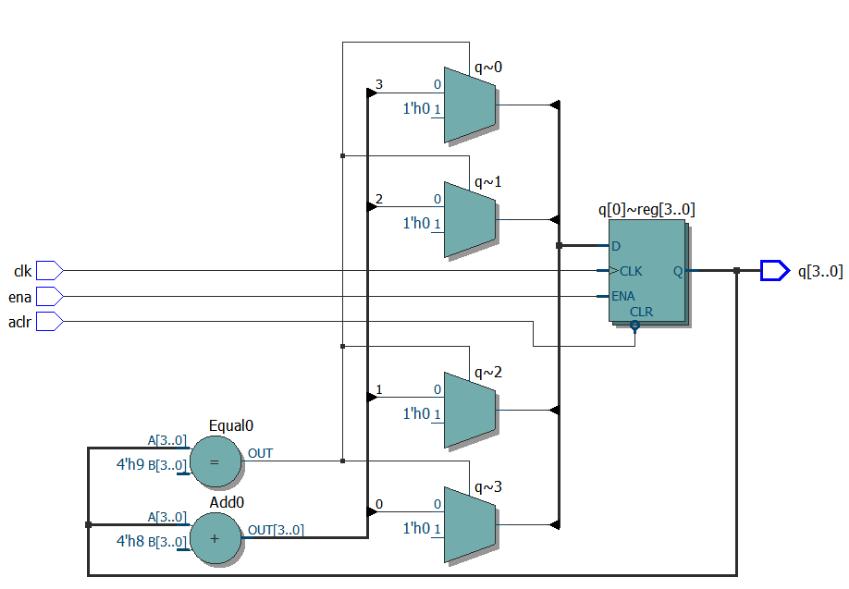

Двоично-десятичный счетчик (0÷9)

Схема двоично-десятичного счетчика (RTL Viewer)

Отчет

Отчет должен содержать:

1.Описание на языке Verilog исследуемой схемы.

2.Схему RTL Viewer, исследуемую пакетом САПР QuartusII.

3. Временные диаграммы входных и выходных сигналов, полученных в результате симуляции работы схемы исследуемого цифрового устройства.

4. Выводы по результатам исследований.