1 курс 1 семестр / лекции / Лекция 9 Многотактный П — копия

.pdf

4). Загрузка данных из памяти - чтение слова.

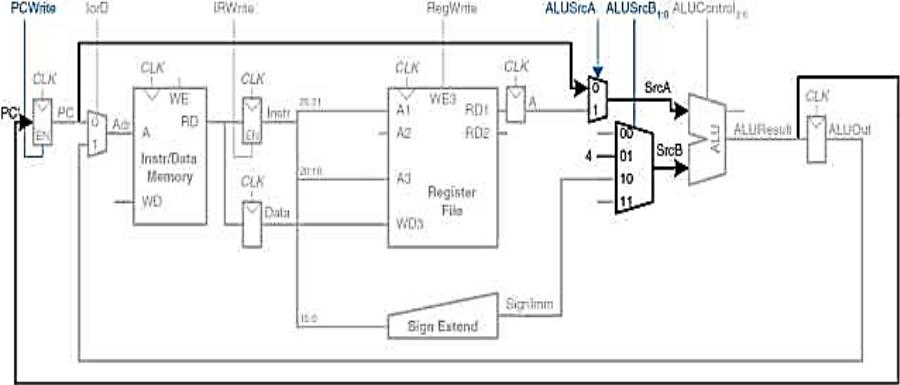

Для этого перед адресным входом памяти добавляем мультиплексор, чтобы в качестве адреса Adr можно было использовать либо PC, либо ALUOut. Этот мультиплексор управляется сигналом IorD (инструкция или данные), показывающим, должен ли быть подан адрес команды или адрес данных. Прочитанные из памяти данные сохраняются во временном регистре Data. Если подается адрес инструкции, то к порту RD подключен не архитектурный регистр памяти IRWrite, если адрес памяти, то подключен к этому же порту не архитектурный регистр Data, что определяется мультиплексором IorD.

Data

5).Запись данных в регистровый файл.

Адрес регистра результата определяется полем rt (Instr20:16) по порту А3 RF.

Прочитанные из временного регистра Data данные загружаются в файл регистров RF по управляющей команде RegWrite (запись регистра) порта WE3 =1 и данные загружаются в порт WD3 RF.

6). Увеличение счетчика команд на четыре для определения следующего слова памяти.

В многотактном процессоре можно использовать уже имеющееся АЛУ, которое уже использовалось ранее для определения адреса и в настоящее время оно пока еще не используется. Для этого добавляется пара мультиплексоров ALUSrcA и ALUSrcB, которые позволят подавать на входы АЛУ: содержимое РС (SrcA) и константу 4 (SrcB), необходимые для определения новой инструкции PC’ .

Тракт команды lw завершен: результат команды записан в RF и РС сменил адрес.

1.5.Алгоритм команды sw - сохранение слова.

1.Читает базовый адрес из первого порта регистрового файла А1- составляющая

SrcA.

2.Выполняет знаковое расширение непосредственного операнда – формирование составляющей адреса записи SrcB.

3.Сложение составляющих SrcA и SrcВ в АЛУ, получение адреса ALUOut=А для общей памяти I/D Memory где планируется сохранение слова.

Все эти функции уже выполнялись в тракте данных команды lw .

Отличие команды sw от команды lw это – запись слова не в RF, а в память I\D Memory, что обеспечивается:

4. Чтением еще одного адреса А2 в RF для определения сохраняемого слова В из порта RD2 файла регистров RF, которое будет записано в память I\D Memory 5. Запись содержимого слова В в память I\D Memory по сигналу разрешения

MemWrite.

Таким образом, слово В, которое было прочитано из порта RD2 файла регистров RF записывается по вычисленному адресу ALUOut=А в память I\D Memory по порту записи WD3.

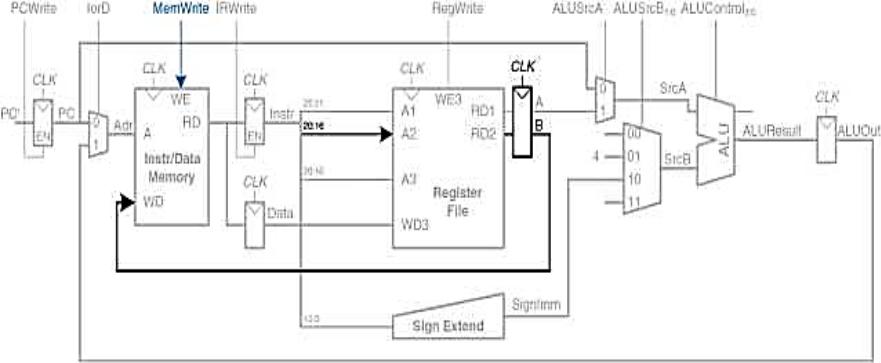

1.6. Тракт записи в память I/D Memory при выполнении команды sw.

1). Чтение адреса А2 из команды Instr поля (20:16) для определения слова В из порта RD2,файла регистров RF, которое нужно записать в памяти I/D Memory. 3). Запоминание этого слова В в не архитектурном регистре.

2). Запись слова В, найденного в регистре RF, из не архитектурного регистра в память I/D Memory, по вычисленному адресу А, определенному уже для порта WD памяти I/D Memory и только по сигналу Mem/Write (запись в память).

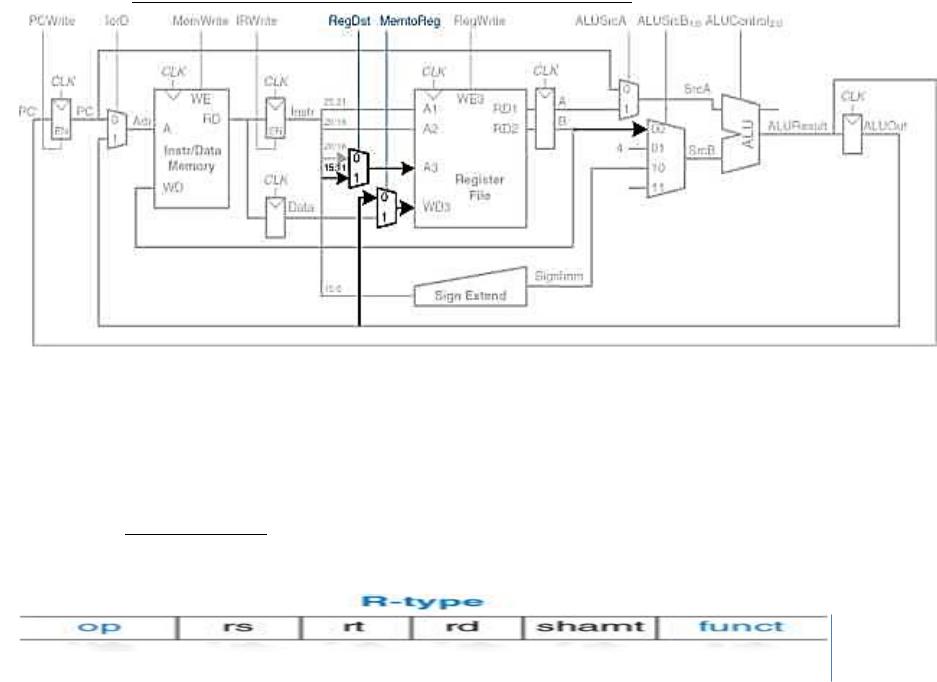

1.7. Тракт данных при поддержки команд типа R.

25:21

A1

20:16

A2

20:16

A3

WD3

15:0

ALUOut

Инструкции типа R используют адреса трех регистров для трех операндов (адреса А1,А2,А3): два регистра-источники (адреса А1= 25:21, А2= 20:16) и один регистр-результат (адрес А3= 15:11) для записи результата в порт WD3 RF.

Два операнда для выполнения функции выбраны из RD1 и RD2 RF. Их результат обработки двух данных SrcA и SrcB получен в AluOut, который теперь будет записан в

порт WD3 по ранее полученному адресу А3.

Формат инструкции типа R

31 6 bits |

26 |

|

25 5 bits 21 |

|

20 5 bits 16 |

|

15 5 bits 11 |

|

10 5 bits 6 |

|

5 |

6 bits |

0 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

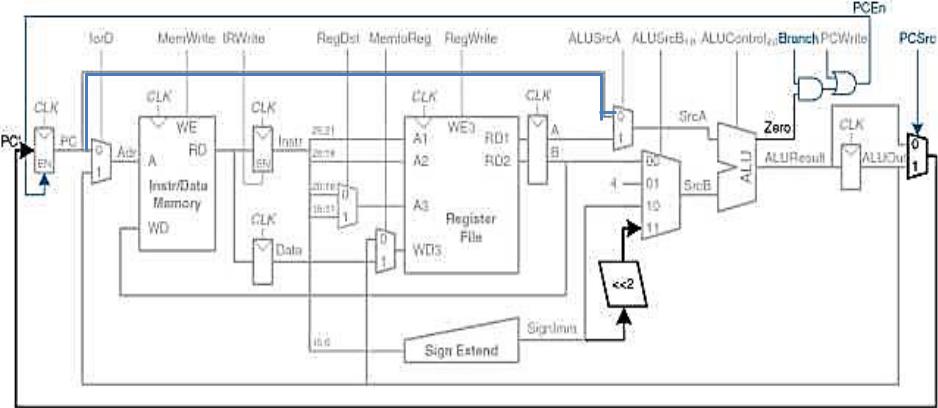

1.8. Тракт данных для поддержки команды beq.

Изменения в тракте данных для поддержки команды beq:

1.Для изменения адреса счетчика команд сдвиг адреса на определенное количество адресов происходит в блоке <<2. Новый результат счетчика команд РС’ , полученный из значений РC и блока <<2 как результат выхода ALUOut по команде PCsrc отправляется в счетчик команд на вход PC’.

2.Разрешение изменения счетчика происходит по командам: Branch и РСEn

Схема многотактного процессора MIPS.

2. Многотактное устройство управления.

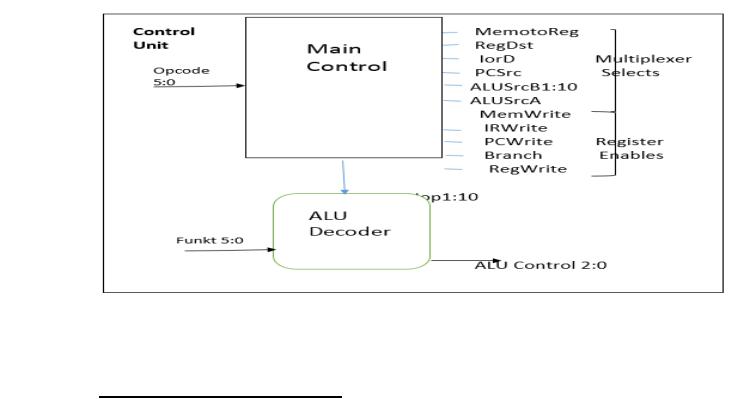

Блок Управления.

Aluop 1:0

Вместо основного дешифратора теперь понадобится конечный автомат, так как управляющие сигналы теперь будут зависеть не только от того, какая команда выполняется в данный момент, но и от того, на каком этапе выполнения она находится. Этот автомат называется Блоком Управления (Control Unit).

Сигналы для мультиплексоров обозначены следующим образом:

MemtoReg (запись в регистровый файл), RegDst (формирования адреса А3 в RF), IorD (инструкция или данные), PCSrc (изменение величины счетчика команд при переходе) , ALUSrcB и ALUSrcA (составляющие АЛУ для выполнения операций).

Обозначение сигналов разрешения записи: IRWrite ( запись инструкций в регистр),

MemWrite (запись в память), PCWrite (запись адреса счетчика команд), Branch (разрешение перехода) и RegWrite (Запсиь в регистровый файл)

Диаграмма Блока управления.

Fetch -этап выборки команды – начальное состояние S0 блока. Сюда же приходит команда Reset – возврат блока.

Для простоты чтения диаграммы состояний далее укажем сигналы, которые имеют смысл на конкретном этапе выпо Сигналы управления мультиплексорами будем указывать л действительно используются. Сигналы разрешения записи только если они не равны нулю.