690_Glukhov_A.V._OrCAD_9.2_Proektirovanie_ehlektronnykh_

.pdf

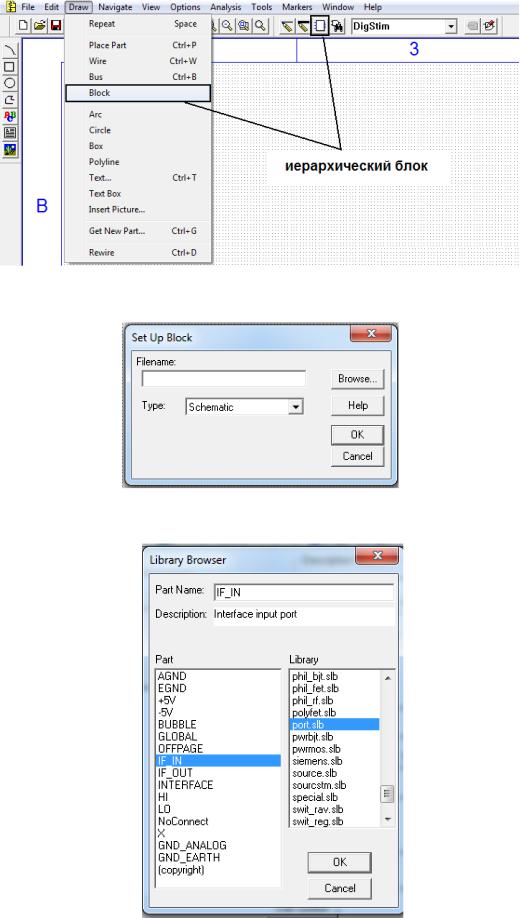

Рисунок 4.1. – Ввод блока в редакторе PSpice Schematics

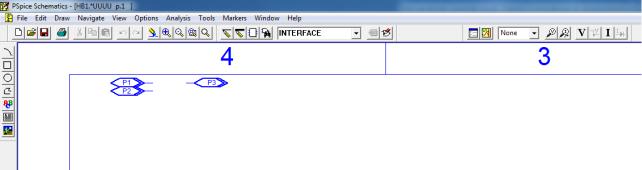

Рисунок 4.2. – Диалоговое окнов параметров блока

Рисунок 4.3. – Вход в библиотеку port.sib

- 61 -

В левой части окна просмотрите список элементов, найдите символы IF_IN (для левых или входных выводов); IF_OUT (для правых или выходных выводов) и INTERFACE (для остальных выводов).

Двойным щелчком или нажатием на кнопку OK выберете последовательно эти три элементы. При размещении их на чертеже подведите конец линии к стороне блока до появления креста в месте соприкосновения с блоком и щелк-

ните левой мышью по элементу  . При этом на контуре блока появится точка и условное обозначение вывода Pi, где i – номер вывода (рис. 4.4).

. При этом на контуре блока появится точка и условное обозначение вывода Pi, где i – номер вывода (рис. 4.4).

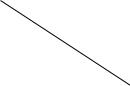

Рисунок 4.4. – Подсоединение вывода к блоку

Для формирования схемы замещения блока выделите его контур левой клавишей мыши и по команде Navigate>Push (рис. 4.5) войдите в окно редакто-

ра Schematics.

Рисунок 4.5. – Вход в редактор Schematics для создания схемы замещения блока

- 62 -

Если проект не сохранен, то развернется панель Save As, где необходимо присвоить имя файлу и нажать кнопку “Сохранить”. После открытия окна Set Up Blok (рис. 4.2) присвойте имя создаваемому блоку в поле Filename и нажмите кнопку OK. На открывшейся панели в области проектирования Schematics (рис. 4.6) создается схема замещения иерархического блока в соответствие с заданием (см. далее). Для обратного перехода на верхний уровень иерархии воспользуйтесь командой Navigate > Pop.

Рисунок 4.6. – Область проектирования иерархического блока в Schematics

Каждому блоку может соответствовать несколько вариантов схем замещения, что позволяет выполнить моделирование различных вариантов. Для этого вручную составляется несколько схем замещения, сохраняемых в отдельных файлах и имеющих одинаковое количество интерфейсных выводов. Если схема, указанная на строке Filename уже создана, то на экран сразу выводится изображение этой схемы.

4.2.2. Схемная реализация логических элементов. Логические элемен-

ты создаваемые с помощью диодов получили название диодной логики (ДЛ), посредством транзисторов – транзисторной логикой (ТЛ), а комбинированные элементы, соответственно, диодно – транзисторной логикой (ДТЛ).

Если хотя – бы к одному из входов схемы «И» (рис. 4.7, а) будет подан сигнал равный нулю, то через диод будет протекать ток. Падение напряжения на диоде стремится к нулю, соответственно на выходе тоже будет ноль. На выходе появится сигнал только при условии, что все диоды будут закрыты, то есть на все входы будет подан сигнал. Схема логического элемента «ИЛИ» представлена на рис. 4.7, б. На каждый из входов может подаваться сигнал в виде какого-то напряжения (единица) или его отсутствия (ноль). На резисторе R появиться напряжение даже при его появлении на каком – либо из диодов. Если используются не все входы, то те входы, которые не используются, следует соединять с землей, чтобы избежать появления посторонних сигналов. В логическом элементе «НЕ» используют транзистор (рис. 4.7, в). При наличии положительного напряжения на входе X1 транзистор VT открывается и напряжение его коллектора стремится к нулю. Если X1=0, то положительного сигнала на базе

- 63 -

нет, транзистор закрыт, ток не проходит через коллектор и на резисторе R нет падения напряжения, соответственно на коллекторе появится сигнал UP.

а) |

б) |

в) |

Рисунок 4.7. – Диодная логика: И (а), ИЛИ (б) и НЕ (в)

4.3. Порядок выполнения работы. Выпишите в соответствии со своим вариантом задания (номером бригады) данные для реализации микросхемы логических элементов из табл. 4.1.

Таблица 4.1. – Варианты задания

Пара- |

Микросхема |

Логичес- |

Модель |

Модель |

метры |

отечественная |

кие |

диода |

n-p-n транзи- |

Номер |

(зарубежный |

элементы |

|

стора |

бригады |

аналог) |

|

|

|

1 |

К155ЛА4 (7400) |

три логиче- |

BAX12 |

DH3724CD |

|

|

ских эле- |

|

|

|

|

мента |

|

|

|

|

3И-НЕ |

|

|

2 |

К155ЛЕ1 (7402) |

2ИЛИ-НЕ |

BAX14 |

DH3724CN |

3 |

К155ЛЛ1 (7432) |

четыре ло- |

BAX18 |

DH3725CD |

|

|

гических |

|

|

|

|

элемента |

|

|

|

|

2ИЛИ |

|

|

|

|

- 64 - |

|

|

Окончание таблицы 4.1.

Пара- |

Микросхема |

Логичес- |

Модель |

Модель |

метры |

отечественная |

кие |

диода |

n-p-n транзи- |

Номер |

(зарубежный |

элементы |

|

стора |

бригады |

аналог) |

|

|

|

4 |

К155ЛИ1 (7408) |

четыре ло- |

BAY68 |

DH3725CN |

|

|

гических |

|

|

|

|

элемента |

|

|

|

|

2И |

|

|

5 |

К155ЛЕ5 (7428) |

четыре ло- |

BAY69 |

DH3724CD |

|

|

гических |

|

|

|

|

элемента |

|

|

|

|

2ИЛИ-НЕ |

|

|

6 |

К155ЛН1 (7404) |

шесть логи- |

BAY80 |

DH3724CN |

|

|

ческих эле- |

|

|

|

|

мента НЕ |

|

|

7 |

К155ЛА1 (7420) |

два логиче- |

BAY135 |

DH3725CD |

|

|

ских эле- |

|

|

|

|

мента |

|

|

|

|

4И-НЕ |

|

|

8 |

К155ЛЕ4(7427) |

три элемен- |

BGX50A |

DH3725CN |

|

|

та 3ИЛИ- |

|

|

|

|

НЕ |

|

|

9 |

К155ЛА2 (7430) |

логический |

BAX12 |

DH3724CD |

|

|

элемент |

|

|

|

|

8И-НЕ |

|

|

10 |

К155ЛА3 (7400) |

четыре ло- |

BAX14 |

DH3724CN |

|

|

гических |

|

|

|

|

элемента |

|

|

|

|

2И-НЕ |

|

|

В соответствие с заданием табл. 4.1 создайте на листе бумаги блок логического устройства, определитесь с количеством входных и выходных выводов. Для создания своего проекта выберете курсором команду File (см. рис. 2.1), за-

тем в ниспадающем меню строку New (или щелкнуть по пиктограмме  ) сохраните файл по команде File > Save As, присвоив имя проекту. Для формирования иерархического блока выполните команды Draw>Block (см. рис. 4.1) или

) сохраните файл по команде File > Save As, присвоив имя проекту. Для формирования иерархического блока выполните команды Draw>Block (см. рис. 4.1) или

нажатием на кнопку  панели рисования редактора PSpice Schematics рис. 2.1. Войдите в диалоговое окно параметров блока (рис. 4.2), дважды щелкнув на размещенный элемент и задайте имя файла на строке Filename, а на панели Туре выберите тип описания блока: Schematic и нажмите кнопку OK. Разместите в области дополнительного проекта (см. рис. 2.1) необходимое количество входных (включая вывод земли и питания) и выходных портов. Для этого

панели рисования редактора PSpice Schematics рис. 2.1. Войдите в диалоговое окно параметров блока (рис. 4.2), дважды щелкнув на размещенный элемент и задайте имя файла на строке Filename, а на панели Туре выберите тип описания блока: Schematic и нажмите кнопку OK. Разместите в области дополнительного проекта (см. рис. 2.1) необходимое количество входных (включая вывод земли и питания) и выходных портов. Для этого

- 65 -

необходимо активизировать менеджер компонентов на панели рисования нажа-

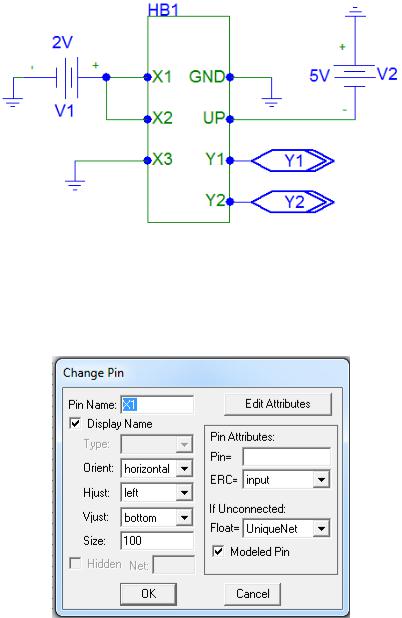

тием пиктограммы  (см. рис. 2.1). После появления диалогового окна Part Browser Basic при нажатии на кнопку Libraries… в открытом окне Library Browser активизируйте библиотеку port.slb (рис. 4.3). В левой части окна из списка элементов поочередно выберите входные IF_IN, затем выходные IF_OUT выводы двойным щелчком или нажатием на кнопку OK. Согласно задания, нарисуйте схему замещения блока (рис. 4.8). Из библиотеке port.slb (рис. 4.3) выберите элемент EGND (земля), разместите пассивный элемент схемы резистор (R) из библиотеки analog.slb. Для размещения активных элементов схемы войдите в окно Library Browser , активизируйте библиотеки в соответствии с элементами: диоды (ediode.slb), биполярные транзисторы (bipolar.slb) и выберите нужные вам типы элементов. Соедините элементы схемы по команде Draw

(см. рис. 2.1). После появления диалогового окна Part Browser Basic при нажатии на кнопку Libraries… в открытом окне Library Browser активизируйте библиотеку port.slb (рис. 4.3). В левой части окна из списка элементов поочередно выберите входные IF_IN, затем выходные IF_OUT выводы двойным щелчком или нажатием на кнопку OK. Согласно задания, нарисуйте схему замещения блока (рис. 4.8). Из библиотеке port.slb (рис. 4.3) выберите элемент EGND (земля), разместите пассивный элемент схемы резистор (R) из библиотеки analog.slb. Для размещения активных элементов схемы войдите в окно Library Browser , активизируйте библиотеки в соответствии с элементами: диоды (ediode.slb), биполярные транзисторы (bipolar.slb) и выберите нужные вам типы элементов. Соедините элементы схемы по команде Draw

> Wire (или выбором пиктограммы  ). Присвойте поочередно имена портам интерфейса как показано на схеме рис. 4.8 в окне Set Attribute Value (см. рис.

). Присвойте поочередно имена портам интерфейса как показано на схеме рис. 4.8 в окне Set Attribute Value (см. рис.

3.21), щелкнув левой мышью по каждому элементу  .

.

Рисунок 4.8. – Пример диодной схемы логики

После завершения создания дополнительного проекта сохраните файл по команде File > Save. Для выхода в основной проект закройте окно формирова-

- 66 -

ния схемы иерархического блока, нажав на кнопку  в правом верхнем углу экрана нижней панели.

в правом верхнем углу экрана нижней панели.

Подключите внешние элементы к иерархическому блоку как показано на рис. 4.9. Для питания микросхемы подсоедините источник постоянного напряжения VDC из библиотеки source.slb и землю EGND из библиотеки port.slb.

Для проверки функционирования схемы в качестве “1” можно использовать источник постоянного напряжения VDC с меньшим уровнем напряжения и в качестве “0” землю. Из библиотеке port.slb выберите выходные IF_OUT выводы. При размещении их на чертеже подведите конец линии к стороне блока до появления креста. Приведите в соответствие имена всех портов, поочередно нажав на условное обозначение выводов Pi (рис. 4.4).

Рисунок 4.9. – Подключение внешних элементов к иерархическому блоку

В открывшемся окне Change Pin (рис. 4.10) в строке Pin Name введите имена.

Рисунок 4.10. – Окно изменения имени вывода Change Pin

- 67 -

Проверьте наличие в схеме ошибок по команде Analysis > Electrical Rule Check (рис. 2.10). В случае наличия ошибок, устраните их. Задайте параметры

моделирования нажатием на пиктограмму  (Analysis->Setup) и в открывшемся окне (рис. 2.13) отметьте директиву моделирования Transient. Нажатием кнопки откройте диалоговые меню задания параметров директивы “Расчет переходных процессов” (рис. 2.14), выберите Print Step = 0ns и Final Time = 100ns и нажмите кнопку Close.

(Analysis->Setup) и в открывшемся окне (рис. 2.13) отметьте директиву моделирования Transient. Нажатием кнопки откройте диалоговые меню задания параметров директивы “Расчет переходных процессов” (рис. 2.14), выберите Print Step = 0ns и Final Time = 100ns и нажмите кнопку Close.

Для графического отображения результатов моделирования в главном меню Analysis выберите команду Probe Setup, откроется окно Probe Setup Options (рис. 2.15) с тремя вкладками: Probe Startup (рис. 2.15, а), Data Collection

(рис. 2.15, б) и Checkpoint (рис. 2.15, в). На вкладке Probe Startup выберите опцию Automatically run Probe after simulation (Автоматически запускать программу вывода результата в виде диаграммы Probe после завершения моделирования) и опцию None (Не выполнять специальные предварительные установки после запуска моделирования, рис. 2.15, а), на вкладке Data Collection (рис. 2.15, б) из выпадающего окна для всех параметров выберите опцию All. Опции на вкладке Checkpoint (рис. 2.15, в) оставьте без изменения. Нажми-

те OK.

Запустите процесс моделирования при помощи пиктограммы  Simulate на панели моделирования (рис. 2.1), либо по команде Analysis > Simulate (F11) и дождитесь его окончания до момента открытия окна Probe (рис. 2.16) и появ-

Simulate на панели моделирования (рис. 2.1), либо по команде Analysis > Simulate (F11) и дождитесь его окончания до момента открытия окна Probe (рис. 2.16) и появ-

ления ярлыка  .

.

Для вывода диаграмм выберите в главном меню Trace команду Add Trace

(рис. 2.17) или щелкните по кнопке  и слева в открывшемся окне Add Trace (рис. 2.18) последовательно выберите из списка диаграмм (щелчком мыши): V(HB1:X1); V(HB1:X2); V(HB1:X3); V(HB1:Y1); V(HB1:Y2).

и слева в открывшемся окне Add Trace (рис. 2.18) последовательно выберите из списка диаграмм (щелчком мыши): V(HB1:X1); V(HB1:X2); V(HB1:X3); V(HB1:Y1); V(HB1:Y2).

Проверьте правильность сигналов на выходе по таблице истинности.

4.4. Результаты работы

Отчет должен содержать принципиальную схему логического блока и временные зависимости, полученные в процессе моделирования.

4.5.Контрольные вопросы

1.Нарисуйте логическую схему И на диодах.

2.Нарисуйте логическую схему ИЛИ на диодах.

3.Нарисуйте логическую схему НЕ на биполярном транзисторе.

4.Что понимается под иерархическим блоком?

5.Какие активные элементы используются для создания логических схем?

6.Какие команды используются для создания иерархического блока?

-68 -

5. Лабораторная работа № 4 Синтез комбинационных цифровых устройств

спомощью программы OrCAD Schematics

5.1.Цель работы. Получение практических навыков составления комбинационных цифровых устройств с использованием шин в качестве средств связи между логическими элементами.

5.2.Основные понятия и определения

Комбинационные цифровые устройства включают следующие основные логические операции:

логическое умножение (конъюнкция или операция И). Записывается как F= a /\ b или F = a·b, или F = ab, читается как a и b. Операция обозначает, что сложное высказывание истинно лишь тогда, когда истинны все простые высказывания.

логическое сложение (дизъюнкция или операция ИЛИ). Записывается как F = a \/ b или F = a+b, читается как F = a или b. Обозначает, что сложное высказывание истинно, если истинно хотя бы одно из простых высказываний, и тем более, если истинны оба.

логическое отрицание (инверсия или операция НЕ). Записывается F a , читается – F = “не” a. Операция обозначает, что сложное высказывание

истинно, если простое ложно и наоборот.

Словесное описание приведенных логических операций может быть представлено в виде таблицы (табл. 5.1).

Таблица 5.1. – Табличное описание логических операций

Аргументы |

|

|

|

|

|

|

|

|

|

|

(простые вы- |

Логические операции (булевы функции) |

|

|

|

||||||

сказывания) |

|

|

|

|

|

|

|

|

|

|

a |

b |

И |

ИЛИ |

|

|

НЕ |

|

|

|

|

a b |

a b |

|

|

|

|

|

|

|

||

a |

|

b |

||||||||

|

|

|

||||||||

|

|

|

|

|

|

|

||||

0 |

0 |

0 |

0 |

1 |

|

1 |

||||

0 |

1 |

0 |

1 |

1 |

|

0 |

||||

1 |

0 |

0 |

1 |

0 |

|

1 |

||||

1 |

1 |

1 |

1 |

0 |

|

0 |

||||

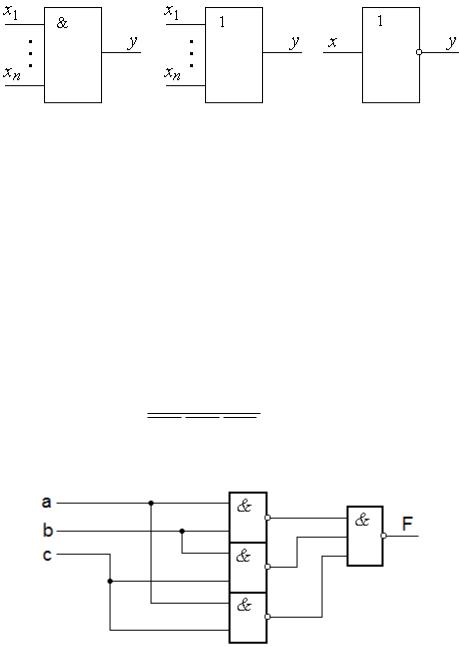

Выполнение сложной логической операции может быть сведено к трем вышеперечисленным операциям и имея технические устройства, реализующие операции И, ИЛИ, НЕ, можно построить комбинационное цифровое устройство. Логические элементы И, ИЛИ, НЕ (рис. 5.1) образуют основной базис.

- 69 -

а) |

б) |

в) |

Рисунок 5.1. – Условное обозначение логических элементов на электрических схемах: И (а), ИЛИ (б), НЕ (в)

Синтез комбинационного цифрового устройства предусматривает построение структурной схемы устройства, т. е. определение состава необходимых логических элементов и соединений между ними, при которых обеспечивается преобразование входных цифровых сигналов в выходные в соответствии с заданными условиями работы устройства. В процессе синтеза обычно подразумевается необходимость минимизации затрат на реализацию устройства. Реализация устройства на интегральных схемах предусматривает широкое использование элементов И – НЕ, ИЛИ – НЕ, И – ИЛИ – НЕ с учётом заданной элементной базы.

Например, функция F=(ab) (bc) (ac) включает только операции И-НЕ, и ее реализация в базисе И-НЕ имеет вид представленный на рис. 5.2.

Рисунок 5.2. –Реализация функции F в базисе И-НЕ

Дискретные устройства, выполняющие операцию сложения над числами, представленными в двоичной системе счисления, называются двоичными сумматорами. Сумматор, который выполняет операцию сложения в одном разряде, называют одноразрядным. Одно из простейших логических устройств, выполняющих сложение одноразрядных чисел без переноса в старший разряд, называется сумматором по модулю 2 (M2) или логическим элементом «исключающее ИЛИ» (логическая неравнозначность). На его выходе 1 появляется, когда в наборе входных сигналов содержится нечетное число 1. Графическое обозначение двухвходового сумматора по модулю 2 показано на рис. 5.3.

- 70 -