контрольная работа вар 17

.docxЗадача 1.

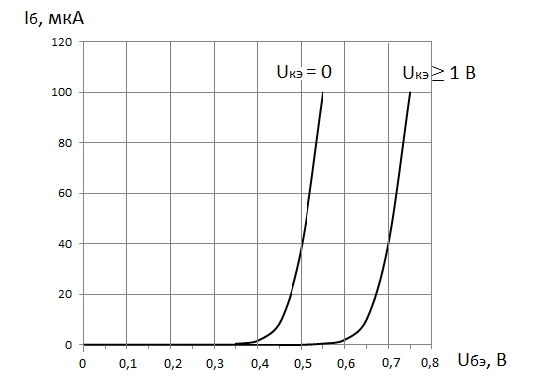

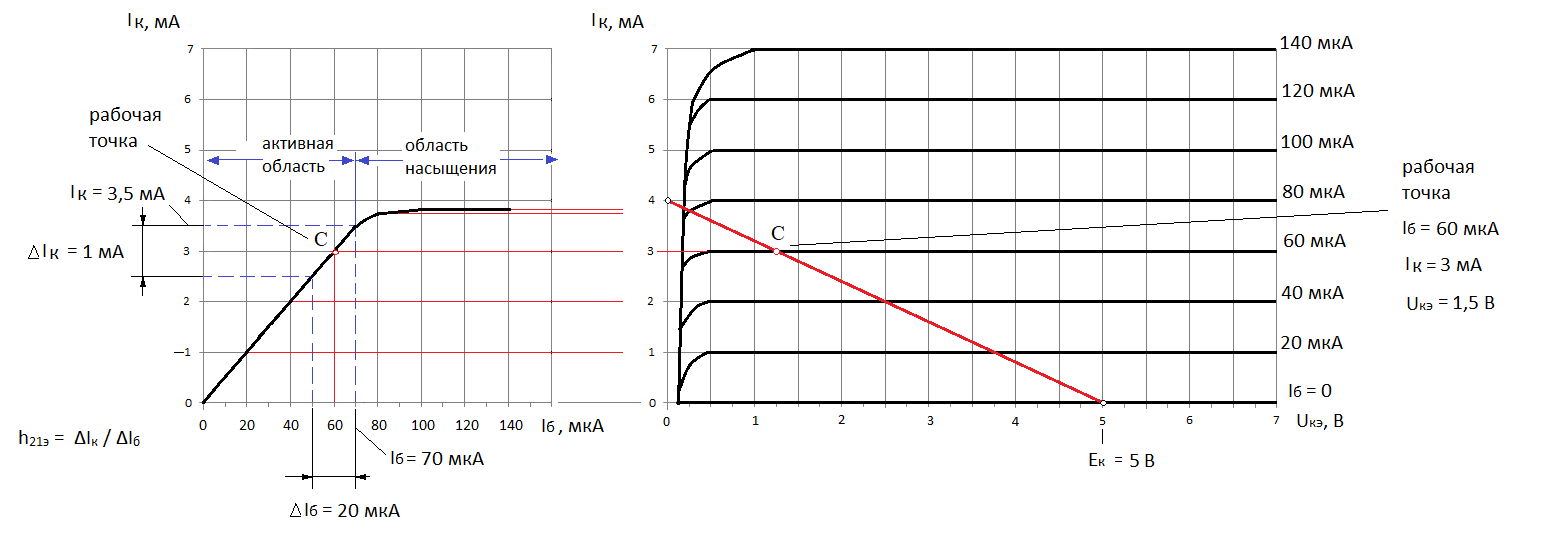

Рисунок 1. Входные и выходные ВАХ транзистора кремниевого маломощного транзистора, включенного с ОЭ

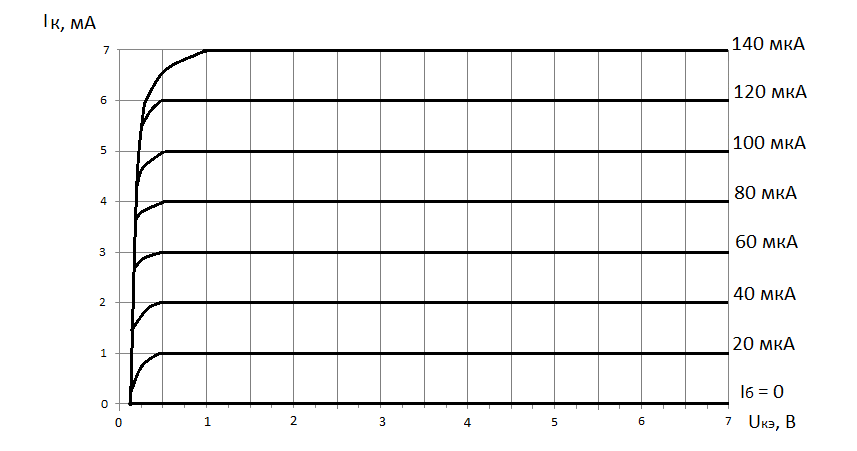

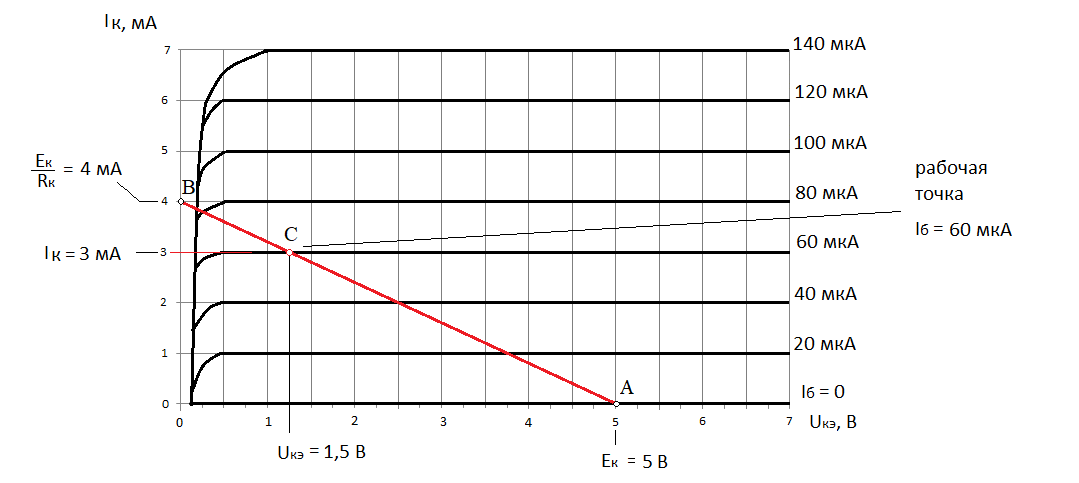

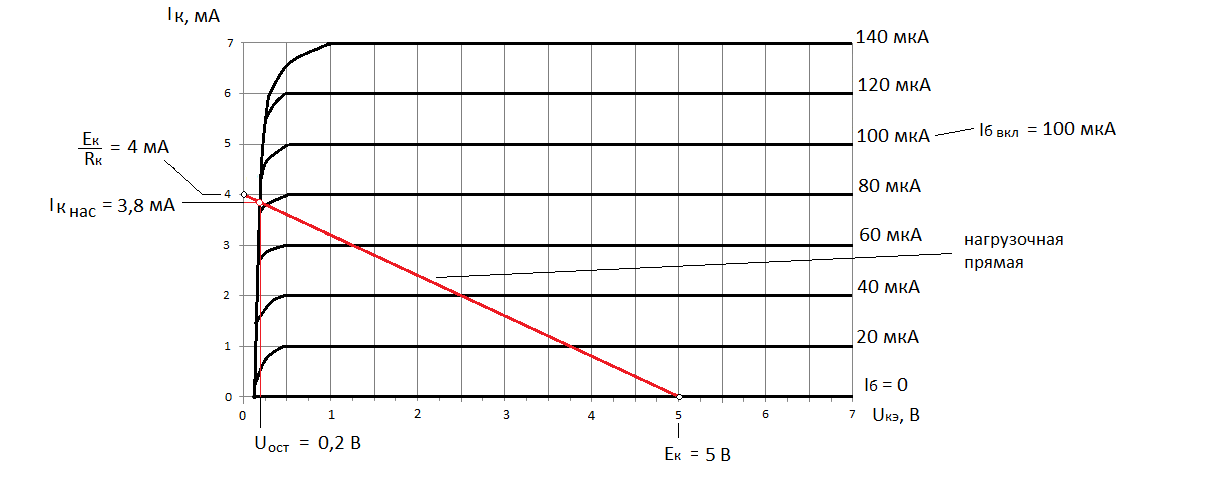

Рисунок 2. Выходные ВАХ кремниевого маломощного транзистора, влюченного с ОЭ

Исходные данные (вариант 17):

Ток базы покоя: Iб = 60 мкА

Напряжение питания: Eк = 5 В

Сопротивление коллекторной нагрузки: Rк = 1,25 кОм

Перерисуем входные (рис.1) и выходные (рис.2) ВАХ транзистора. Для выходных ВАХ отметим значения токов базы.

Режим усиления:

а)

На

входной характеристике транзистора

для Uкэ

≥ 1 В (рис. 3) находим рабочую точку,

соответствующую току базы транзистора

и определяем напряжение

база-эмиттер транзистора

для этой рабочей точки:

и определяем напряжение

база-эмиттер транзистора

для этой рабочей точки:

.

.

Рисунок 3. Входная ВАХ транзистора

На семействе выходных характеристик рис.4 строим нагрузочную прямую

,

,

которую проведём через две точки с координатами:

т.A

( ,

,

)

)

т.B

( ,

,

.

.

Рисунок 4. Выходные ВАХ транзистора

Рабочую точку (рис.4) находим графически как точку пересечения нагрузочной прямой и линии выходной ВАХ тока базы рабочей точки .

Определяем графически параметры рабочей точки (рис.4):

ток

коллектора:

и

напряжение коллектор-эмиттер:

Мощность, рассеиваемая на коллекторе транзистора, равна

Мощность, рассеиваемая на резисторе коллекторной цепи транзистора, равна

б) Построим передаточную характеристику Iк = Iк (Iб), соответствующую нагрузочной прямой, для чего графически определим координаты тока коллектора точек пересечения с нагрузочной прямой всех имеющихся линий выходных ВАХ транзистора (рис.5). Расчетные данные сводим в таблицу 1, и строим по ним передаточную характеристику Iк = Iк (Iб). Передаточную характеристику удобно строить слева от семейства выходных ВАХ транзистора (во 2-м квадранте), совмещая оси ординат – оси тока коллектора (рис.5).

Таблица 1. Расчетные данные для построения передаточной характеристики Iк = Iк (Iб)

Iб, мкА |

0 |

20 |

40 |

60 |

80 |

100 |

120 |

140 |

Iк,мА |

≈ 0 |

1 |

2 |

3 |

3,76 |

3,8 |

3,81 |

3,81 |

Рисунок 5. Передаточная характеристика Iк = Iк (Iб)

По наклону передаточной характеристики в окрестности рабочей точки тока базы определяем коэффициент передачи тока базы (рис.5):

Также определяем границу тока базы и тока коллектора, при которых транзистор выходит в область насыщения:

и

и

Отмечаем на графике передаточной характеристики активную область (область малых нелинейных искажений) и область насыщения (рис.5).

в)

Максимальная амплитуда переменной

составляющей выходного напряжения

ограничена областью отсечки (значение

тока базы

)

и областью насыщения (значение тока

базы

).

Тогда, максимальная амплитуда переменной

составляющей выходного напряжения

определяется амплитудой тока базы:

)

и областью насыщения (значение тока

базы

).

Тогда, максимальная амплитуда переменной

составляющей выходного напряжения

определяется амплитудой тока базы:

и изменению тока коллектора между своим максимальным значением:

и своим минимальным значением:

Этим значениям соответствуют граничные значения входного тока базы:

и граничные значения напряжения коллектор-эмиттер:

На выходных ВАХ транзистора (рис.6) строим временные диаграммы выходного напряжения и выходного тока коллектора и определяем амплитуду переменного сигнала выходного напряжения:

и амплитуду переменного сигнала выходного тока коллектора:

Рисунок 6. Временные диаграммы выходного напряжения и тока коллектора

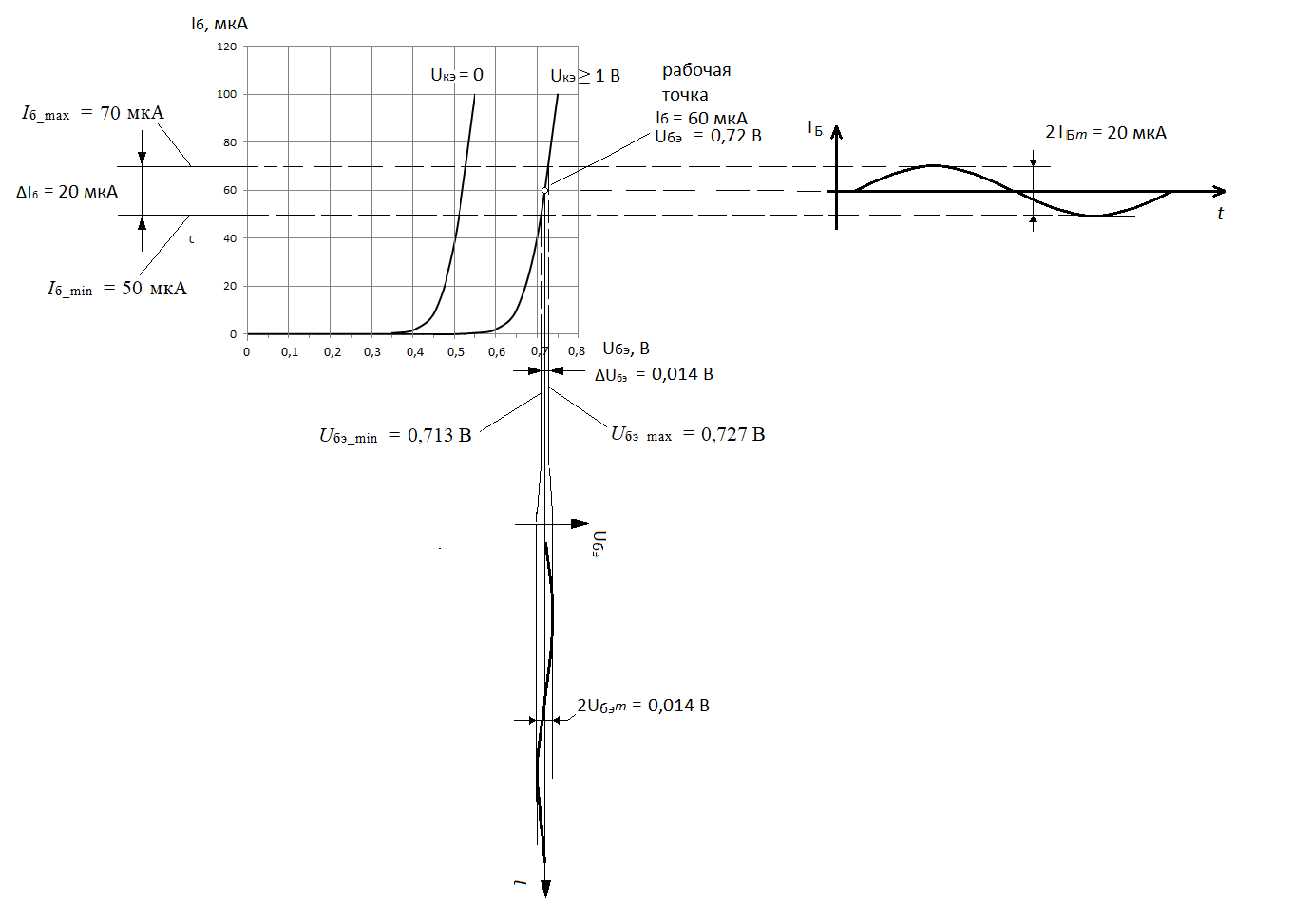

На

входной характеристике для

Uкэ

≥ 1 В (рис.7) строим временные диаграммы

входного тока базы

между его граничными значениями

между его граничными значениями

и

и

и

определяем соответствующие границы

входного напряжения база-эмиттер

и

определяем соответствующие границы

входного напряжения база-эмиттер

.

.

Амплитуда переменного сигнала входного тока базы:

а амплитуда переменного сигнала входного напряжения база-эмиттер:

Рисунок 7. Временные диаграммы входного сигнала и определение входного сопротивления

На входной характеристике для Uкэ ≥ 1 В (рис.7) определяем изменение входного напряжения база-эмиттер для изменения тока базы:

около

рабочей точки тока базы

:

:

.

.

Входное сопротивление каскада усилителя:

Выходное сопротивление каскада усилителя:

Коэффициент усиления по напряжению:

Коэффициент усиления по току:

Коэффициент усиления по мощности:

Полезная мощность в нагрузке (определяется по максимальной амплитуде выходного сигнала в режиме отсутствия ограничения)

Ключевой режим:

г) На выходных ВАХ транзистора (рис.8) определяем остаточное напряжение на открытом транзисторе:

и выходной ток насыщения:

Сопротивление транзистора в состоянии “включено”:

Мощность, рассеиваемая на коллекторе транзистора в состоянии “включено”,

Рисунок 8. Ключевой режим работы транзистора

Минимальный ток базы, необходимый для включения транзистора, -- это ток базы нижней ветви, где транзистор находится в режиме насыщения:

Рисунок 9. Определение входного напряжения включения

На входной ВАХ транзистора в режиме насыщения (ветвьUкэ = 0 В) (рис.9) определяем входное напряжение включения для входного тока базы :

Мощность, необходимая для включения транзистора:

Задача 2.

Исходные данные (вариант 17):

Напряжение входных сигналов: U1 = 5 B, U2 = 10 B

Фазы входных сигналов: U1 = +, U2 = --

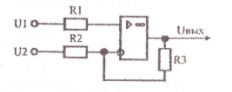

Рисунок 10. Схема включения идеального операционного усилителя

В схеме сигналы подается U2 на инвертирующий сигнал, а U1 на неинвертирующий. Это означает, что фаза выходного сигнала от воздействия будет совпадать с фазой U1, а фаза выходного сигнала U2 от воздействия будет противоположным.

Сигнал U1 усиливается без инверсии, сигнал U2 усиливается с инверсией, поэтому на выходе сигналы от первого и от второго входа совпадают по фазе. Выходной сигнал – сумма выходных сигналов от первого и от второго входов.

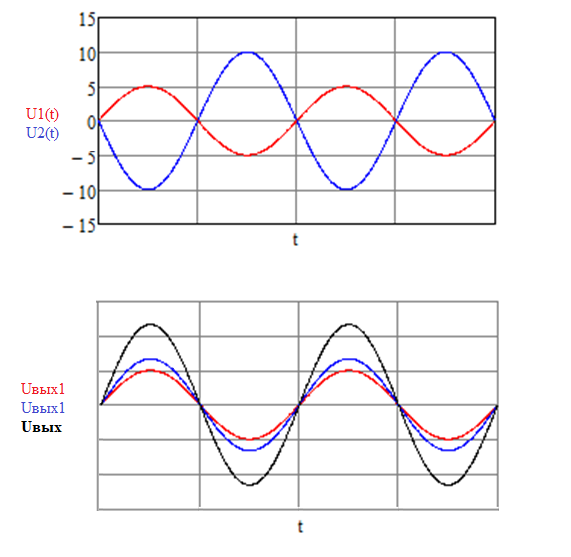

Рисунок 11. Временные диаграммы входных и выходных сигналов

На рис.11 изображены временные диаграммы входных и выходных сигналов. В условном масштабе при равном коэффициенте усиления по каждому из входов соотношение амплитуд выходных сигналов сохраняется.

Результирующий сигнал представляет сумму выходных сигналов от воздействия каждого с учетом фазовых соотношений. В данном случае фаза результирующего сигнала совпадает с фазами откликов на оба входных сигнала.

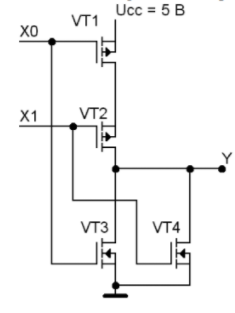

Задача 3.

Исходные данные (вариант 17):

Логическая функция: ИЛИ-НЕ на кМПД ключах

Входной сигнал: Х1 = 1, Х2 = 1

Логическая схема представлена на рис. 12:

Рисунок 12. Схема кМПД ключа

Если на входы Х0 и Х1 подать сигналы низкого уровня, то транзисторы VT1 и VT2 окажутся открытыми, а транзисторы VT3 и VТ4 — закрытыми. В результате на выходе Yокажется сигнал высокого уровня. Если хотя бы на одни из входов подан сигнал высокого уровня (1) , то хотя бы один из транзисторов VT1 или VТ2 окажется закрытым, a хотя бы один из транзисторов VT3 или VT4 — открытым. B результате сигнал на выходе Y окажется низкого уровня (0).

Москва, 2021 г.