3963

.pdf11

-------------------------------------------------------------------------------

--

-- Title |

: start |

-- Design |

: start |

-- Author |

: User |

-- Company |

: 12 |

-- |

|

-------------------------------------------------------------------------------

--

-- File |

: E:\my_designs\start\start\src\start.vhd |

|

-- Generated |

: Thu Apr 13 10:45:11 2017 |

|

-- |

From |

: interface description file |

-- |

By |

: Itf2Vhdl ver. 1.22 |

--

-------------------------------------------------------------------------------

--

-- Description :

--

-------------------------------------------------------------------------------

--{{ Section below this comment is automatically maintained

--and may be overwritten

--{entity {start} architecture {start}}

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity start is port(

x: in STD_LOGIC;

y: out STD_LOGIC

);

end start;

--}} End of automatically maintained section

architecture start of start is begin

-- enter your statements here -- end start;

12

Опишем элемент «инвертор». В описании вход x, выход y. Функция сум-

матора имеет вид.

Реализуем эту функцию в разделе архитектура. Полный текст модели (ис-

ключена часть комментариев) приведен ниже. Описание функций очевидно и не требует пояснений. Обратите внимание на символ присваивания <=.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity start is port(

x: in STD_LOGIC;

y: out STD_LOGIC

);

end start;

architecture start of start is begin

y <= not x; end start;

После ввода текста файла нужно выполнить его компиляцию. Компиляция текущего активного файла выполняется кнопкой Compile . Если в проекте не-

сколько VHDL-файлов и необходимо компилировать все, то нажимаете кнопку

Compile All.

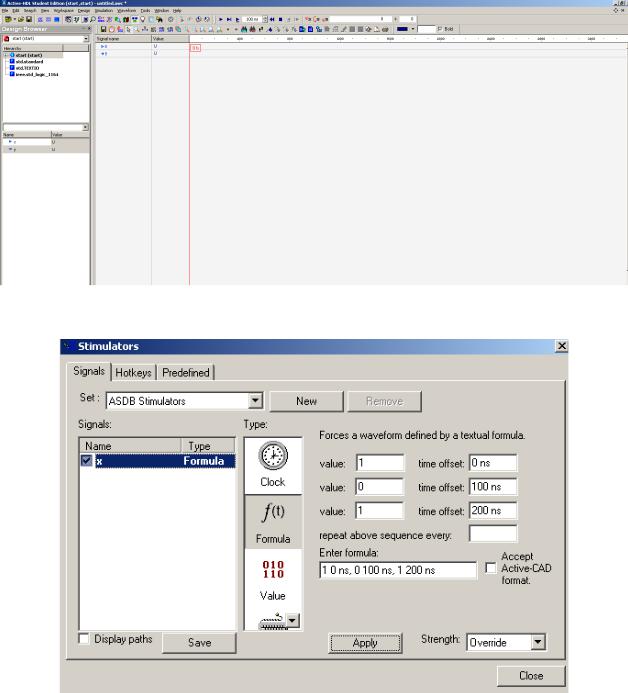

Следующим шагом работы с проектом является его моделирование. Пред-

варительно создаем окно (и файл) Waveform кнопкой . После создания окна формируем подмножество переменных для наблюдения в процессе моделирова-

ния. Для этого в окне проекта Design Browser активизируем окно

Structure (кнопки окон проекта в нижней части окна Design Browser). Пе-

ретаскиваем мышью в колонку Name окна Waveform имена переменных, кото-

рые необходимо наблюдать (формируем состав протокола моделирования). На рис. 8 приведен фрагмент окна моделирования. В число наблюдаемых включены вход X и выход Y элемента. Затем необходимо присвоить переменным значения.

13

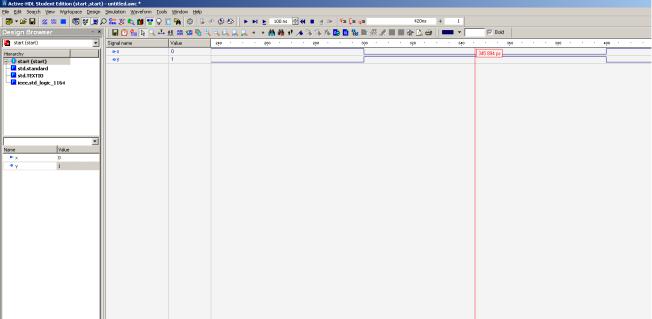

Это можно сделать в окне Stimulators, которое открывается кнопкой . Вид окна для рассматриваемого примера приведен на рис. 9.

Рисунок 8. Окно Design Browser.

Рисунок 9. Окно формирования (стимуляции) значений переменных. при моделировании Stimulators

Можно задавать значения непосредственно в поле Enter formula. Через за-

пятую вводятся пары: значение сигнала и, через пробел, момент времени. Ввод

14

заканчивается заданием периода повторения формулы. Обязательно указание размерности времени. После задания значений переменных следует задать об-

щее время моделирования в соответствующем окне панели, например 210нС , и

нажать кнопку Run.

Результат моделирования приведен на рис. 10. Показана часть панелей ин-

струментов. Как можно судить по результату, инвертор на уровне функций опи-

сан правильно.

Рисунок 10. Результат моделирования.

Варианты для самостоятельной работы:

1Создать блок И-НЕ и протестировать его функционирование.

2Создать блок И и протестировать его функционирование.

3Создать блок ИЛИ и протестировать его функционирование.

4Создать блок ИЛИ-НЕ и протестировать его функционирование.

5Какие из обеспечений САПР задействованы для выполнения задания.

15

Практическая занятие 2.

Пример проектирования устройства с использованием обеспече-

ний САПР

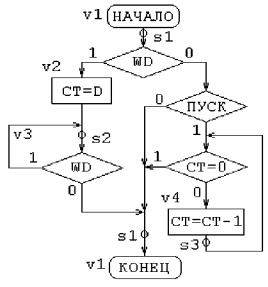

Будем проектировать устройство формирования пачки импульсов, рас-

смотренное в методических указаниях по формальному синтезу дискретных устройств (11). ГСА работы устройства приведена на рис. 21. На рисунке поме-

чены состояния управляющих автоматов Мили (обозначены как s1, s2 и s3) и

Мура (v1, v2, v3 и v4).

В таб. 1 приведена таблица переходов-выходов автомата Мили.

На ГСА приняты следующие обозначения:

D - четырехразрядная шина данных;

WD = 1 - готовность данных на шине D;

CT = D - команда записи данных в счетчик СТ, в таблице обозначена CTD;

ПУСК - команда на формирование пачки импульсов;

СТ = СТ - 1 команда на вычитание единицы из содержимого счетчика, в

таблице обозначена СТМ1;

СТ = 0 - счетчик СТ = 0000, в таблице обозначено СТО

Рис. 21. ГСА формирования пачки импульсов

16

Таблица 1

Исх. |

Вход |

Сост. |

Вы- |

|

|

рех. |

ход |

|

|

|

|

s1 |

WD |

s2 |

CTD |

|

WD-ПУСК |

s1 |

- |

|

WD-ПУСК- |

s1 |

- |

|

WD-ПУСК- |

s3 |

CTM1 |

|

CT0 |

|

|

s2 |

WD |

s2 |

- |

|

WD |

s1 |

- |

|

|

||

|

|

|

|

s3 |

CT0 |

s3 |

CTM1 |

|

CT0 |

s1 |

- |

|

|

|

|

При реализации регистров состояний и выходов на D-триггерах после до-

определения функций комбинационной части автомата Мили получим:

z1 = WDQ ■ Q2, |

|

z2 = WD ■ PUSK ■ CTO ■ Q2 + CTO ■ Q1, |

|

d1 = WD ■ PUSK ■ CT0 ■ Q2 + CTO ■ Q . |

d2 = WD ■ Q, |

В уравнениях ф и d2 - входы регистра состояний, ъх и z2 регистра выхо-

дов.

1.1. Модель УА Мили

Опишем функции комбинационной части УА на VHDL. --{entity {fgpi} architecture {fgpi}} library IEEE; use IEEE.STD_LOGIC_1164.all; entity fgpi is --

port( wd, pusk, ctO, q1, q2 : in STD_LOGIC; -- d1, d2, z1, z2 : out STD_LOGIC);

-end fgpi;

architecture fgpi of fgpi is –begin -- функции комбинационной части

17

автомата

z1<=wd and (not q1) and (not q2);

z2<=((not wd) and pusk and(not ctO) and (not q2)) or ((not ctO) and q1); d1<=((not wd) and pusk and (not ct0) and (not q2))or ((not ct0) and q1); d2<=wd and (not q1); end fgpi;

Память автомата реализуем на микросхеме ТМ8 - четыре D - триггера с общими входами начальной установки - r и записи по фронту импульса с (Рис.

-- File : TM8.vhd |

|

|

|

|

|

— 2 |

|

|

|

|

|

||

|

|

|

|

|

|

|

--{entity {TM8} architecture {TM8}} |

d1 |

|

T |

q1 |

о- 3 |

|

d2 |

|

|

q2 |

— 7 |

||

|

|

|

|

|||

library IEEE; |

12 |

d3 |

|

|

|

о- 6 |

|

13 |

d_ |

|

|

q3 |

— 1 |

|

9 |

|

|

|

|

0 o- |

|

'c |

|

|

|

||

|

|

|

|

11 |

||

|

|

|

|

|

q4 |

|

|

|

|

|

|

—15 |

|

|

|

|

r |

|

|

|

|

|

|

|

|

о- 14 |

|

|

|

|

|

|

|

|

|

Рис. 22. Микросхема TM8 |

|||||

22). Она так же описана на VHDL. |

|

|

|

|

|

|

use IEEE.STD_LOGIC_1164.all; |

|

|

|

|

|

|

-- |

Объект ТМ8 |

|

|

|

|

|

entity TM8 is |

|

|

|

|

|

|

port( d1, d2, d3, d4, c, r : in STD_LOGIC; |

|

|

|

|

|

|

q1, nq1, q2, nq2, q3, nq3, q4, nq4 : out STD_LOGIC); |

|

|

|

|

|

|

end TM8; |

|

|

|

|

|

|

-- |

Описание архитектуры (функционирование ТМ8) |

|||||

architecture TM8 of TM8 is begin

process (d1, d2, d3, d4, c, r) -- Вычисление процесса только при изменении

-- переменных, перечислены в скобках begin

18

-- Начальная установка при r=1 (RESET) if (r =

'1') then q1<='0'; nq1<='1'; q2<='0'; nq2<='1';

q3<='0'; nq3<='1'; q4<='0'; nq4<='1';

elsif (c'event and c='1' and r='0') -- Так выделяется фронт им-

пульса

-- запись данных по фронту тактового импульса then q1<=d1; nq1<= not d1; q2<=d2; nq2<= not d2; q3<=d3; nq3<= not d3; q4<=d4; nq4<= not d4;

end if; end process; end TM8;

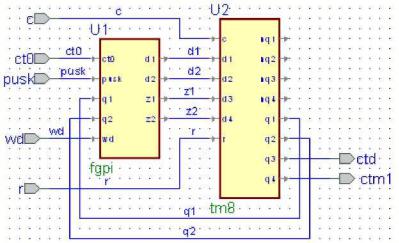

Объединим полученные модели в схему УА, которая в обозначениях AC- TIVE-HDL приведена на рис. Инверсные выходы триггеров не используются

19

Нажав кнопку ^ преобразуем схему в VHDL-текст. Затем выполним

п

реобразуем схему в VH компиляцию полученного VHDL текста (Compile ^ ) и

моделирование авто-

_п_г

мата (Waveform ™ ).

В таблице приведены результаты моделирования управляющего автомата.

Вертикальными линиями помечены моменты формирования выходных сигна-

лов.

Результаты моделирования управляющего автомата Мили

N |

|

S |

i . 5 . i Jp i . 15 i 2.0 i 25 i 3.0 i 35 i +.0 i |

|||||

г |

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

С |

|

C |

|

оля_алшялялги |

^ЛЯЛЯЛЯЛЛП |

|||

|

|

|

|

|

|

|

|

|

w |

|

W |

г |

|

г |

|

|

|

|

|

P |

|

_г |

|

_г |

|

|

|

|

|

|

|

|

|

|

|

ct |

|

T |

|

|

_г |

|

|

|

ct |

|

|

|

п |

|

п |

|

|

|

|

|

|

|

|

|

|

|

ct |

|

|

|

|

|

|

|

|

м |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

м |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.2. Операционная часть устройства

Для завершения проекта нам нужна модель счетчика, который может ра-

ботать в режиме параллельной записи данных и вычитания и логика для фор-

мирования сигналов. Используем счетчик ИЕ7, УГО которого приведено на рис.

25. Его функционирование также опишем на языке VHDL и выполним мо-

делирование для проверки правильности описания.

-- File : ie7.vhd --{entity {ie7} |

D |

CT16 |

Q |

|

|

15 - 1 1 |

1 |

3 |

|

architecture {ie7}} |

|

|||

- 10 - 2 |

|

2 |

2 |

|

|

|

|||

— Подключение необходимых библиотек |

9 - 3 |

|

3 |

6 |

library IEEE; |

4 |

|

4 |

7 |

11 -cl dw |

|

|

|

|

-- библиотека логических переменных и операций |

|

|

|

|

5 4 |

|

|

|

|

|

~7 cu |

|

wpu t>- 12 |

|

use IEEE.STD_LOGIC_1164.all; |

14 -I |

|

||

u ucd |

|

wpd |

Ё>- |

|

-- библиотеки двоичной арифметики use |

urs |

|

||

|

|

|

||

|

|

13 |

|

|

|

|

|

|

|

IEEE.STD_LOGIC_ARITH.all; use |

Рис. 25. УГО микросхемы ИЕ7 |

|||

|

|

|

|

|

IEEE.STD_LOGIC_UNSIGNED.all;

-- описание портов (входов-выходов) объекта entity ie7 is port(

d1, d2, d3, d4, dw, ucu, ucd,urs: in STD_LOGIC; q1, q2, q3, q4, wpu, wpd : out STD_LOGIC); end ie7;

-- Описание функционирования счетчика architecture ie7 of ie7 is

signal z : STD_LOGIC_VECTOR(0 to 3); -- внутреннее состояние счетчика begin

N: process (d1, d2, d3, d4, dw, ucu, ucd,urs) begin

--Начальная установка сигналов при urs=1 if (urs=T) then z<=(others=>'0') ; wpu<='0'; wpd<='0';

--параллельная запись данных с входов D elsif (urs='0' and dw='0') then z(0)<=d1; z(1)<=d2; z(2)<=d3; z(3)<=d4;

--Режим суммирования

elsif (urs='0' and dw='1' and ucd-1' and ucu'event and ucu='1')

then if(z(0)='1' and z(1)='1' and z(2)='1' and z(3)='1') then wpu<='1'; end if; z <= z + 1 ;

-- Режим вычитания