999

.pdfФедеральное агентство по образованию Государственное образовательное учреждение высшего профессионального образования

«Воронежская государственная лесотехническая академия»

МИКРОПРОЦЕССОРНАЯ ТЕХНИКА

Методические указания к лабораторным работам для студентов специальностей

210200 (220301) – Автоматизация технологических процессов и производств (лесной комплекс),

240400 (190702) – Организация и безопасность движения (автомобильный транспорт)

Воронеж 2007

2

УДК 681.325

Данилов, А. Д. Микропроцессорная техника [Текст] : метод. указания к лабораторным работам для студентов специальностей 210200 (220301) – Автоматизация технологических процессов и производств (лесной комплекс), 240400 (190702) – Организация и безопасность движения (автомобильный транспорт) / А. Д. Данилов, В. И. Кочетов, М. А. Кривотулова ; Фед. агентство по образованию, ГОУ ВПО «ВГЛТА». – Воронеж, 2007. − 20 с.

Печатается по решению редакционно-издательского совета ГОУ ВПО «ВГЛТА»

Рецензент д-р техн. наук, проф. Ю.С. Сербулов

Научный редактор д-р техн. наук, проф. В.С. Петровский

3

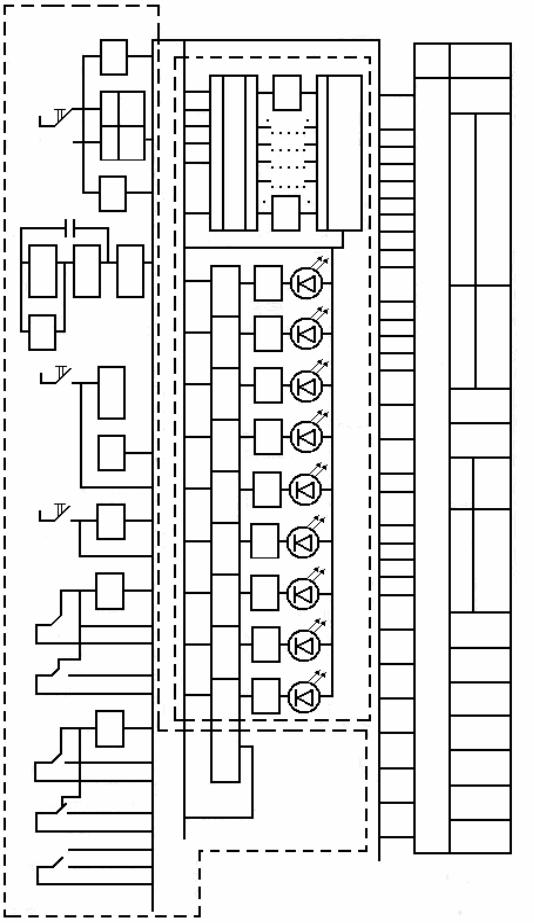

ОПИСАНИЕ ЛАБОРАТОРНОГО СТЕНДА

Универсальный стенд предназначен для выполнения нескольких лабораторных робот. Он содержит блок питания, блок управления и ввода информации, блок индикации. Стенд имеет разъем XI, в который вставляются сменные платы, зависящие от содержания выполняемой работы. Принципиальная схема блоков индикации, управления и ввода информации представлена на рис.1.

На передней (наклонной) панели стенда установлены тумблеры (SA1 – SA5) и кнопки (SB1 – SB3) ввода информации и задания режимов работы исследуемых устройств. Выводы всех тумблеров и кнопок, кроме SB1, подключены непосредственно к контактам разъема X1.

Переключатели SA1 – SA4, SВ2 и SB3 предназначены для подачи логических сигналов с уровнями "0" (соответствующий вывод замкнут на общий провод) или "1" (вывод – на +5В). Тумблер SA5 подключается всеми своими выводами к разъему и поэтому может использоваться в качестве переключателя "двух сигналов в одну линию" или наоборот, "одного сигнала на два направления". Кнопка SB1 подключена к схеме зашиты от "дребезга" на триггере (микросхема D1.1.). С помощью этой кнопки на выходе триггера (27 контакт разъема X1) формируется одиночный импульс с крутыми фронтами, необходимый для нормальной работы исследуемых триггеров, регистров и счетчиков. При нажатии SB1 на 27 контакте появляется логический 0, а при отпускании – логическая 1. Этот блок в дальнейшем на схемах обозначается как формирователь одиночного импульса (Fn).

Ha передней панели блока установлен светодиодный дисплей для индикации режимов работы, а также входной и выходной информации исследуемого устройства. Дисплей состоит из девяти светодиодов HL1 – HL9, позволяющих индицировать в 9 разрядах уровни логической "1"(светодиоды светятся) и логического "0" (не светятся), и семисегментного индикатора HG1 для индикации числа в десятичном или шестнадцатиричном кодах.

Индикатор HG1 подключается к исследуемой схеме через дешифратор на ИМС D5, преобразующий четырехразрядный двоичный код (на контактах 11 – 14 разъема X1) в семисегментный код индикатора HG1. При низком уровне напряжения на входе 14 ИМС D5 (контакт 15 разъема X1) на индикаторе HG1 индицируется число в десятичном коде, при высоком уровне – в шестнадцатиричном. Светодиоды HL1 – HL9 подключаются к элементам схемы через инверторы D3.1 – D3.4, D3.6. D4.1 – ГМ.4. В дальнейшем устройство, содержащее дешифратор D5, индикатор HG1, инверторы с подключенными к ним светодиодами НL1 – HL9, обозначается как блок индикации (БИ).

Блок управления

1

R2

sb1

R T

S D1.1

27

1

R3

C1

30

1 1 1

D2.1 D2.2 D2.3

R1

sb2 |

|

|

1 |

25 |

||

|

|

|

||||

1 |

2 |

|

|

D2.5 |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

R21 |

1 |

|

|

|

|

|

|

19 |

sb3 |

|

|

|

|

|

|

|

|

|

|

|

R22 |

1 |

1 |

2 |

|

|

|

|

|

|

|

|

|

|

|

18 |

|

3 |

|

|

R23 |

1 |

|

sa1 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

1 |

2 |

|

|

|

20 |

|

sa2 |

3 |

|

|

|

|

16 |

|

|

|

|

|

||

1 |

2 |

|

|

|

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

R24 |

1 |

|

3 |

|

|

|

|

|

sa3 |

|

|

|

|

|

16 |

|

|

|

|

|

|

|

1 |

2 |

|

|

|

22 |

|

|

|

|

|

|

|

|

sa4 |

|

|

|

|

|

16 |

|

|

|

|

|

|

23 |

31

sa5 |

26 |

|

|

|

24 |

4

Блок индикации

11 |

1 |

|

DC a |

R4 |

a HG1 |

|

12 |

2 |

|

b |

|

b |

|

13 |

|

|

||||

3 |

|

c |

|

c |

||

14 |

4 |

|

d |

|

d |

|

15 |

|

|

||||

5 |

|

e |

|

e |

||

|

|

|

||||

|

|

|

f |

|

f |

|

16 |

|

|

g |

R11 |

g |

|

V DS h |

h |

|||||

|

||||||

|

|

|||||

1 |

|

|

|

|

|

|

10 |

1 |

|

R12 |

HL1 |

||

|

|

|||||

|

D3.4 |

|

|

|||

2 |

1 |

|

R13 |

|

||

|

|

HL2 |

||||

|

|

|

|

|||

|

|

|

|

|

||

|

D2.6 |

|

|

|||

3 |

1 |

|

R14 |

HL3 |

||

|

|

|||||

|

D3.1 |

|

|

|||

4 |

1 |

|

R15 |

HL4 |

||

|

|

|||||

|

D3.2 |

|

|

|||

5 |

1 |

|

R16 |

HL5 |

||

|

|

|||||

|

D3.3 |

|

|

|||

6 |

1 |

|

|

HL6 |

||

|

|

R17 |

||||

|

|

|

|

|

||

|

D4.4 |

|

|

|||

7 |

1 |

|

R18 |

HL7 |

||

|

|

|||||

|

D4.1 |

|

|

|||

8 |

1 |

|

|

HL8 |

||

|

|

R19 |

||||

|

|

|

|

|

||

|

D4.2 |

|

|

|||

9 |

1 |

|

R20 |

HL9 |

||

|

|

|

|

|||

|

D4.3 |

|

|

|||

17 |

1 |

|

|

|

||

|

D4.5 |

|

|

|||

|

|

|

||||

25 |

|

|

|

|

|

|

|

Конт. |

Цепь |

||||

1 |

1 |

+5 в |

||||

|

||||||

|

|

|||||

2 |

2 |

HL |

2 |

|

|

|

|

|

|

||||

3 |

3 |

|

3 |

|

||

4 |

4 |

|

4 |

|

|

|

5 |

5 |

|

5 |

|

||

6 |

6 |

|

6 |

|

|

|

7 |

7 |

|

7 |

|

|

|

8 |

8 |

|

8 |

|

|

|

9 |

9 |

|

9 |

|

||

|

|

|

|

|

||

10 |

10 |

|

1 |

|

||

|

|

|

|

|||

11 |

11 |

DC |

1P |

|||

12 |

12 |

|||||

|

2P |

|||||

|

|

|||||

13 |

|

|

||||

13 |

|

3P |

||||

|

|

|||||

14 |

|

|

||||

14 |

|

4P |

||||

|

|

|

||||

15 |

15 |

|

V |

|||

16 |

16 |

Общ. |

||||

|

|

|||||

17 |

17 |

Вх. НЕ |

||||

|

|

|||||

18 |

18 |

|

1 |

|

||

|

|

SB |

|

|||

19 |

19 |

|

|

|

||

|

2 |

|

||||

|

|

|

|

|||

20 |

20 |

SA |

|

|

|

|

21 |

|

1 |

|

|

||

21 |

|

|

|

|||

|

|

|

|

|||

|

|

|

|

|

||

22 |

22 |

|

2 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

||

23 |

23 |

|

3 |

|

||

|

|

|

|

|||

|

|

|

|

|

||

24 |

24 |

|

4 |

|

|

|

|

5 |

|

||||

|

|

|

|

|||

25 |

25 |

Вых. НЕ |

||||

|

|

|||||

26 |

26 |

SA5 |

|

|

|

|

|

|

|

|

|

||

27 |

27 |

Вых. F |

|

|

||

28 |

28 |

|

|

|

|

|

Резерв |

||||||

|

|

|||||

29 |

29 |

Вых. НЕ |

||||

|

|

|||||

30 |

30 |

Вых. G |

||||

|

|

|||||

31 |

31 |

SB5 |

|

|

|

|

Рис. 1 Схема блоков индикации, управления и ввода информации

5

Помимо описанных устройств ввода и вывода информации стенд содержит следующие вспомогательные устройства:

− инвертор на элементе D4.5, используемый при работе с платами D3,

D4;

−генератор прямоугольных импульсов на элементах D2.1 – D2.3 с выходом на X1/30. Частота колебаний генератора в пределах 2...10 кГц:

−инвертор на элементе D2.6, используемый при работе с платой П6.

Тумблеры и кнопки, формирователь F , инверторы D2.6 и D4.5 образуют блок управления.

ЛАБОРАТОРНАЯ РАБОТА N 1

Исследование логических элементов

Цель работы – исследование поведения основных логических элементов при подаче на них двоичных потенциальных сигналов.

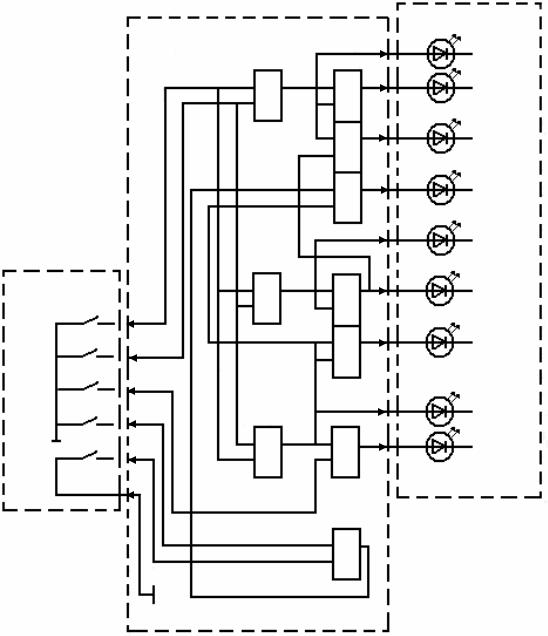

Описание сменной платы П1

Схема платы П1 приведена на рис. 2. Плата обведена пунктиром, а ключи и индикаторы находятся на стенде. В качестве элемента D1 используется ИМС К155ЛЕ1, D2 – К155ЛА3, D3 – К155ЛП5.

Порядок выполнения работы

1.Выделить и изобразить отдельно схему реализации логической функции Y = X1 X2. Экспериментально получить таблицу истинности функции (карта 1.2).

2.Аналогично п.1, но для Y = X1 X2 (карта 1.1).

3.Аналогично п.1. на для Y = X1 X2 (карта 1.4).

4.Аналогично п.1, но для Y = X1 X2 (карта 1.3).

5.Используя элемент D3 "исключающее ИЛИ" (сложение по модулю 2), выделить и изобразить отдельно схему реализации функции Y = X1+ X2. Экспериментально получить и заполнить таблицу истинности функции. Синтезировать функцию на элементам И-НЕ и изобразить полученную схему (карта 1.5).

6. Аналогично п.1, но для Y = X1 X2 (иначе Х1Х – "исключающее ИЛИ-НЕ", равнозначность) (карта 1.6).

Блок

управления

SA1

SA2

SA3

SA4

SA5

6

П1 |

|

2 |

1 |

1 |

4 |

D1.1 |

D1.2 |

|

|

1 |

8 |

|

|

|

|

D1.3 |

|

|

1 |

10 |

|

|

|

|

D1.4 |

|

|

|

3 |

& |

& |

5 |

|

||

D2.1 |

D2.2 |

|

20 |

|

|

21 |

& |

7 |

D2.3 |

|

|

|

|

|

22 |

|

|

|

|

6 |

23 |

|

|

=1 |

=1 |

9 |

24 |

D3.2 |

|

D3.1 |

|

25

=1

D3.3

Блок индикации

HL2

HL4

HL8

HL1

HL3

HL5

HL7

HL6

HL9

Рис. 2 Схема платы П1 и ее подключение к основному блоку

7.Исследовать одноразрядный полусумматор, используя ключи SA1, SA2 в качестве булевских переменных X1, Х2, светодиод HL8 для индикации суммы, a HL5 – переноса. Выделить и изобразить, часть схемы, реализующую полусумматор. Доказать тождественность уравнений полусумматора функциям выделенной схемы. Экспериментально исследовать схему. Синтезировать полусумматор на элементах И-НЕ (карта 1.9).

8.Исследовать устройство побитового сравнения двух двухразрядных чисел Х1Х0 и Z1Z0. В качестве X1, Х0 использовать SAl, SА4, a Z1, Z0 – SА2, SA5. Результат сравнения наблюдать на светодиоде HL1. Два числа равны, если X1=Z1 и X0=Z0. Составить таблицу истинности и по ней

7

логическое уравнение условия равенства чисел. По уравнению синтезировать устройство сравнения на элементах И-НЕ. Выделить и изобразить схему сравнения на элементах D1, D3. Составить уравнение функционирования схемы и, преобразовав его к СДНФ, сравнить с предыдущим. Исследовать работу схемы экспериментально (карта 1.8).

9. Исследовать трехразрядное устройство проверки на нечетность. Источниками сигнала являются тумблеры SAl, SA2, SA3. Индикатором нечетного количества истинных бит в слове – HL9. Выделить, и изобразить схему контроля. Получить экспериментально таблицу истинности и по ней составить уравнение в СДНФ. Составить уравнение в СДНФ непосредственно по виду схемы. Сравнить оба полученных уравнения (карта 1.7).

Отчет о работе

Отчет должен содержать:

1.Схему (выделенную из рис. 2) и экспериментальную таблицу истинности функции ИЛИ.

2.Аналогично п.1, но для ИЛИ-НЕ.

3.Аналогично п.1, но для И.

4.Аналогично п.1, но для И-НЕ.

5.Аналогично п.1, но для "исключающего ИЛИ".

6.Схему элемента "исключающее ИЛИ", синтезированного по элементам И-НЕ.

7.Аналогично п.1. но для элемента "исключающее ИЛИ-НЕ".

8.Аналогично п.6, но для элемента "исключающее ИЛИ-НЕ".

9.Схемы (выделенную из рис. 2 и общепринятую условную) полусумматора.

10.Экспериментальные таблицы истинности для суммы и переноса.

11.Аналитическое доказательство тождественности уравнений полусумматора по рис. 2 и по таблице истинности.

12.Схему полусумматора, синтезированного на элементах И-НЕ.

13.Схему сравнения двух чисел (выделенную из рис. 2), экспериментальную таблицу истинности, логическое уравнение, составленное по схеме.

14.Доказательство эквивалентности уравнения для схемы сравнения по рис.2 и по таблице истинности.

15.Схему проверки на нечетность, таблицу истинности, уравнения в СДНФ, составленные но таблице.

16.Уравнения в СДНФ для схемы проверки нечетности, составленные непосредственно по схеме рис.2.

17.Доказательство эквивалентности уравнения по п.п. 15, 16.

Вопросы для самоконтроля

8

1.Таблицы истинности, логические уравнения, обозначение конъюнкции, дизъюнкции, инверсии, сумматора, а также графические обозначения элементов, реализующих указанные функции.

2.Булевские переменные и их реализация в элементах.

3.Синтез примитивного автомата по таблице истинности.

4.Основные законы алгебры логики.

5.Определение ДНФ и СДНФ.

6.Функциональная полнота логических функций.

7.Приведение булевских уравнений к монофункциональному базису.

ЛАБОРАТОРНАЯ РАБОТА N 2

Исследование триггеров

Цель работы – исследование режимов работы триггеров на ИМС.

Описание сменной платы П2

Принципиальная схема платы П2 приведена на рис. 3. Цифры на границах пунктирного прямоугольника означают номера контактов на разъеме X1. Блоки управления и индикации расположены в основном блоке ввода-вывода стенда и используются при работе с данной платой.

Порядок выполнения работы

1.Выделить и изобразить отдельно схемы RS-триггера на элементах ИЛИ-НЕ. В качестве источника сигнала использовать кнопки SB2, SB3. Состояние триггера определять с помощью диодов HL3, HL4.Сигналы управления триггером индицируются со светодиодами HL1, HL2.

Заготовить форму таблицы переходов триггера и экспериментально заполнить ее. Обратить внимание на запрещенное состояние.

2.Аналогично п.1, но для RS-триггера на элементах И-НЕ. Сигналы управления в инверсном виде индицируются светодиодами HL1, HL2.

Блок управления

SB2

SB3

SA1

SA5

SA3

SB1 F

|

9 |

|

|

П2 |

|

& |

Блок индикации |

|

|

|

|

|

|

D1.1 |

|

|

|

|

5 |

|

|

|

HL5 |

|

|

& |

6 |

|

|

HL6 |

|

|

|

D1.2 |

|

|

|

|

|

|

|

|

10 |

|

|

|

HL1 |

19 |

|

|

3 |

|

& |

& |

HL3 |

18 |

D2.1 |

D2.2 |

|

|

|

|

|

20 |

|

|

|

31 |

|

|

4 |

|

& |

& |

HL4 |

|

D2.3 |

D2.4 |

|

24 |

|

|

2 |

|

|

|

HL2 |

26 |

|

|

9 |

|

R |

T |

|

|

HL9 |

||

|

|

||

22 |

D |

|

|

|

|

|

|

27 |

C |

|

|

|

|

|

|

|

|

D3.1 |

8 |

|

S |

HL8 |

|

X1 |

X2 |

|

7 |

|

D |

|

|

|

T |

HL7 |

Y1

CD3.2

Рис. 3 Схема платы П2 и ее подключения к основному блоку

3.Аналогично п.2, но используется RS-триггера в интегральном исполнении на микросхеме D3.1. Выходы D, С не используются (кнопка SB1 не нажата, a SA1 находится в выключенном состоянии). Выходная информация выводится на индикаторы HL9 (прямой выход) и HL8 (инверсный).

4.Выделить и изобразить отдельно схему тактируемого D-триггера на ИМС D3.1. На выходы R, S подать логические единицы. Экспериментально получить таблицу переходов. По полученной таблице составить временную диаграмму напряжений на инверсном выходе по известным сигналам на входах D и С. Провести эксперимент, подтверждающий, что запись

10

информации происходит по фронту синхроимпульсов.

5.На базе ИМС D3.2 путем надлежащей коммутации превратите D- триггер в Т-триггер. Исследовать работу Т-триггера.

6.Соединив перемычки X1 и X2 получить последовательное включение D-триггеров на ИМС D3.1 и D3.2. Манипулируя SA1, наблюдать продвижение информации по системе, используя светодиоды HL9, НL7. Изобразить временные диаграммы процессов.

Отчет о работе

Отчет должен содержать:

1.Схему RS-триггера на элементах ИЛИ--ИЕ и экспериментальную таблицу переходов.

2.Аналогично п.1, но на элементах И-НЕ.

3.Аналогично п.1, но на ИМС D3.1.

4.Схему тактируемого D-триггера, экспериментальную таблицу переходов, временные диаграммы напряжения на инверсном выходе, сигнальном и тактовом входах.

5.Схему Т-триггера на базе D-триггера, экспериментальную таблицу переходов, временные диаграммы.

6.Схему последовательно соединенных двух D-триггеров и временные диаграммы продвижения цифры Е.

Вопросы для самоконтроля

1.Схемы и таблицы переходов тактируемых и нетактируемых RSтриггеров на логических элементах.

2.Схемы и таблицы переходов D, Т, JК-триггеров .на ИМС.

3.Принцип работы двухступенчатых триггеров.

4.Способы превращения JK-триггера на ИМС в RS, D, Т - триггеры.