Лекции / Схемотехника ЭВМ. Лекция 08. Риски сбоя

.pdfГлава 8. Риски сбоя в комбинационных схемах

Риском сбоя называется возможность появления на выходе цифрового устройства сигнала, не предусмотренного алгоритмом его работы и могущего привести к ложному срабатыванию. Отметим, что риск сбоя представляет собой только возможность ложного срабатывания. Конкретная цепь может давать риск сбоя, а может и не давать, причем даже при наличии риска сбоя может отсутствовать ложное срабатывание, следовательно, риск сбоя

представляет собой наихудший случай.

Проектирование цифровой аппаратуры с использованием принципов комплексной миниатюризации на основе достижений микроэлектроники в качестве основной из своих задач выдвигает проблему обеспечения устойчивости ее функционирования при влиянии коструктивнотехнологических факторов и дестабилизирующих воздействий внешней среды [12, 22-24].

Функциональная устойчивость определяется стабильностью реализации цифровым устройством заданного алгоритма работы при наличии разброса задержек выполнения операций в логических элементах, задержек сигналов в линиях связи и электромагнитных наводок паразитных сигналов. Термин “функциональная устойчивость” можно рассматривать также как синоним алгоритмической устойчивости.

В схемотехническом плане проблема функциональной устойчивости может быть сведена к устранению опасных состязаний (гонок) сигналов устройства. Эффект состязаний сигналов, приводящий к неустойчивой работе цифрового устройства, известен давно. Наиболее наглядный пример - эффект “дребезга” контактов реле, кнопок и других электромагнитных устройств. Проблема гонок в цифровой схемотехнике является очень серьезной. Большинство трудно обнаруживаемых и удивительно разнообразно проявляющихся ошибок в цифровых схемах связано именно с гонками, возможность появления которых разработчик не предвидел или не заметил.

Состязаниями (гонками) сигналов называется процесс их распространения в различных цепях цифрового устройства при существовании разбросов временных задержек этих цепей. Цепь - совокупность логических и других элементов и линий связи между ними. Алгоритмическим переходом называется изменение сигнала на выходе какой-либо схемы, предусмотренное алгоритмом ее работы. Неалгоритмическим переходом называется изменение выходного сигнала, не предусмотренное алгоритмом ее работы. Опасными называются такие состязания, которые могут привести к неалгоритмическому переходу в цифровой схеме при заданных условиях ее работы, а неопасными называются такие состязания, которые не могут привести к неалгоритмическому переходу. Схемой, свободной от влияния опасных состязаний, называется такая цифровая структура, в которой неалгоритмический переход, возникший в части схемы из-за опасных состязаний, не изменяет алгоритма работы схемы в целом при заданных условиях ее работы.

Задержка логической схемы слагается из задержек срабатывания логических элементов и задержек распространения сигналов по цепям связи между ними. Важнейшим параметром, характеризующим инерционность логического элемента, является среднее время задержки выходного сигнала по отношению к входному tзд.ср.. Трудоемкость учета задержек зависит от соотношения значений задержек самих логических элементов и задержек в цепи связи tсв.. Если эти значения близки, то задержки различных трактов схемы можно определить лишь после размещения элементов на поверхности печатной платы или кристалла БИС, когда станут известны фактические длины связей. В сверхбыстродействующих ИС и БИС, построенных на ТТЛШ- и ЭСЛэлементах, время задержки выполнения логической операции в вентиле (логическом элементе) оценивается единицами или десятыми долями наносекунды. В этом случае не считаться с tсв. нельзя.

Ситуации, когда задержки tсв. превышают tзд.ср., возникают и при использовании не очень быстродействующих элементов, когда сигналы передаются между блоками на достаточно большое расстояние. Однако доля подобных связей невелика, поэтому их можно выделить особо и учесть tсв. в линии связи. Тем не менее для большинства микроэлектронных устройств сейчас (90-е годы) выполняется соотношение tсв. < tзд.ср..

Задержки различных экземпляров элементов какой-либо серии имеют технологический разброс, который обычно описывают некоторым статистическим законом. Дестабилизирующие воздействия внешней среды, в основном выражающиеся в изменении температуры, напряжения питания и в воздействии радиационного излучения, приводят к расширению диапазона вариации задержки выполнения операции в логических элементах и поэтому могут быть сведены к эквивалентному расширению влияния конструктивнотехнологических факторов. Задержка каждого конкретного элемента зависит от количества и типа нагрузок, от паразитной емкости монтажа, числа лет с момента выпуска и ряда других факторов. Точное значение величины tзд.ср. для конкретного случая не известно, так как в технических условиях изготовитель указывает значение tзд.ср.max для наихудших условий применения. Разработчику часто полезно знать кроме максимальной еще и минимально возможную величину tзд.ср.. К сожалению, для большинства серийно выпускаемых микросхем значение минимальной задержки в технических условиях не указано и, следовательно, изготовителем не гарантируется. Поэтому если разработчик аппаратуры, предназначенной для серийного выпуска, использует микросхемы, в паспорте которых не оговорено минимальное значение задержки, то он вынужден полагать его равным нулю. Никаких юридических оснований считать, что это значение больше нуля у него нет [24].

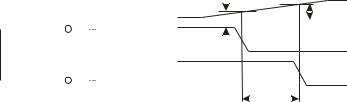

Специфическим фактором, приводящим к разбросу tзд.ср., является длительность фронта (спада) входного сигнала при наличии разброса порогов срабатывания логических элементов. Особенно важно не допускать малой

крутизны фронта или спада в схемах на элементах типа КМДП, в которых возможен большой разброс пороговых напряжений. Такое явление часто называют гонками по входу (рис.8.1). Опасностью возникновения гонок по входу объясняются ограничения на максимальную длительность переходов 01 и 10 входных сигналов, приводимые в паспортах многих микросхем.

а |

|

|

|

|

|

|

б Вход |

|

Uпор.1 |

|

|

Uпор.2 |

||

|

|

|

|

|

|

|

|

|

||||||

|

|

1 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

Выход |

. |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

1 |

|

|

|

2 |

2 |

|

|

|

|

|

||||

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

∆τ |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 8.1 Гонкипо входу: а- две ветвящиеся цепи; б - временные диаграммы.

На практике изменение набора входных переменных комбинационной схемы часто происходит при несогласованных во времени изменениях различных входных переменных. При этом схема фактически находится под действием нескольких последовательно сменяющихся наборов, причем каждый из них дробится еще на несколько наборов при прохождении через схему из-за несогласованных значений tзд.ср. элементов. В результате изменение сигнала на каждом выходе схемы и внутреннем узле реально происходит не мгновенно, а образует некоторый сложный динамический процесс. Нахождение этих процессов называется динамическим анализом комбинационной схемы.

Динамический анализ ведут с учетом следующих обстоятельств. 1. Изменение входного набора схемы состоит из неодновременных

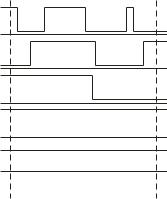

изменений различных входных переменных, образующих этот набор. Поэтому последовательность входных наборов можно рассматривать как набор входных последовательностей из нулей и единиц, действующих независимо друг от друга на разных входах. Переключательным процессом называется последовательность уровней “1” и “0” (импульсов и пауз), которая на любом конечном наблюдаемом интервале времени содержит конечное число переходов 01 и 10. Примеры переключательных процессов

приведены на рис.8.2. Длиной переключательного процесса называется общее число изменений сигнала в нем. Например, для процесса x4 на рис.8.2 длина равна 3. Переключательный процесс называется сложным, если его длина больше или равна 2. В противном случае он называется простым переключением.

x5

x4

x3

x2

x1

x0

t |

|

n |

|

|

|

tn+1 |

|||

Рис. 8.2 Переключательные процессы, приводящие к изменению постоянного значения сигнала: X5, X3- изменения1  0;

0;

x4,x2 - 0  1; x1 - 1

1; x1 - 1 1; x0 - 0

1; x0 - 0  0.

0.

Для векторного процесса (переключения совокупности переменных) соответствующим понятием является вектор длин. Компоненты этого вектора - длины процессов, являющихся компонентами векторного процесса. Например, векторный процесс, компонентами которого являются шесть процессов на рис.8.2, имеет вектор длин (5,3,1,1,0,0). Векторный переключательный процесс считается простым переключением, если все его компоненты - простые переключения, совершаемые одновременно. В противном случае векторный процесс считается сложным. На рис.8.2 набор (вектор) Х1 =x5x4x3x2x1x0 = 101010 изменяется на набор (вектор) Х2 = 010110.

2. Помимо логических элементов в схеме могут иметься специальные вспомогательные элементы - задержки. Задержки, связанные с логическими элементами и линиями связи, обычно называют паразитными задержками, чтобы отличить их от задержек, которые могут быть введены в цепь для гарантирования должного функционирования (например, при реализации разностных преобразователей или детекторов событий ). Событие - любое

изменение логического сигнала, в том числе сложный переключательный процесс.

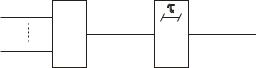

Представляют интерес два вида задержек. Первый тип - чистая задержка, которая при подаче на вход сигнала x(t) обусловливает на выходе сигнал y(t-τ), где τ - величина задержки. Таким образом, выход является просто задержанным на фиксированную величину переключательным процессом, а формы (длины!) выходных и входных процессов являются идентичными. Инвертирование сигнала, следовательно, не рассматривается как изменение формы.

Второй тип - инерционная задержка или фильтр. Фильтр осуществляет ту же операцию, что и чистая задержка, но сверх того не пропускает на выход изменений входного сигнала, отстоящих одно от другого по времени менее чем на τ , благодаря чему процесс на выходе может изменить форму. На рис.8.3 показано различие между чистой и инерционной задержкой (фильтром). Справедливо утверждение, что паразитные задержки имеют компоненты как чистой, так и инерционной задержки.

x

y1

y2

Рис.8.3. Поведение цепипри чистойи инерционной задержках: x - входной сигнал; y1- выходной сигнал чистойзадержки;

y2 - выходной сигнал инерционной задержки.

3. Каждый инерционный логический элемент в большинстве случаев можно представить в виде модели, содержащей последовательное соединение безынерционного логического элемента, реализующего безынерционное преобразование Z = f(X), с элементом задержки (иногда фильтром) на τ (рис.8.4). Под τ подразумевается паразитная задержка. Величину τ , а также моменты изменений входных переменных схемы, называют временными параметрами. Очевидно, что в общем случае значение τ моделирующей задержки зависит от того, какое изменение сигнала 01 или 10 имеет место на выходе элемента, то есть τ = τ01 и τ10 . В простейшем случае τ01 = τ10 = τ .

xn-1 |

ЛЭ |

Z |

y |

x0

Рис.8.4. Модельинерционного логического элемента.

В различных частях комбинационной схемы в зависимости от числа последовательно включенных элементов переходный процесс после смены входного набора будет заканчиваться в разное время. Это приведет либо к

деформированию длительности выходных сигналов либо к появлению

рисков сбоя. И то и другое в отдельных случаях может нарушить нормальную работу последующих устройств.

8.1. Деформирование длительности полезных выходных сигналов

Если сигналы в схеме распространяются по цепочкам, задержки в которых различны, то это приводит к смещению сигналов относительно друг друга во времени. В свою очередь, это может вызвать уменьшение длительности сигнала “1” на выходе элемента И и увеличение - на выходе ИЛИ. На рис.8.5 приведены схема и временные диаграммы, поясняющие деформирование длительности выходных сигналов при переключении инерционных логических элементов.У выходных сигналов y1 и y2 в начале и в конце будут зоны неопределенности длительностью по 3τ каждая. В

частном случае при τ = 0 выходные сигналы y1 и y2 почти повторяют входные. Однако, если задержки τ максимальны, то на входах элементов D5 и D6 они могут появиться с разбросом по времени на 2τ .

а)

x1 |

& |

|

& |

& |

|

D1 |

|

D3 |

y1 |

1 |

1 |

D5 |

||

x0 |

& |

|

& |

1 |

|

|

|

|

y2 |

1 |

D2 |

1 |

D4 |

D6 |

б)

T

x1;x0

D1;D2

2

D3;D4

y1

y2

Рис.8.5 Деформирование длительностивыходных сигналов: а - схема; б - временные диаграммы.

Понятие одновременности расплывается и становится относительным. В худшем случае сигнал y1 будет иметь длительность Т- 2τ , а y2 - Т + 2τ , причем фронты (спады) этих сигналов могут быть сдвинуты по отношению к входным сигналам на 3τ . Возможны и любые промежуточные формы рассмотренных частных случаев, причем предугадать характер деформирования заранее невозможно. Если цепочка (до входов элементов D5 и D6 содержит k элементов, то во всех рассмотренных случаях вместо двойки в качестве множителя при τ войдет k. У разработчика нет никаких официальных документов, позволяющих проигнорировать любой из

возможных эффектов, и он вынужден проектировать схему так, чтобы ни один из них не привел к сбою в работе. Если на выходе схемы требуется получить импульс с длительностью Т, то длительность импульса на входе цепочки должна быть на kτ больше. Аналогично нужно обеспечивать на выходе схемы и минимальную длительность паузы и максимальную длительность импульса, если это требуется. Двухстороннего допуска на длительность импульса, менее жесткого, чем ±kτ , требовать нельзя.

Сказанное позволяет сделать вывод, что деформирование выходного сигнала может настолько уменьшить длительность уровней “1” и “0”, что элементы D5 и D6 могут стать для них фильтрами, то есть полностью нарушить логику работы схемы. Итак, деформирование выходного сигнала может привести к исчезновению алгоритмически верного сигнала.

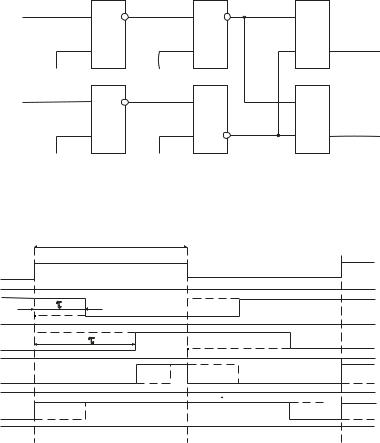

8.2. Статические риски сбоя

На рис.8.6 показана работа элементов И и ИЛИ при подаче на их входы двух последовательных во времени наборов Х1 = x1x0 = 01 и Х2 = x1x0 = 10. Значение сигнала y1 для элемента И на этих наборах должно оставаться постоянным и равным 0, а y2 - равным 1. Это выполняется для случаев разброса во времени моментов переключения переменных x1 и x0, показанных на рис.8.6,а и г. Если же этот разброс соответствует рис.8.6,б и в, то видно, что на выходе схемы И появится логический сигнал 1 длительностью ∆τ1 , а на выходе схемы ИЛИ - сигнал 0 длительностью ∆τ2 . Эти ложные сигналы и являются рисками сбоя, причем видно, что они могут быть, а могут и отсутствовать. Все дальнейшие примеры будут иллюстрироваться временными диаграммами для наихудшего случая, когда риск сбоя обязательно имеет место.

|

x1 |

|

|

|

& |

|

y1 |

|

|

|

x1 |

|

|

|

|

1 |

|

y2 |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

x0 |

|

|

|

|

|

|

|

|

|

|

|

x0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

|

б) |

|

|

|

|

|

|

|

|

|

в) |

|

|

|

|

|

|

|

г) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x1 |

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x0 |

|

|

|

|

|

|

|

x0 |

|

|

|

|

|

|

|

|

x0 |

|

|

|

|

|

|

|

x0 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

y1 |

|

|

|

|

|

|

|

|

y1 |

|

|

|

|

|

|

1 |

|

|

y2 |

|

|

|

|

|

2 |

y2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Рис.8.6. Статический риск сбоя : а - отсутствие риска сбоя в элементе И;

б- наличие риска сбоя в элементе И; в - наличие риска сбоя в элементе ИЛИ;

г- отсутствие риска сбоя в элементе ИЛИ.

Риск сбоя называется статическим, если y(X1) = y(Х2), где y - булева функция. Риск сбоя называется статическим в нуле S0, если y(Х1) = y(Х2) = 0. Риск сбоя называется статическим в единице S1, если y(Х1) = y(Х2) = 1. Итак, на рис.8.6,б имеет место статический риск сбоя в нуле S0, а на рис.8.6,в - статический риск сбоя в единице S1.

Существенно, что полученные помехи S0 и S1 (иногда их называют “иголками”, “мерцаниями”, “глитчами” (англ. glitch)) - это не пренебрежимо короткий всплеск напряжения малой амплитуды. При достаточно большой разности ∆τ помеха будет иметь длительность, во много раз превышающую время переключения элемента, и амплитуду, равную номинальному сигналу. Это уже полноценный сигнал, на который могут реагировать последующие элементы (входы синхронизации, установки в 0 или 1, загрузки данных и т. п.). Такие помехи - страшная вещь для цифровых схем, тем более, что их практически невозможно увидеть на осциллографе, и разработчик просто не будет знать об их существовании. Они могут сужаться до полного исчезновения, но могут и расширяться, проходя через логические цепи.

8.3. Динамические риски сбоя

На рис.8.7,а приведена схема, реализующая функцию y = x2x1 + x0. Пусть входной набор Х1 = x2x1x0 = 010 изменяется на входной набор Х2 = x2x1x0= =101. На рис.8.7,б приведены временные диаграммы,